1、虚拟原型:芯片设计领域的革新利器

芯片设计公司长期面临双重挑战:既要研发高性能芯片方案,又得缩短周期抢先推新。当下,系统与软件的复杂度与日俱增,传统软件开发方法在当下复杂形势中弊端渐显,如介入时间靠后增加了开发周期,难满足行业发展,革新势在必行。“Shift Left”——左移开发理念虽并非新兴概念,但其在当下愈发凸显出重要价值。其核心在于尽早进入软件开发环节,利用虚拟平台等与硬件设计并发进行早期软件开发,也可利用软件将验证和测试工作提前至设计初期。毕竟,设计初期发现并解决问题,成本和时间投入远低于项目后期。借助左移开发,芯片设计公司能更主动地把控质量,降低潜在风险及问题定位成本,提升整体开发效率,从而缩短芯片开发周期。在左移开发理念的推动下,虚拟原型技术崭露头角,为芯片设计和其配套软件的开发带来了全新的思路和方法。

虚拟原型中的虚拟平台提供全系统仿真能力,能够在硬件还不具备的情况下提前进行软件开发。且基于虚拟原型开发的软件可在项目开发的后续阶段直接运行在对应的芯片上,这将大大提高项目的开发效率。且虚拟原型与传统物理原型相比,虚拟平台在可扩展性、易用性、调试手段等方面有先天优势。如物理原型,需要高昂的FPGA、子卡等硬件成本,而且在构建验证环境时耗时费力。而虚拟平台则可以轻松地根据设计需求进行灵活调整和扩展,为开发人员提供了更大的自由度和便利性。但物理原型上运行的是真实的芯片IP设计,在验证精准度、IP复用等方面有虚拟原型不可比拟的优势。虚拟原型考虑到仿真速度等原因,一般在事务级进行建模从而忽略了设计的细节。物理原型仿真的是真实芯片设计,能够精确仿真芯片的运行细节。同时,对于已有IP也可以直接集成到物理原型中,不需要再投入人力对其重新进行建模。混合仿真解决方案将结合虚拟原型仿真速度、左移开发与物理原型在精确度上的优势带来更高效的验证方案。

2、混合仿真:融合物理原型与虚拟原型的前沿技术

混合仿真不仅能够助力实现更早的架构优化与软件开发,还能在关键IP(知识产权核)的寄存器传输级(RTL)验证过程中,通过软件驱动RTL验证实现更高的验证效率。混合仿真解决方案让系统的一部分在硬件原型或硬件仿真器中运行,另一部分在虚拟原型中运行,结合二者的优势,建构混合验证系统。混合仿真具有三个主要应用场景,分别是架构探索、支持早期软件开发以及开展硬件验证。

- 架构探索

在架构探索阶段,需要调整如总线拓扑、内存带宽、cache结构等系统参数,并结合仿真结果找到最优的芯片架构。在这个过程中,仿真的速度和仿真的精确度都至为重要,前者决定了架构探索效率,后者决定了仿真结果是否可信。在使用混合仿真进行架构探索时,可将需要高精确度但运行速度稍慢的部分使用RTL实现,而不关注的部分使用低精度但仿真速度较快的部分使用事务级模型实现,从而兼顾二者优势。如,在对SoC中某个外设的访存带宽进行优化时,可通过事务级的指令仿真器实现CPU指令的执行,通过在指令仿真器中运行二进制触发不同应用场景下外设对内存的访问并进行统计,从而找到瓶颈点和优化方向。

- 早期软件开发

绝大多数情况下,硬件需要配套相应的软件才能正常工作,而在传统开发模式下,软件团队一般需要等待硬件开发验证完成才能投入软件的适配开发和测试;且在大型的芯片开发过程中,各硬件模块的开发进度一般是不同的,导致软件团队需等待最慢的一个硬件模块完成验证才能进行开发,这将拉长整体项目的周期,降低研发效率。因此,通过虚拟平台使能早期软件开发可以成为提升项目整体开发效率的关键举措。同时,随着硬件模块开发的推进,混合仿真可将已开发完成的硬件模块集成到虚拟平台中,使软件团队能尽早得使用实际设计的硬件进行开发、验证。随着开发进度的进行逐步完成虚拟平台中各模块的替代,并最终完全迁移到物理原型中。

- 开展硬件验证

硬件验证是确保芯片设计正确性和可靠性的关键环节。混合仿真允许在实际的软件负载下运行硬件系统,这为硬件验证提供了更加真实和全面的测试环境。通过在实际软件负载下进行验证,开发人员能够更早、更准确地发现硬件设计中存在的问题,如性能瓶颈、兼容性问题等,并及时进行修复和优化,从而提高芯片的质量和可靠性。

3、可扩展的虚拟平台:混合仿真的坚实基石

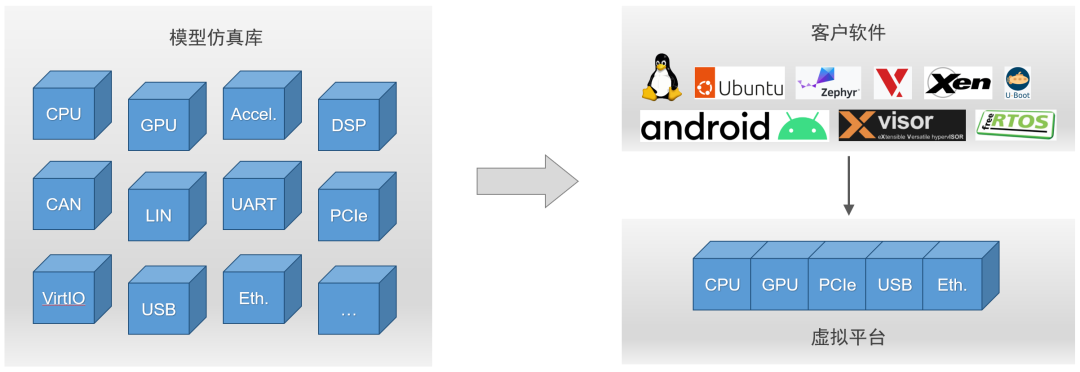

可扩展的虚拟平台是混合仿真得以实现的重要基础。通过提供各种组件,开发人员可根据设计需求,将这些组件像搭积木一样拼接成虚拟原型(VP)。在这个VP之上,可运行多种操作系统或应用程序,如Ubuntu、Android、U - boot、RTOS等,为芯片配套的软件开发和验证提供丰富测试场景。

以思尔芯的Genesis芯神匠Virtual Platform(以下简称 VP)为例,它是一个典型的虚拟原型平台。该平台具备高度可扩展性和灵活性,能满足不同芯片设计项目需求。开发人员可利用Genesis VP提供的丰富组件和工具,以及思尔芯的芯神瞳原型验证平台,快速搭建符合项目要求的虚拟原型,加速芯片设计和开发进程。

4、混合仿真的应用场景

- 场景1:系统早期Bring-up

在芯片尚不可用之前,混合仿真解决方案能提供良好的IP 接入,借助虚拟平台为软件开发创造有利条件。开发的软件同时也作为RTL硬件的验证激励。开发人员可在虚拟平台的CPU上运行开发的软件,作为硬件验证编写的测试模型,通过将暂未完成开发的RTL模块迁移到虚拟平台,可以尽早地构建完整的验证系统并bring-up,从而使能早期软件开发,提升验证效率。

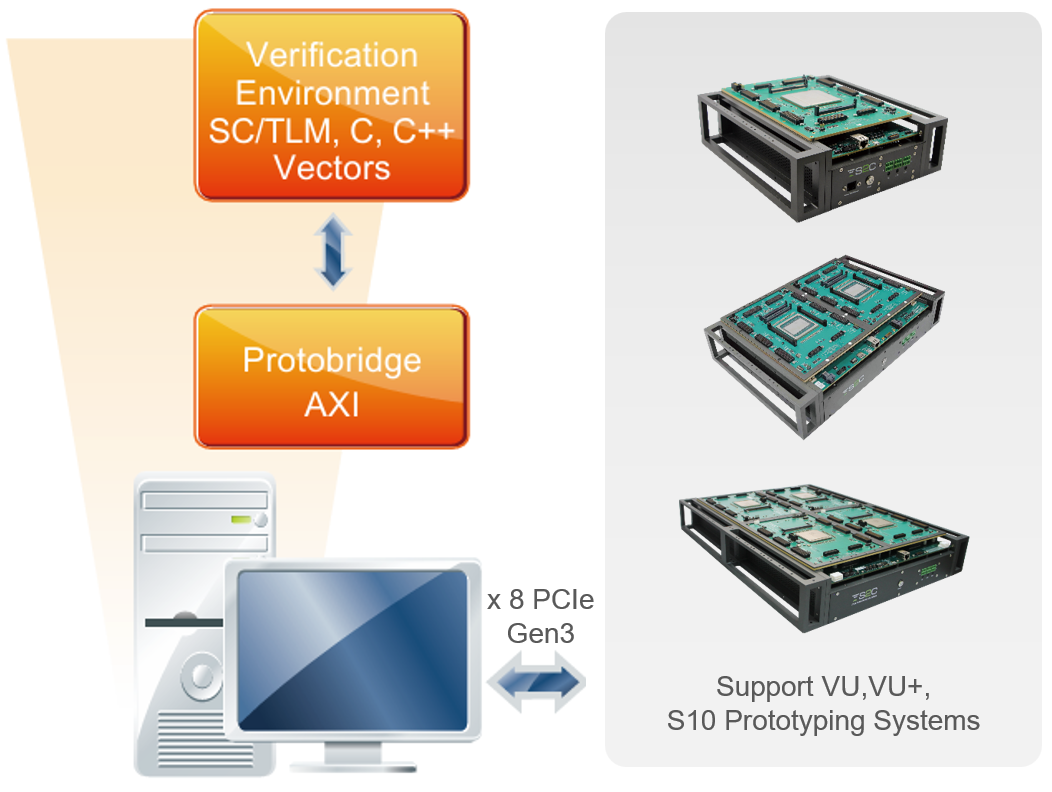

- 场景2: 降低TAT并提高可调试性

虚拟平台有助于提高测试覆盖率、生产力和质量。它具备集成丰富的调试能力,能够让开发人员直观地观察从代码到硬件内部寄存器的运行情况,从而提升测试和问题解决效率。开发人员可以根据应用场景在软件中创建Corner测试,并在思尔芯的芯神瞳原型验证平台上执行,提高生产力。同时,在虚拟原型中构建的用例可作为在原型验证平台上运行的高性能回归测试,进一步确保芯片的质量和性能。

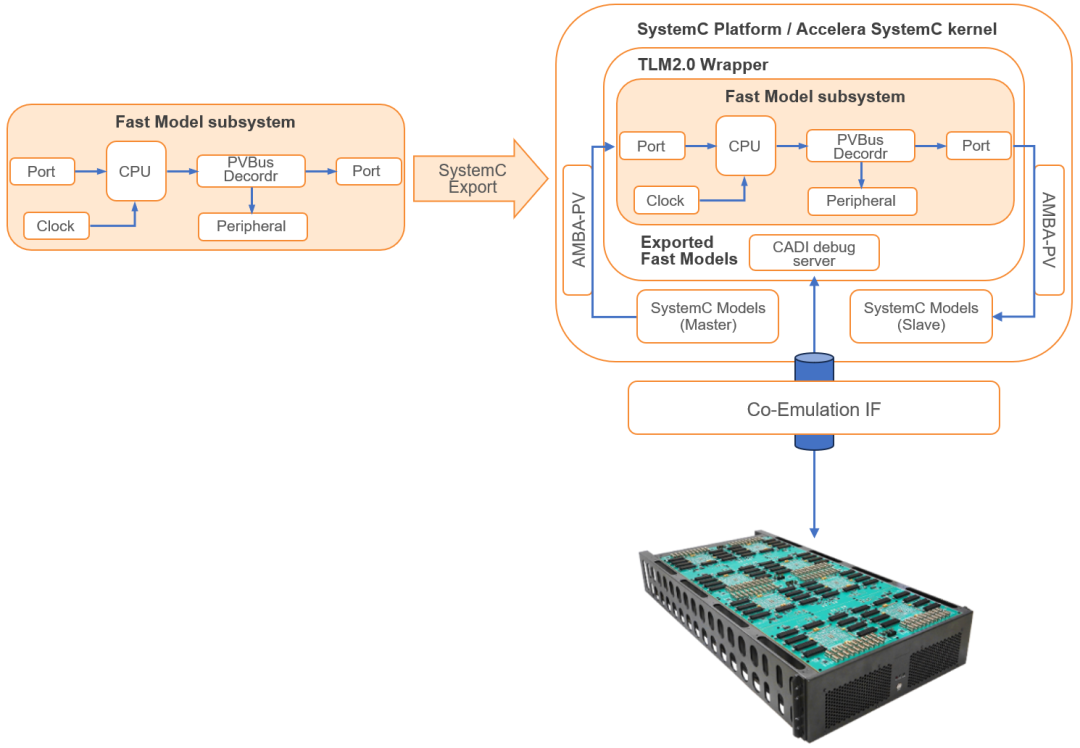

- 场景3: FPGA加速提升整体系统性能

利用虚拟平台和思尔芯的芯神瞳FPGA的混合仿真技术能有效加速仿真时间。对于软件速度表现不佳的组件,可移植到FPGA实施,剩余部分组件则运行在软件上。如:客户先撰写SystemC or C/C++模型,运行整体系统仿真,判断哪些模型是性能瓶颈并可通过FPGA执行提升运行效率,然后通过HLS等方法将这些模型转化到RTL并部署到FPGA再运行仿真,以实现系统仿真性能的提升。

- 场景4: 提高可复用性

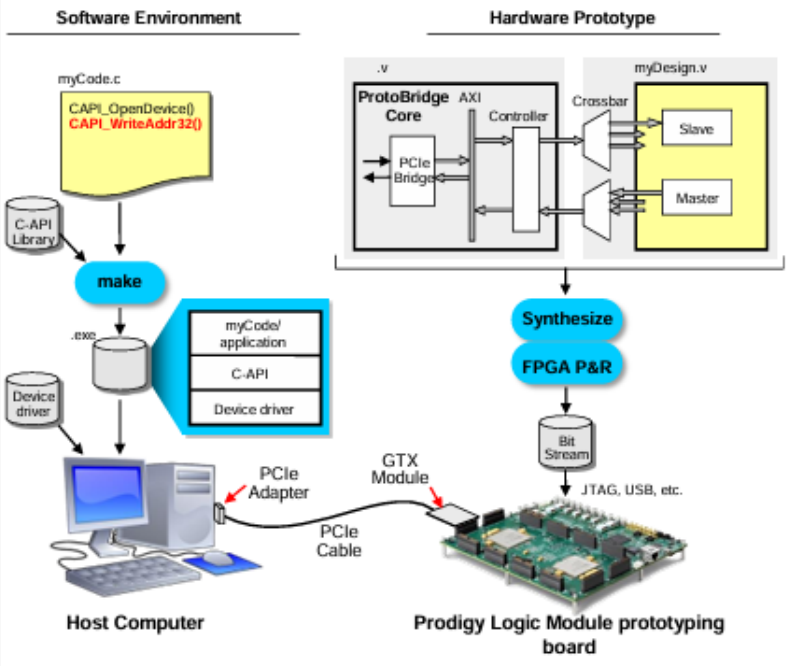

混合仿真系统能充分利用已经存在并完全验证的RTL。在芯片设计中,常常会用到三方IP,或者行为模型SystemC or C/C++尚未准备好的情况;或这些模型虽然可用,但可能具有特定限制,且与 RTL 并不完全等效。此时,重复使用RTL在之前的客户项目中就具有很大优势,不必将其转换为 SystemC模型,而且RTL模型可能已在FPGA中部署,进一步提高开发效率和资源利用率。

5、成功案例 - SW + FPGA开发板

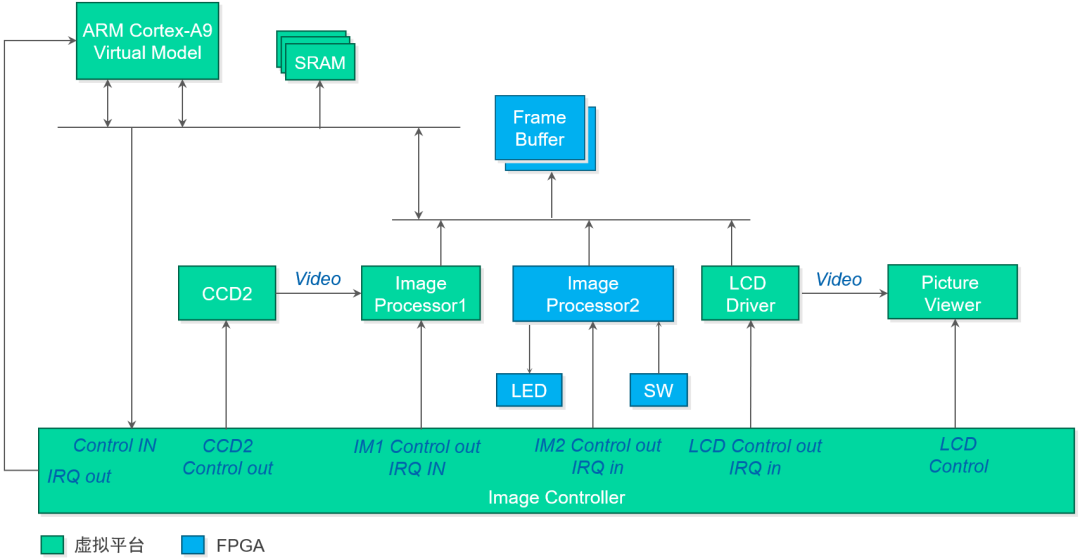

在前面详细阐述虚拟平台丰富应用场景的基础上,下面通过一个SW + FPGA开发板的成功案例,进一步展现虚拟平台在实际项目中的强大效能与独特价值。此案例聚焦于图像处理设计领域。该系统中,CPU扮演核心控制角色,精准调度硬件资源;内存负责存储图片,为图像处理提供数据基础;而图像处理器则需频繁访问内存以获取并处理图像数据。如此复杂且紧密协作的系统架构,对验证工作提出极高要求,也凸显出可扩展虚拟平台应用的必要性。

在图像处理系统的验证工作中,采用将系统一分为二的创新策略。具体而言,把Image Processor 2部署在FPGA中运行,考虑到其需要接收图像数据,在FPGA内部专门设置Frame Buffer(帧缓冲器),用于临时存储图像数据,确保数据能够稳定、有序地传输给Image Processor 2进行处理。系统的其余部分,涵盖CPU以及各类配套的组件模型,则放置在虚拟原型(VP)中。系统运行时,VP会加载外设的驱动程序,精准捕获原始图像,并将其传递至FPGA开展处理工作。值得一提的是,VP中还集成图像显示等功能模块,开发人员可直接观察处理后的图像情况,极大提升调试效率。此外,VP中还能集成通过软件实现的图像处理算法,将其作为Image Processor 1。系统运行后,以Image Processor 1的处理结果作为标准,与FPGA中Image Processor 2的处理数据进行对比,以此验证FPGA处理的正确性。

总结

思尔芯的Genesis芯神匠Virtual Platform虚拟平台凭借其独特的搭建方式和广泛的应用场景,在芯片设计与验证领域发挥着不可替代的作用。它不仅为开发人员提供便捷、高效的开发环境,还为芯片的质量和性能提供有力保障,推动着芯片行业不断向前发展。随着技术的不断进步,虚拟平台有望在更多领域展现其强大魅力,为芯片设计与开发带来更多创新与突破。

-

芯片设计

+关注

关注

15文章

1128浏览量

56454 -

仿真

+关注

关注

53文章

4407浏览量

137672 -

思尔芯

+关注

关注

0文章

143浏览量

1680

发布评论请先 登录

思尔芯原型验证系统助力昆明湖V2成功启动GUI OpenEuler

“芯”启杭 创未来 | 匠芯创杭州办事处盛大开业

【匠芯创D133CBS KunLun Pi开发板试用体验】开箱评测

创“芯”舞台!思尔芯邀您挑战2025 EDA精英赛

产学研融合!思尔芯数字EDA工具走进北航课堂

芯来科技携手芯芒科技发布RISC-V CPU系统仿真平台

预告|思尔芯邀您共聚2025玄铁RISC-V生态大会

解锁思尔芯Genesis芯神匠虚拟原型平台:混合仿真与多元应用实践

解锁思尔芯Genesis芯神匠虚拟原型平台:混合仿真与多元应用实践

评论