声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

dsp

+关注

关注

559文章

8214浏览量

363834 -

FPGA

+关注

关注

1655文章

22281浏览量

630051 -

Xilinx

+关注

关注

73文章

2192浏览量

129880

发布评论请先 登录

相关推荐

热点推荐

基于DSP与FPGA异构架构的高性能伺服控制系统设计

DSP+FPGA架构在伺服控制模块中的应用,成功解决了高性能伺服系统对实时性、精度和复杂度的多重需求。通过合理的功能划分,DSP专注于复杂算法和上层控制,FPGA处理高速硬件任务,两者协同实现了传统架构难以达到的性能指标。

DSP的基础

高速数字信号处理技术是以DSP为核心,具有高速,实时的特点的一种信息处理技术。其本质是信息的变换和提取。DSP(Digital Signal Processor),即数字信号处理器,是一种专用

发表于 11-20 06:35

DSP、FPGA之间SRIO通信的问题?

目前在使用DSP和FPGA之间通过SRIO的SWRITE事务完成双向数据通信,大多数情况下都正常,但是在我不停的给DSP进行烧写程序时,会偶尔出错,FPGA无法收到

发表于 11-15 16:22

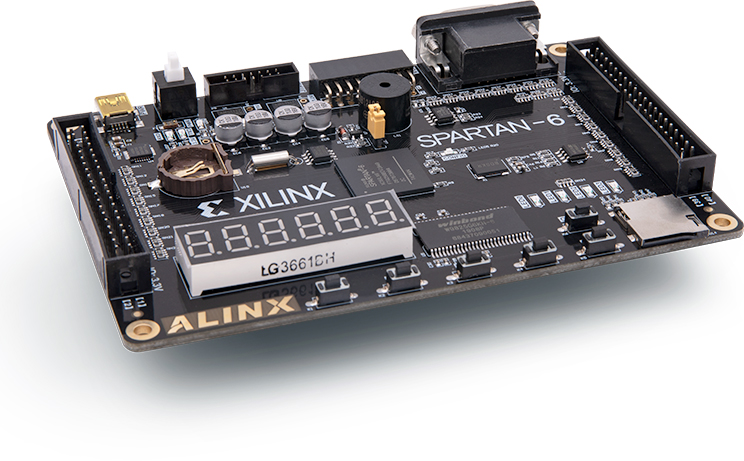

如何利用Verilog HDL在FPGA上实现SRAM的读写测试

本篇将详细介绍如何利用Verilog HDL在FPGA上实现SRAM的读写测试。SRAM是一种非易失性存储器,具有高速读取和写入的特点。在FPGA中实现SRAM读写测试,包括设计SRAM接口模块

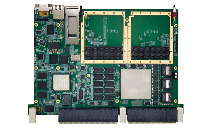

【 VPX638】青翼凌云科技基于KU115 FPGA+C6678 DSP的6U VPX双FMC接口通用信号处理平台

VPX638是一款基于KU115 FPGA + C6678 DSP的6U VPX双FMC接口通用信号处理平台,该平台采用一片Xilinx的Kintex UltraScale系列FPGA

FPGA利用DMA IP核实现ADC数据采集

本文介绍如何利用FPGA和DMA技术处理来自AD9280和AD9708 ADC的数据。首先,探讨了这两种ADC的特点及其与FPGA的接口兼容性。接着,详细说明了使用Xilinx VIVADO环境下

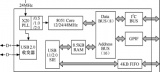

中科亿海微SoM模组——FPGA+DSP核心板

FPGA+DSP核心板是基于中科亿海微EQ6HL130型FPGA芯片搭配国产DSP开发的高性能核心板卡。对外接口采取邮票孔连接方式,可以极大提高信号传输质量和焊接后的机械强度。核心板卡的系统框图如下

适用于Versal的AMD Vivado 加快FPGA开发完成Versal自适应SoC设计

设计、编译、交付,轻松搞定。更快更高效。 Vivado 设计套件提供经过优化的设计流程,让传统 FPGA 开发人员能够加快完成 Versal 自适应 SoC 设计。 面向硬件开发人员的精简设计流程

智多晶FIFO_Generator IP介绍

FIFO_Generator是智多晶设计的一款通用型FIFO IP。当前发布的FIFO_Generator IP是2.0版本,相比之前的1.1版本主要新增了非等比输入输出数据位宽支持和异步FIFO跨时钟级数配置功能。

EE-191:利用SHARC DSP SPORTs实现无缝UART

电子发烧友网站提供《EE-191:利用SHARC DSP SPORTs实现无缝UART.pdf》资料免费下载

发表于 01-06 14:40

•0次下载

利用FPGA实现USB 2.0通信接口

USB 2.0接口的实现方式 利用FPGA来实现USB 2.0接口的方式一般有两种,一是借助外围的USB接口芯片,二是FPGA内部实现USB协议控制器,外部通过USB的PHY芯片来实现接口。 对于

当DSP与FPGA通讯的时候,XZCS0、XZCS6、XZCS7会影响ADS8556的工作吗?

您好,我想用3个ads8556和1个FPGA都通过TMS320F28335的XINTF接口与DSP相连,3个ads8556占用了XZCS0、XZCS6、XZCS7三个片选信号,DSP只对AD读数

发表于 12-20 07:30

利用 AccelDSP 和 System Generator for DSP™ 加快 FPGA 设计

利用 AccelDSP 和 System Generator for DSP™ 加快 FPGA 设计

评论