单芯片解决方案,开启全新体验——W55MH32 高性能以太网单片机

W55MH32是WIZnet重磅推出的高性能以太网单片机,它为用户带来前所未有的集成化体验。这颗芯片将强大的组件集于一身,具体来说,一颗W55MH32内置高性能Arm® Cortex-M3核心,其主频最高可达216MHz;配备1024KB FLASH与96KB SRAM,满足存储与数据处理需求;集成TOE引擎,包含WIZnet全硬件TCP/IP协议栈、内置MAC以及PHY,拥有独立的32KB以太网收发缓存,可供8个独立硬件socket使用。如此配置,真正实现了All-in-One解决方案,为开发者提供极大便利。

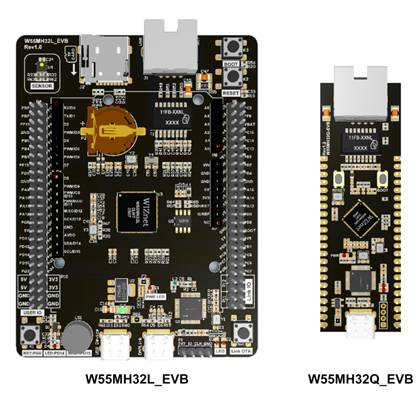

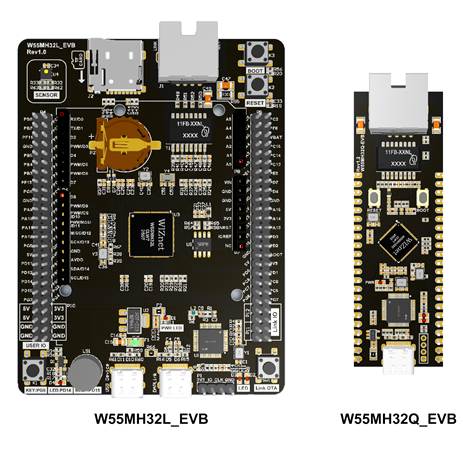

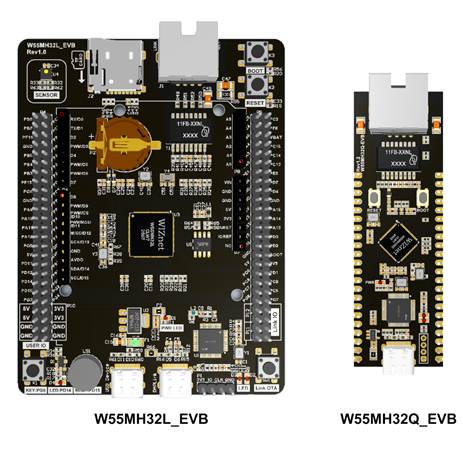

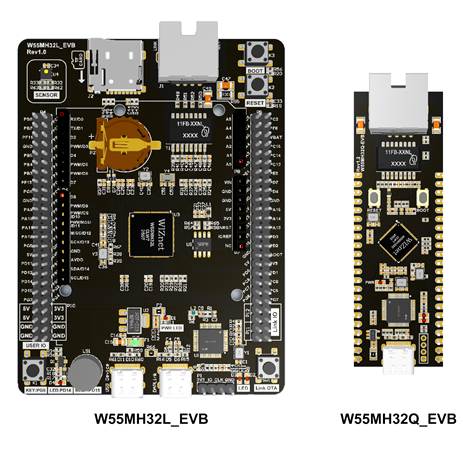

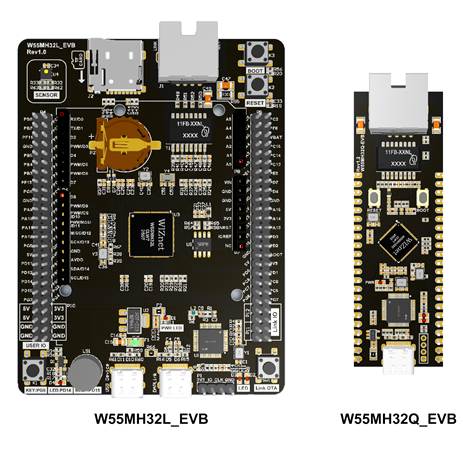

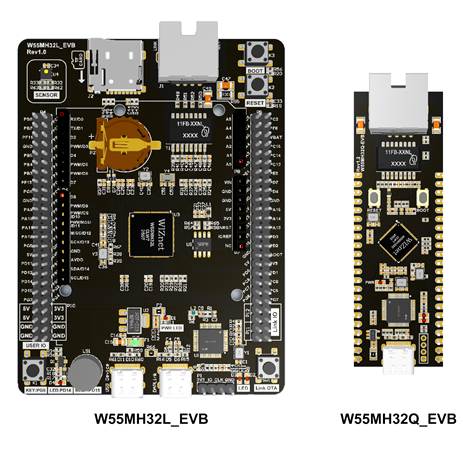

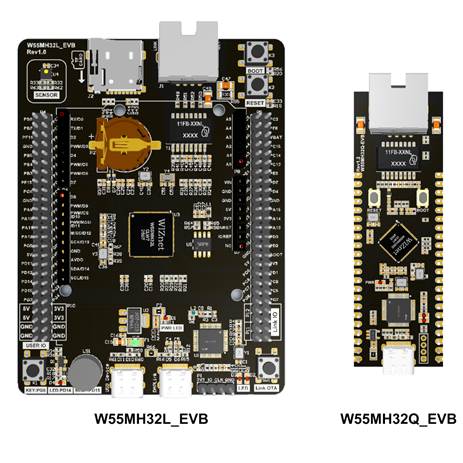

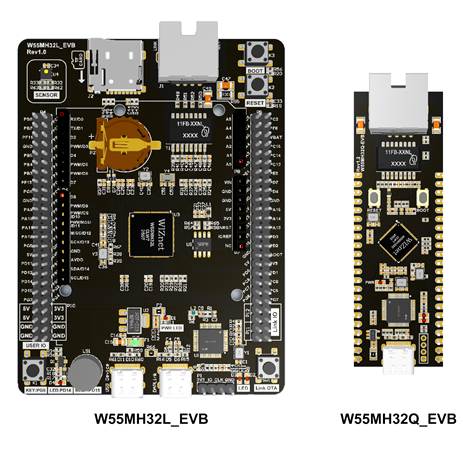

在封装规格上,W55MH32 提供了两种选择:QFN100和QFN68。

W55MH32L采用QFN100封装版本,尺寸为12x12mm,其资源丰富,专为各种复杂工控场景设计。它拥有66个GPIO、3个ADC、12通道DMA、17个定时器、2个I2C、5个串口、2个SPI接口(其中1个带I2S接口复用)、1个CAN、1个USB2.0以及1个SDIO接口。如此丰富的外设资源,能够轻松应对工业控制中多样化的连接需求,无论是与各类传感器、执行器的通信,还是对复杂工业协议的支持,都能游刃有余,成为复杂工控领域的理想选择。 同系列还有QFN68封装的W55MH32Q版本,该版本体积更小,仅为8x8mm,成本低,适合集成度高的网关模组等场景,软件使用方法一致。更多信息和资料请进入http://www.w5500.com/网站或者私信获取。

此外,本W55MH32支持硬件加密算法单元,WIZnet还推出TOE+SSL应用,涵盖TCP SSL、HTTP SSL以及 MQTT SSL等,为网络通信安全再添保障。

为助力开发者快速上手与深入开发,基于W55MH32L这颗芯片,WIZnet精心打造了配套开发板。开发板集成WIZ-Link芯片,借助一根USB C口数据线,就能轻松实现调试、下载以及串口打印日志等功能。开发板将所有外设全部引出,拓展功能也大幅提升,便于开发者全面评估芯片性能。

若您想获取芯片和开发板的更多详细信息,包括产品特性、技术参数以及价格等,欢迎访问官方网页:http://www.w5500.com/,我们期待与您共同探索W55MH32的无限可能。

第十章 W55MH32中断应用概览

本章参考资料《W55MH32-参考手册》、《 Cortex-M3内核编程手册》-4.3 章节:NVIC和4.4章节:SCB—4.4.5的AIRCR。

W55MH32中断非常强大,每个外设都可以产生中断,所以中断的讲解放在哪一个外设里面去讲都不合适,这里单独抽出一章来做一个总结性的介绍,这样在其他章节涉及到中断部分的知识我们就不用费很大的篇幅去讲解,只要示意性带过即可。

1 异常类型

W55MH32在内核水平上搭载了一个异常响应系统, 支持为数众多的系统异常和外部中断。 其中系统异常有8个(如果把Reset和HardFault也算上的话就是10个), 外部中断有60个。除了个别异常的优先级被定死外,其它异常的优先级都是可编程的。 有关具体的系统异常和外部中断可在标准库文件w55mh32.h这个头文件查询到,在IRQn_Type这个结构体里面包含了W55MH32系列全部的异常声明。

W55MH32系统异常清单

| 编号 | 优先级 | 优先级类型 | 名称 | 说明 | 地址 |

| - | - | - | 保留(实际存的是 MSP 地址) | 0X0000 0000 | |

| -3 | - | 固定 | Reset | 复位 | 0X0000 0004 |

| -2 | - | 固定 | NMI | 不可屏蔽中断。RCC 时钟安全系统 (CSS) 连接到 NMI 向量 | 0X0000 0008 |

| -1 | - | 固定 | HardFault | 所有类型的错误 | 0X0000 000C |

| 0 | - | 可编程 | MemManage | 存储器管理 | 0X0000 0010 |

| 1 | - | 可编程 | BusFault | 预取指失败,存储器访问失败 | 0X0000 0014 |

| 2 | - | 可编程 | UsageFault | 未定义的指令或非法状态 | 0X0000 0018 |

| - | - | - | 保留 | 0X0000 001C-0X0000 002B | |

| 3 | - | 可编程 | SVCall | 通过 SWI 指令调用的系统服务 | 0X0000 002C |

| 4 | - | 可编程 | Debug Monitor | 调试监控器 | 0X0000 0030 |

| - | - | - | 保留 | 0X0000 0034 | |

| 5 | - | 可编程 | PendSV | 可挂起的系统服务 | 0X0000 0038 |

| 6 | - | 可编程 | SysTick | 系统嘀嗒定时器 | 0X0000 003C |

W55MH32外部中断清单

| 编号 | 优先级 | 优先级类型 | 名称 | 说明 | 地址 |

| 0 | 7 | 可编程 | WWDG | 窗口看门狗中断 | 0X0000 0040 |

| 1 | 8 | 可编程 | PVD | 连到 EXTI 的电源电压检测 (PVD) 中断 | 0X0000 0044 |

| 2 | 9 | 可编程 | TAMPER | 侵入检测中断 | 0X0000 0048 |

| 57 | 64 | 可编程 | DMA2 通道 2 | DMA2 通道 2 中断 | 0X0000 0124 |

| 58 | 65 | 可编程 | DMA2 通道 3 | DMA2 通道 3z 中断 | 0X0000 0128 |

| 59 | 66 | 可编程 | DMA2 通道 4_5 | DMA2 通道 4 和通道 5 中断 | 0X0000 012C |

2 NVIC简介

在讲如何配置中断优先级之前,我们需要先了解下NVIC。NVIC是嵌套向量中断控制器,控制着整个芯片中断相关的功能,它跟内核紧密耦合,是内核里面的一个外设。但是各个芯片厂商在设计芯片的时候会对Cortex-M3内核里面的NVIC进行裁剪,把不需要的部分去掉,所以说W55MH32的NVIC是Cortex-M 3的NVIC的一个子集。

2.1 NVIC寄存器简介

在固件库中,NVIC的结构体定义可谓是颇有远虑,给每个寄存器都预留了很多位,恐怕为的是日后扩展功能。 不过W55MH32可用不了这么多,只是用了部分而已,具体使用了多少可参考《 Cortex-M3 内核编程手册》-4.3.11:NVIC寄存器映射。

代码清单:中断-1 NVIC结构体定义,来自固件库头文件:core_cm3.h

typedef struct {

__IO uint32_t ISER[8]; // 中断使能寄存器

uint32_t RESERVED0[24];

__IO uint32_t ICER[8]; // 中断清除寄存器

uint32_t RSERVED1[24];

__IO uint32_t ISPR[8]; // 中断使能悬起寄存器

uint32_t RESERVED2[24];

__IO uint32_t ICPR[8]; // 中断清除悬起寄存器

uint32_t RESERVED3[24];

__IO uint32_t IABR[8]; // 中断有效位寄存器

uint32_t RESERVED4[56];

__IO uint8_t IP[240]; // 中断优先级寄存器(8Bit wide)

uint32_t RESERVED5[644];

__O uint32_t STIR; // 软件触发中断寄存器

} NVIC_Type;

在配置中断的时候我们一般只用ISER、ICER和IP这三个寄存器,ISER用来使能中断,ICER用来失能中断,IP用来设置中断优先级。

2.2 NVIC 中断配置固件库

固件库文件core_cm3.h的最后,还提供了NVIC的一些函数,这些函数遵循CMSIS规则,只要是Cortex-M3 的处理器都可以使用,具体如下:

| NVIC 库函数 | 描述 |

| void NVIC_EnableIRQ(IRQn_Type IRQn) | 使能中断 |

| void NVIC_DisableIRQ(IRQn_Type IRQn) | 失能中断 |

| void NVIC_SetPendingIRQ(IRQn_Type IRQn) | 设置中断悬起位 |

| void NVIC_ClearPendingIRQ(IRQn_Type IRQn) | 清除中断悬起位 |

| uint32_t NVIC_GetPendingIRQ(IRQn_Type IRQn) | 获取悬起中断编号 |

| void NVIC_SetPriority(IRQn_Type IRQn, uint32_t priority) | 设置中断优先级 |

| uint32_t NVIC_GetPriority(IRQn_Type IRQn) | 获取中断优先级 |

| void NVIC_SystemReset(void) | 系统复位 |

这些库函数我们在编程的时候用的都比较少,甚至基本都不用。在配置中断的时候我们还有更简洁的方法,请看中断编程小节。

3 优先级的定义

3.1 优先级定义

在NVIC 有一个专门的寄存器:中断优先级寄存器NVIC_IPRx,用来配置外部中断的优先级,IPR宽度为8bit, 原则上每个外部中断可配置的优先级为0~255,数值越小,优先级越高。但是绝大多数CM3芯片都会精简设计, 以致实际上支持的优先级数减少,在W55MH32中,只使用了高4bit,如下所示:

| bit7 | bit6 | bit5 | bit4 | bit3 | bit2 | bit1 | bit0 |

| 用于表达优先级 | 未使用,读回为 0 | ||||||

用于表达优先级的这4bit,又被分组成抢占优先级和子优先级。如果有多个中断同时响应,抢占优先级高的就会抢占抢占优先级低的优先得到执行, 如果抢占优先级相同,就比较子优先级。如果抢占优先级和子优先级都相同的话,就比较他们的硬件中断编号,编号越小,优先级越高。

3.2 优先级分组

优先级的分组由内核外设SCB的应用程序中断及复位控制寄存器AIRCR的PRIGROUP[10:8]位决定,W55MH32分为了5组,具体如下:主优先级=抢占优先级

| PRIGROUP[2:0] | 中断优先级值 PRI_N [7:4](二进制点) | 主优先级位 | 子优先级位 | 主优先级 | 子优先级 |

| 0b 011 | 0b xxxx | [7:4] | None | 16 | None |

| 0b 100 | 0b xxx.y | [7:5] | [4] | 8 | 2 |

| 0b 101 | 0b xx.yy | [7:6] | [5:4] | 4 | 4 |

| 0b 110 | 0b x.yyy | [7] | [6:4] | 2 | 9 |

| 0b 111 | 0b .yyyy | None | [7:4] | None | 16 |

设置优先级分组可调用库函数NVIC_PriorityGroupConfig()实现,有关NVIC中断相关的库函数都在库文件misc.c和misc.h中。

代码清单:中断-2 中断优先级分组库函数NVIC_PriorityGroupConfig()

/**

* 配置中断优先级分组:抢占优先级和子优先级

* 形参如下:

* @arg NVIC_PriorityGroup_0: 0bit for抢占优先级

* 4 bits for 子优先级

* @arg NVIC_PriorityGroup_1: 1 bit for抢占优先级

* 3 bits for 子优先级

* @arg NVIC_PriorityGroup_2: 2 bit for抢占优先级

* 2 bits for 子优先级

* @arg NVIC_PriorityGroup_3: 3 bit for抢占优先级

* 1 bits for 子优先级

* @arg NVIC_PriorityGroup_4: 4 bit for抢占优先级

* 0 bits for 子优先级

* @注意 如果优先级分组为0,则抢占优先级就不存在,优先级就全部由子优先级控制

*/

void NVIC_PriorityGroupConfig(uint32_t NVIC_PriorityGroup)

{

// 设置优先级分组

SCB->AIRCR = AIRCR_VECTKEY_MASK | NVIC_PriorityGroup;

}

| 优先级分组 | 主优先级 | 子优先级 | 描述 |

| NVIC_PriorityGroup_0 | 0 | 0-15 | 主 - 0bit,子 - 4bit |

| NVIC_PriorityGroup_1 | 0-1 | 0-7 | 主 - 1bit,子 - 3bit |

| NVIC_PriorityGroup_2 | 0-3 | 0-3 | 主 - 2bit,子 - 2bit |

| NVIC_PriorityGroup_3 | 0-7 | 0-1 | 主 - 3bit,子 - 1bit |

| NVIC_PriorityGroup_4 | 0-15 | 0 | 主 - 4bit,子 - 0bit |

4 中断编程

在配置每个中断的时候一般有3个编程要点:

1.使能外设某个中断,这个具体由每个外设的相关中断使能位控制。比如串口有发送完成中断,接收完成中断,这两个中断都由串口控制寄存器的相关中断使能位控制。

2.初始化NVIC_InitTypeDef结构体,配置中断优先级分组,设置抢占优先级和子优先级, 使能中断请求。NVIC_InitTypeDef结构体在固件库头文件misc.h中定义。

代码清单:中断-3 NVIC初始化结构体

typedef struct {

uint8_t NVIC_IRQChannel; // 中断源

uint8_t NVIC_IRQChannelPreemptionPriority; // 抢占优先级

uint8_t NVIC_IRQChannelSubPriority; // 子优先级

FunctionalState NVIC_IRQChannelCmd; // 中断使能或者失能

} NVIC_InitTypeDef;

有关NVIC初始化结构体的成员我们一一解释下:

(1).NVIC_IROChannel:用来设置中断源,不同的中断中断源不一样,且不可写错,即使写错了程序也不会报错,只会导致不响应中断。 具体的成员配置可参考w55mh32x.h头文件里面的IRQn_Type结构体定义,这个结构体包含了所有的中断源。

代码清单:中断-4 IRQn_Type中断源结构体

typedef enum IRQn {

//Cortex-M3 处理器异常编号

NonMaskableInt_IRQn = -14,

MemoryManagement_IRQn = -12,

BusFault_IRQn = -11,

UsageFault_IRQn = -10,

SVCall_IRQn = -5,

DebugMonitor_IRQn = -4,

PendSV_IRQn = -2,

SysTick_IRQn = -1,

/W55MH32 外部中断编号

WWDG_IRQn = 0,

PVD_IRQn = 1,

TAMP_STAMP_IRQn = 2,

// 限于篇幅,中间部分代码省略,具体的可查看库文件W55MH32.h

DMA2_Channel2_IRQn = 57,

DMA2_Channel3_IRQn = 58,

DMA2_Channel4_5_IRQn = 59

} IRQn_Type;

(2).NVIC_IRQChannelPreemptionPriority:抢占优先级,具体的值要根据优先级分组来确定, 具体参考表格 优先级分组真值表 优先级分组真值表 。

(3). NVIC_IRQChannelSubPriority:子优先级,具体的值要根据优先级分组来确定, 具体参考表格 优先级分组真值表 优先级分组真值表 。

(4).NVIC_IRQChannelCmd:中断使能(ENABLE)或者失能(DISABLE)。 操作的是NVIC_ISER和NVIC_ICER这两个寄存器。

3.编写中断服务函数

在启动文件startup_w55mh32_hd.s中我们预先为每个中断都写了一个中断服务函数,只是这些中断函数都是为空,为的只是初始化中断向量表。 实际的中断服务函数都需要我们重新编写,为了方便管理我们把中断服务函数统一写在w55mh32_it.c这个库文件中。

关于中断服务函数的函数名必须跟启动文件里面预先设置的一样,如果写错,系统就在中断向量表中找不到中断服务函数的入口, 直接跳转到启动文件里面预先写好的空函数,并且在里面无限循环,实现不了中断。

5 补充说明

后续其他例程的某个外设配置过程的自定义函数如NVIC_Configuration()分别执行了 NVIC_PriorityGroupConfig() 配置中断优先级分组,NVIC_Init(&NVIC_InitStructure) 配置结构体赋值的将要设置的中断向量和其优先级, 注意这里的 NVIC_PriorityGroupConfig是整个程序中只需要设置一次 。

当设置好了中断优先级分组,其他各种外设对应的中断向量的中断优先级既是基于目前设置分组来解读, 假设配置为NVIC_PriorityGroup_0或者NVIC_PriorityGroup_4,那么给多个外设分别填充NVIC_InitStructure的子优先级或主优先级是无效的,所以说如果工程里面有用到许多的外设中断,那么在确定了想用哪一种优先级分组后再给每个外设对应的中断向量配置优先级。

在其他例程中很多将NVIC_PriorityGroupConfig写在了每个外设自己的中断配置函数里面,有些可能多个外设配置函数下重复了NVIC_PriorityGroupConfig()这句, 这里提醒用户后续编写自己程序时只需要调用一次即可,若重复调用相当于对中断相关寄存器重复赋值多次取最后一次赋值,并且从代码布局逻辑来说,NVIC_PriorityGroupConfig适合放在main()函数中。

WIZnet 是一家无晶圆厂半导体公司,成立于 1998 年。产品包括互联网处理器 iMCU™,它采用 TOE(TCP/IP 卸载引擎)技术,基于独特的专利全硬连线 TCP/IP。iMCU™ 面向各种应用中的嵌入式互联网设备。

WIZnet 在全球拥有 70 多家分销商,在香港、韩国、美国设有办事处,提供技术支持和产品营销。

香港办事处管理的区域包括:澳大利亚、印度、土耳其、亚洲(韩国和日本除外)。

审核编辑 黄宇

-

芯片

+关注

关注

463文章

54458浏览量

469515 -

封装

+关注

关注

128文章

9337浏览量

149057 -

WIZnet

+关注

关注

3文章

20浏览量

42906

发布评论请先 登录

【PDF】C++ GUI Programming with Qt 4 中文版(第一章至第十章)目录版

《从算法设计到硬线逻辑的实现》中第十章练习6-在Verilog H...

明德扬视频分享点拨FPGA课程--第十章 GVIM的使用

第二章 W55MH32 DHCP示例

第五章 W55MH32 UDP示例

第九章 W55MH32 HTTP Server示例

第十章 W55MH32 SNTP示例

第十四章 W55MH32 TFTP示例

第十五章 W55MH32 SNMP示例

第十六章 W55MH32 PING示例

第三十章 W55MH32 HTTP_Server&NetBIOS示例

第十章 W55MH32中断应用概览

第十章 W55MH32中断应用概览

评论