概述

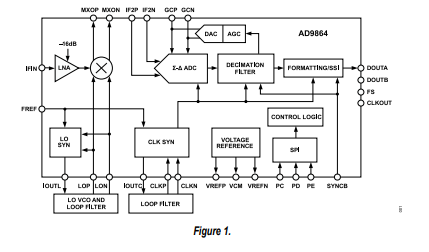

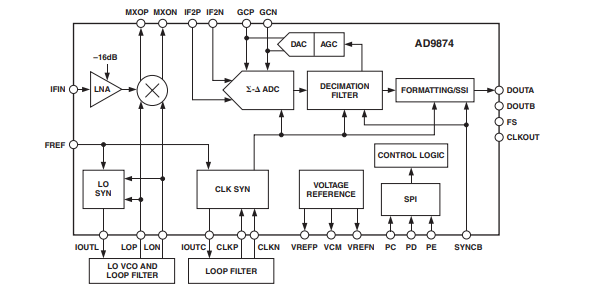

AD9864是一款通用中频子系统,可对信号带宽范围为6.8 kHz至270 kHz的低电平10 MHz至300 MHz中频输入进行数字化处理。AD9864的信号链包括一个低噪声放大器(LNA)、一个混频器、一个带通Σ-Δ型模数转换器(ADC)以及一个具有可编程抽取系数的抽取滤波器。自动增益控制(AGC)电路提供12 dB的连续增益调整。辅助模块包括时钟和LO频率合成器。

AD9864的高动态范围和带通Σ-Δ型转换器内在的抗混叠功能,使该器件能处理比目标信号强度高达95 dB的阻塞信号。此特性可以降低中频滤波要求,从而降低无线电的成本,而且还支持不同通道带宽的多模无线电,使中频滤波器具有较大的额定通道带宽。

通过SPI®端口可对AD9864的许多参数进行编程,因此该器件可针对特定应用进行优化。可编程参数包括:频率合成器分频比、AGC衰减和上升/延迟时间、接收信号强度水平、抽取系数、输出数据格式、16 dB衰减器以及所选的偏置电流。

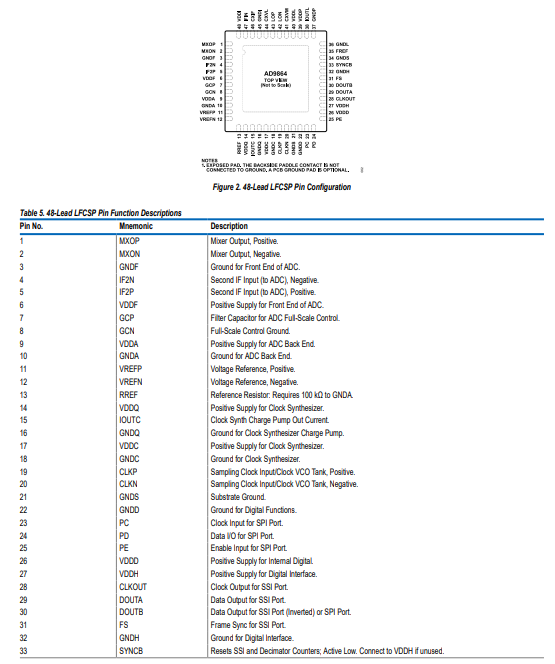

AD9864采用48引脚LFCSP封装,以2.7 V至3.6 V单电源供电。总功耗典型值为56 mW,可通过串行接口实现省电模式。

数据表:*附件:AD9864中频数字化子系统技术手册.pdf

应用

特性

- 输入频率:10 MHz至300 MHz

- 复合输出信号带宽:6.8 kHz至270 kHz

- 单边带噪声系数(SSB NF):7.5 dB

- 输入三阶交调截点(IIP3):−7.0 dBm

- 无AGC范围最高达−34 dBm

- 连续AGC范围:12 dB

- 前端衰减器:16 dB

- 基带I/Q 16位(或24位)串行数字输出

- LO和采样时钟频率合成器

- 可编程抽取系数、输出格式、AGC和频率合成器设置

- 370 Ω输入阻抗

- 电源电压:2.7 V至3.6 V

- 低功耗: 17 mA

- 48引脚LFCSP封装

框图

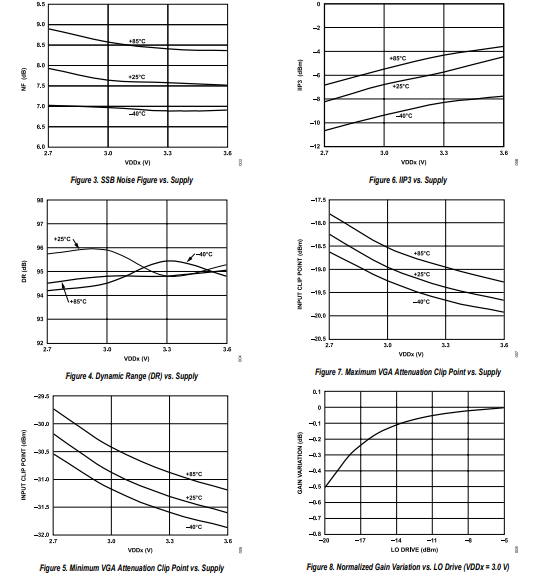

引脚配置描述

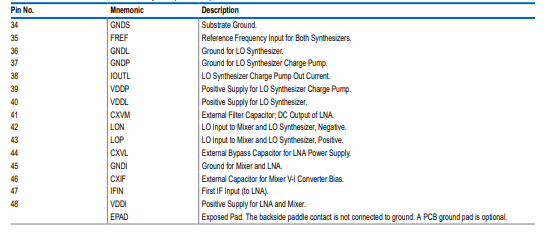

典型性能特征

上电复位

当VDD电源电压超过阈值时,SPI寄存器会自动设置为默认值。这确保了AD9864处于已知状态,并在最小电源功耗下稳定运行。SPI寄存器无需写入其默认设置,这等同于通过软件复位将0x09发送到SFR。0xF00可作为第一个SPI写命令,提供额外保障。

同步串行接口(SSI)

AD9864为其SSI输出数据格式、编程模式及其与帧同步信号(FS)、时钟(SCLK)的定时关系提供了高度灵活性。AD9864提供三线制数字接口,用于与主机设备进行通信。在四线制模式下,帧同步信息被嵌入到数据流中,因此同时提供SCLK和DOUTA信号给主机设备。SSI控制寄存器(SSICR)和SSICR2中的表6到表13展示了与这些寄存器相关的位字段。

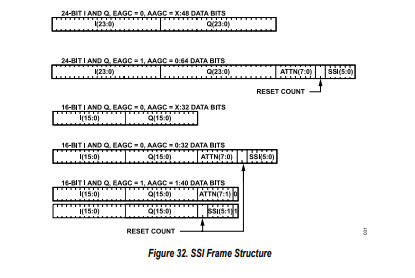

AD9864的主要输出是在帧内解调的同相(I)和正交(Q)信号流。SSI输出端口有一个单比特流,其数据速率等于ADC采样速率除以抽取因子。该比特流在解复用寄存器(0x007)中进行编程。数据由一个Q字组成,其中每个字可以是24位或16位长,并且总是先发送最高有效位。可选字节也可包含在Q字之后的SSI帧中。每个SSI帧由一个或多个Q字组成,Q字计数用于调制残余误差并估计接收信号幅度(相对于AD9864的满量程)。图32说明了SSI数据帧中的样本关系。

如果SSICR1中的EAGC位被置位,会输出两个可选字节。第一个字节是 - 6 dB衰减设置(0 = 无衰减,255 = 24 dB衰减),而第二个字节包含24比特的接收信号强度指示(RSSI)值,其中RSSI的前8位是整数部分,后16位是小数部分。在第一个再生阶段,信号强度与输出的满量程成比例。

两个可选字节跟随16比特的I和Q数据。如果EAGC位被置位,这两个字节遵循I和Q数据的交替模式。在交替模式下,I数据中的整数部分是包含RSSI信息字节的最高有效位,而小数部分是该字节的最低有效位。

在双线接口中,嵌入的帧同步(EFS)在第一个字节的第1位设置。在四线接口中,EFS在嵌入式帧中,该帧由一个起始位(低电平)和一个停止位(高电平)包围,每个帧端至少有10个高电平位。FS保持低电平或三态(默认),以防止帧同步位(SFS)翻转。其他位可用于反转SFS的状态。延迟控制帧同步脉冲一个时钟周期(DLFS),以确保时钟信号不干扰SFS。注意,如果EFS设置为1,SFS不能被位时钟(SCLK)翻转。

辅助寄存器可将输出比特率(fSSI_OUT)设置为输入采样时钟频率(fCLK_IN)或其整数分频。注意,fSSI_OUT等于fCLK_IN除以解复用寄存器中设置的抽取因子。它应该足够高,以避免混叠,且不会损坏输出比特流中的数据。用户通常选择输出比特率,使一个SSI帧适合所选字长和抽取因子。使用高电平位来填充每个字节。

-

子系统

+关注

关注

0文章

116浏览量

13570 -

中频

+关注

关注

0文章

52浏览量

22739 -

ad9864

+关注

关注

0文章

4浏览量

1951

发布评论请先 登录

用SPI给AD9864配置后无法产生时钟信号

请问中频子系统芯片AD9864如何根据芯片SSI接口输出的ATT和RSSI数值?

AD9864,pdf datasheet (IF Digit

发射机中频数字化的设计与实现

基于软件无线电的短波通信中频数字化

中频数字化正交解调结构介绍

AD6644做中频数字处理模块及接口的设计

AD9864 中频数字化子系统

AD9874低功耗中频数字化子系统技术手册

AD9864中频数字化子系统技术手册

AD9864中频数字化子系统技术手册

评论