概述

AD809可以从19.44 MHz或9.72 MHz TTL/CMOS/ECL/PECL基准频率产生155.52 MHz ECL/PECL输出时钟。它支持分布式时序架构,能够将背板或PCB的19.44 MHz或9.72 MHz时序基准信号分配给多个155.52 Mbps端口。该器件可用来为一个或多个端口创建发送位时钟。

输入信号多路复用器支持环路定时应用,可从155.52 Mbps接收数据恢复155.52 MHz发送位时钟。

低抖动VCO、低功耗和宽工作温度范围,使该器件适合在环路系统中为SONET/SDH/光纤产生155.52 MHz位时钟。

该器件内置一个低成本、片内VCO,在输入频率为19.44 MHz或9.72 MHz时,可锁定至该频率的8倍或16倍。无需外部器件便可进行频率合成。不过,用户可以通过选择阻尼因子电容来调整环路动态特性,环路阻尼由阻尼因子电容的值决定。

AD809的设计可保证在输入端无信号时,时钟输出频率的漂移很低(约20%)。

AD809采用+5 V或-5.2 V单电源供电,功耗为90 mW。

数据表:*附件:AD809 155MHz频率合成器技术手册.pdf

特性

- 频率合成至155.52 MHz

- 19.44 MHz或9.72 MHz输入

- 基准信号选择复用

- 单电源供电:+5 V或–5.2 V

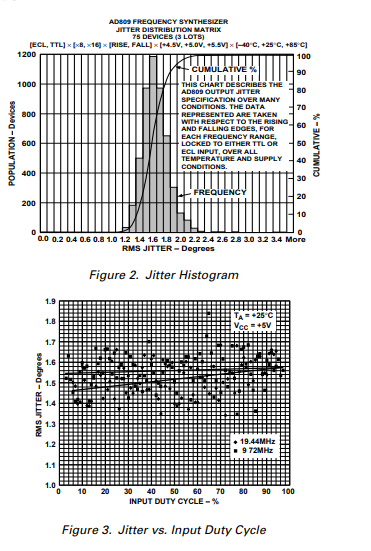

- 输出抖动:2.0度(均方根)

- 低功耗:90 mW

- 10 KH ECL/PECL兼容输出

- 10 KH ECL/PECL/TTL/CMOS兼容输入

- 封装:16引脚窄体150 Mil SOIC

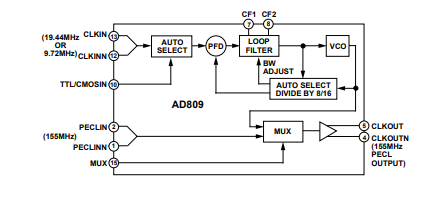

框图

典型特性曲线

使用AD809

接地层

建议使用一个接地层来连接模拟地和数字地。

电源连接

- 建议在(V_{CC})和地之间使用一个10 μF的电容。该电容应连接在(+5 V)电源线到(V_{CC2})(引脚3)之间。(V_{CC2})引脚用于为CLKOUT/CLKOUTN信号提供隔离电源。

- 建议在引脚14((AV_{CC2}))和引脚6((AV_{CC1}))之间分别使用一个10 μF的电容。在集成电路(IC)电源和地之间使用0.1 μF的电容进行去耦也是可取的。应尽可能靠近IC放置电源去耦电容。有关建议的连接方式,请参见图5“传输线路”。

传输线路

对于正发射极耦合逻辑(PECL)输入,建议使用50 Ω的传输线。

端接

- PECL输入信号应使用端接电阻。建议使用金属膜、精度为1%的电阻。

- PECL输入信号的端接电阻应尽可能靠近PECL输入引脚放置。

- 从电源到输入和输出负载电阻的连接应该是独立的,而不是串联连接。这样可以避免这些信号之间的串扰。

环路阻尼电容(C_D)

可以使用陶瓷电容作为环路阻尼电容。一个22 nF的电容可提供10的阻尼系数。

-

频率合成器

+关注

关注

5文章

368浏览量

33875 -

时钟

+关注

关注

11文章

1999浏览量

135225 -

ad809

+关注

关注

0文章

3浏览量

1042

发布评论请先 登录

基于DDS的频率合成器设计介绍

如何利用FPGA设计PLL频率合成器?

155.52兆赫频率合成器ad809数据表

AD809 155 MHz频率合成器

1930–1990 MHz 高性能 VCO/频率合成器,带集成开关 skyworksinc

AD809 155MHz频率合成器技术手册

AD809 155MHz频率合成器技术手册

评论