文章来源:学习那些事

原文作者:赵先生

本文介绍了芯片的堆叠与堆叠产生的应力问题。

多芯片堆叠

多芯片堆叠技术的出现,顺应了器件朝着小型化、集成化方向发展的趋势。该技术与先进封装领域中的系统级封装(SIP)存在一定差异。先进封装涵盖多种前沿工艺技术,如重布线层(RDL)、硅通孔(TSV)、金属凸点(Bump)以及晶圆级封装(WLP)等。晶圆级封装已突破传统封装在划片、粘片、键合和密封等方面的工艺范畴,像芯片再布线、凸点生长与倒装焊接,芯片通孔、叠层与互连,乃至扇出型晶圆级封装(FOWLP)、扇入型晶圆级封装(FIWLP),均属于广义上的封装概念。部分中道线工艺在一些工厂虽被归为后道工序,但相较于后道封装工艺,其与前道晶圆制造工艺的联系更为紧密。

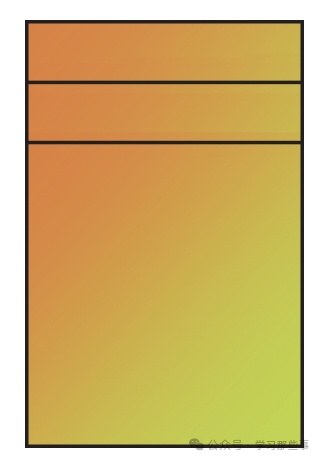

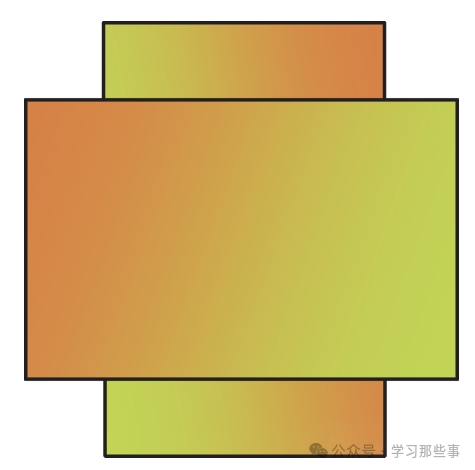

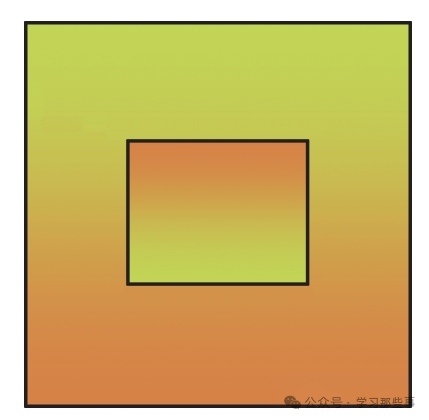

多芯片堆叠所构建的器件,同样属于SIP。不过,其采用的是传统的芯片粘接和引线键合工艺,因此本质上属于传统封装类型。芯片的叠层粘接能够大幅节省空间,但在操作过程中,需确保下层芯片的管脚(Pad)点不会被上层芯片或粘接剂覆盖,以免对后续的引线键合工序造成影响。多芯片堆叠的形式主要由芯片的大小、形状以及管脚点的分布决定,常见的堆叠形式如图1-图3所示。

图1 多芯片的错层堆叠

图2 多芯片的交叉堆叠

图3 多芯片的金字塔堆叠

多层芯片堆叠应力集中

在多层芯片堆叠过程中,由于芯片正面设有钝化层,无法采用合金烧结的方式进行芯片间的堆叠,一般会选用胶黏剂来实现粘接。具体的粘接工艺流程为,首先将最下层芯片进行粘接;接着在最下层芯片表面涂抹胶黏剂,随后粘接上层芯片,依此方式逐层叠加粘接。研究显示,由于胶黏剂与硅芯片的热膨胀系数存在差异,多层芯片之间会产生较大应力。

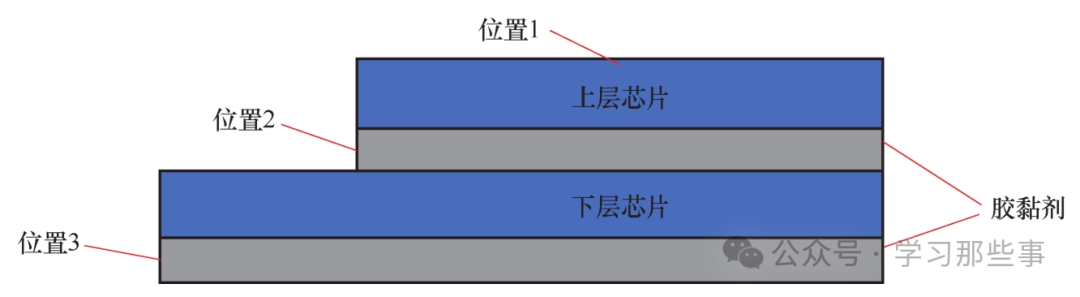

有研究人员针对塑封的多层芯片堆叠器件开展建模仿真,识别出应力集中的三种主要形式,如图4所示。

图4多层堆叠粘片主要失效位置

多层芯片堆叠应力集中产生的失效形式:

芯片与环氧塑封料分层:上层芯片与环氧塑封料之间会产生应力,这一应力致使芯片与塑封料界面处出现分层现象。

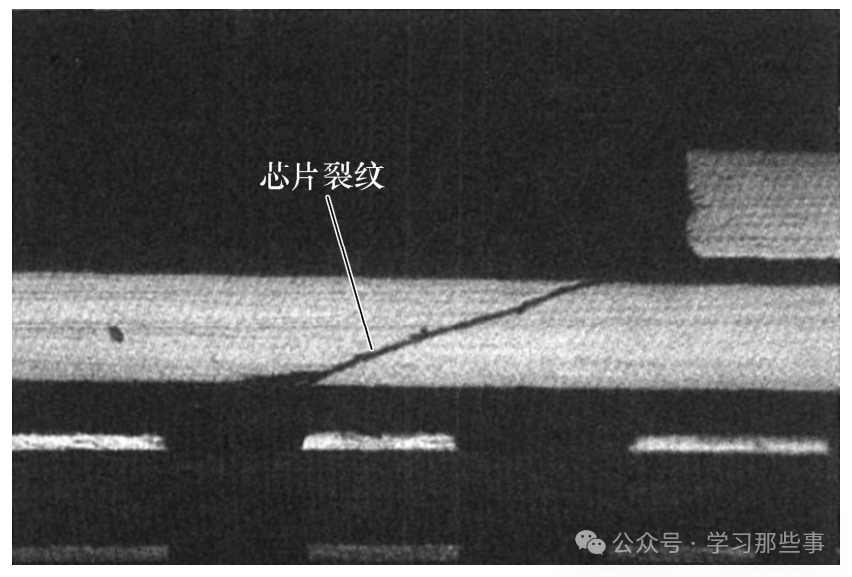

下层芯片损伤:上下层芯片间的应力会在上层芯片的边角位置高度集中。这种集中应力往往会导致下层芯片出现裂纹,严重时甚至造成芯片断裂,对器件造成致命性破坏,具体可参考图5。

图5下层芯片裂纹

芯片与胶黏剂整体和环氧塑封料分层:下层芯片边缘与环氧塑封料之间存在应力,这种应力会使芯片和胶黏剂构成的整体,与环氧塑封料之间发生分层。

研究表明,上述应力的大小,与材料的热膨胀系数、芯片厚度等关键参数紧密相关。

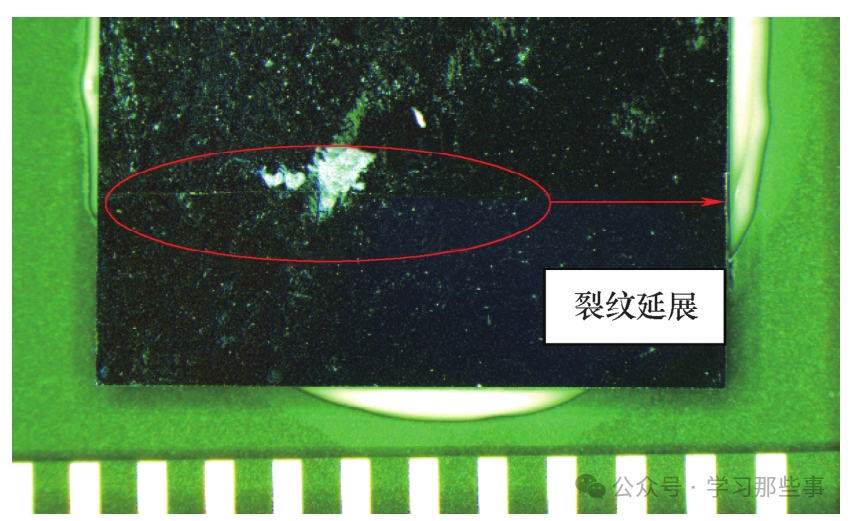

芯片的裂纹

为了通过目检清晰观察胶黏剂从芯片四周溢出的轮廓,通常会在芯片下方悬空部位填充不导电胶。研究人员将硅片切割成与待封装芯片相同尺寸,并分别堆叠至两层、三层、四层,随后开展 -55℃至125℃的温度循环试验。试验结果显示,填充不导电胶的电路出现了热失配问题。在温度循环试验结束后,上层芯片均出现了不同程度的裂纹,裂纹首先沿底层芯片边缘位置扩展,最终有可能贯穿整个芯片,具体现象如图6所示。

仿真结果表明,使用不导电胶填充的模型,其最大应力位置与实际观察到的上层芯片裂纹位置一致,均出现在上层芯片、填充的不导电胶、下层芯片边缘三者的交接面上。而未使用不导电胶填充的模型,上层芯片的最大应变相较于使用不导电胶填充的模型,降低了91.7%。由此可见,硅芯片与胶黏剂之间匹配性的差异,是引发芯片裂纹的主要原因。这些裂纹在温度循环等可靠性试验过程中,会进一步扩展,严重时可导致芯片断裂。底部无填充的堆叠芯片情况,如图7所示。

图6堆叠粘片的裂纹

图7无填充的堆叠芯片

爬胶与胶膜

在传统封装工艺里,芯片粘接普遍采用直接涂抹导热胶的方式。这种导热胶不仅使用便捷,而且能提供足够的粘接强度。然而,在多层堆叠芯片的场景下,芯片通常会被减薄至很薄的尺寸,部分芯片厚度甚至达到100μm。当使用常规导热胶进行这类超薄芯片间的粘接时,爬胶问题频繁出现。爬胶会致使部分导热胶溢出到芯片表面,污染管脚(Pad)点,进而对后续的键合工序造成严重影响。

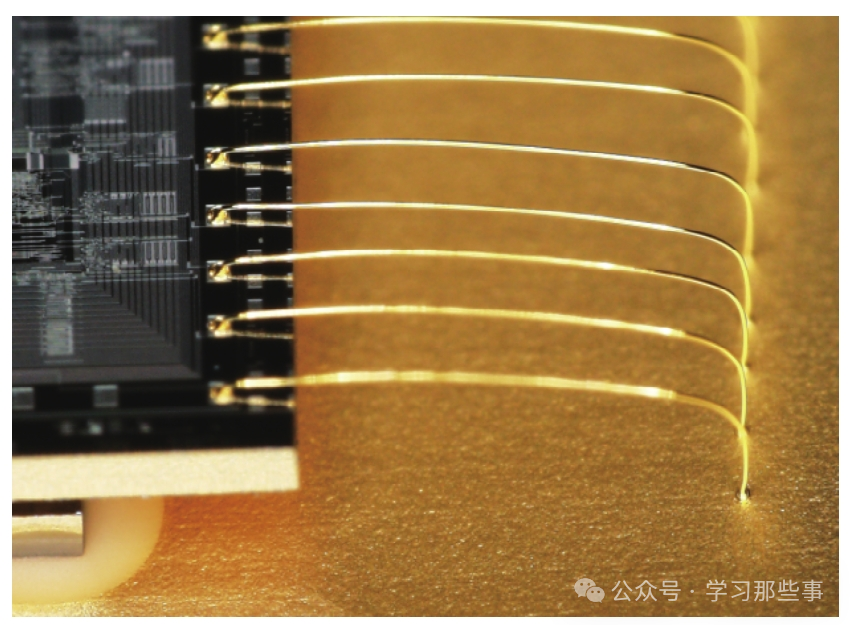

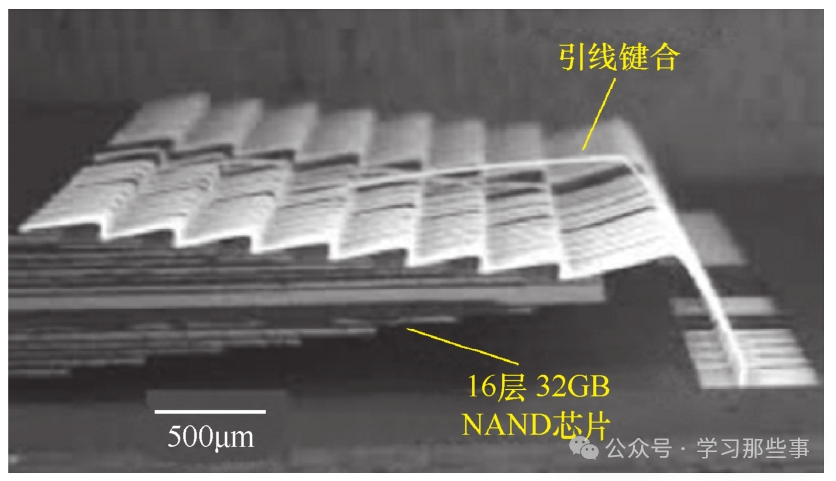

为解决这一难题,材料供应商研发出导热胶膜,以此替代传统导热胶。导热胶膜具有固定的厚度,借助这一特性,能够有效控制胶量和粘接厚度,从而避免爬胶现象的发生。不仅如此,导热胶膜还能在高度设计方面提供更大的灵活性。从实际应用来看,在民用产品领域,部分多层堆叠结构已经实现了百余层的堆叠。图8展示了一种存储器芯片的堆叠示意图。

图8一种存储器芯片的堆叠示意图

-

芯片

+关注

关注

462文章

53550浏览量

459258 -

晶圆

+关注

关注

53文章

5348浏览量

131703 -

封装

+关注

关注

128文章

9146浏览量

147907 -

堆叠

+关注

关注

0文章

37浏览量

17013

原文标题:芯片的堆叠与堆叠产生的应力问题

文章出处:【微信号:深圳市赛姆烯金科技有限公司,微信公众号:深圳市赛姆烯金科技有限公司】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

一文详解多芯片堆叠技术

一文详解多芯片堆叠技术

评论