概述

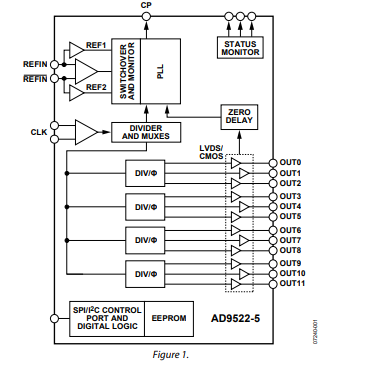

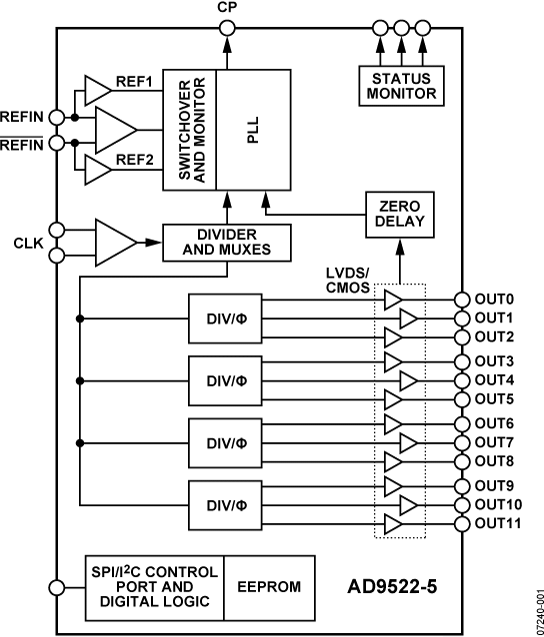

AD9522-5提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL),可以配合外部VCO使用。

AD9522串行接口支持SPI和I^2^C®端口。封装内EEPROM可以通过串行接口进行编程,存储用于上电和芯片复位的用户定义寄存器设置。

数据表:*附件:AD9522-5 12 LVDS 24 CMOS输出时钟发生器技术手册.pdf

AD9522具有12路LVDS输出(分为四组)。任一路800 MHz LVDS输出均可重新配置为两路250 MHz CMOS输出。

每组输出具有一个分频器,其分频比(从1至32)和相位(粗调延迟)均可以设置。

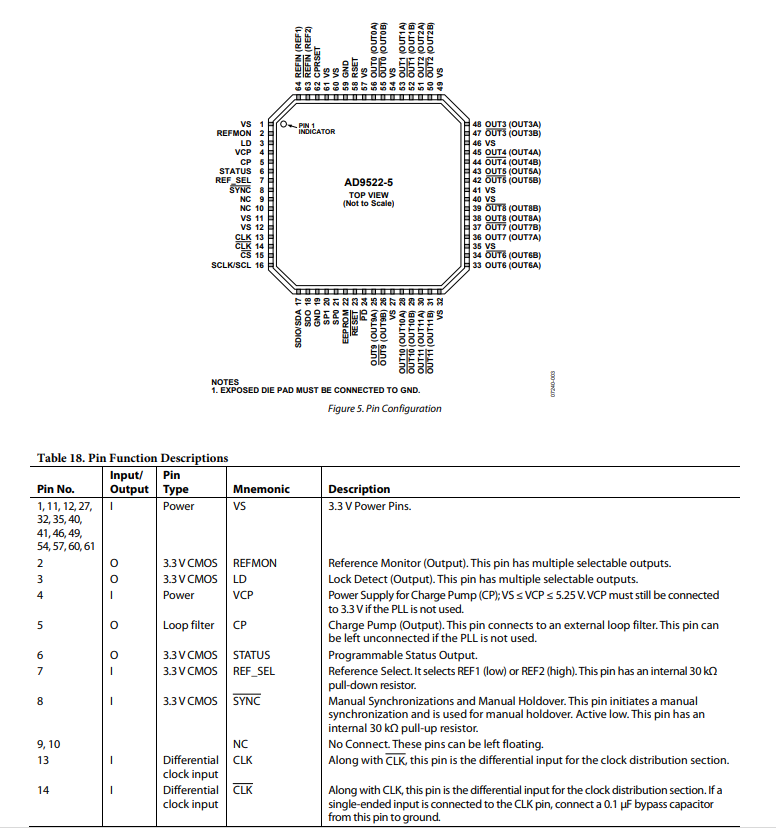

AD9522提供64引脚LFCSP封装,可以采用3.3 V单电源供电。外部VCO的工作电压最高可达5.5 V。

AD9522的额定工作温度范围为40°C至+85°C标准工业温度范围。

AD9520-5是AD9522-5的等效产品,采用LVPECL/CMOS驱动器而非LVDS/CMOS驱动器。

^1^AD9522在本数据手册中泛指AD9522系列的所有器件。但是,使用AD9522-5时,它仅指AD9522系列的该特定器件。

应用

- 低抖动、低相位噪声时钟分配

- SONET、10Ge、10G FC和其它10 Gbps协议的时钟产生和转换

- 前向纠错(G.710)

- 为高速ADC、DAC、DDS、DDC、DUC、MxFE提供时钟

- 高性能无线收发器

- 自动测试设备(ATE)和高性能仪器仪表

- 宽带基础设施

特性

- 低相位噪声锁相环(PLL)(欲了解更多信息,请参考数据手册。)

- 12路800 MHz LVDS输出,分为4组(欲了解更多信息,请参考数据手册。)

- 上电时所有输出自动同步

- 可以根据需要手动同步多路输出

- SPI和I^2^C兼容型串行控制端口

- 64引脚LFCSP

- 非易失性EEPROM存储配置

框图

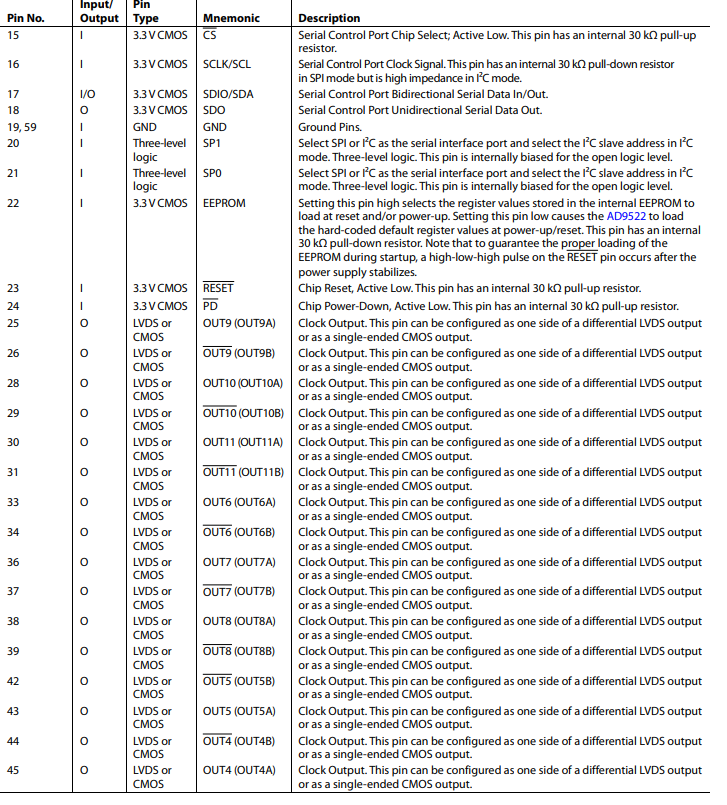

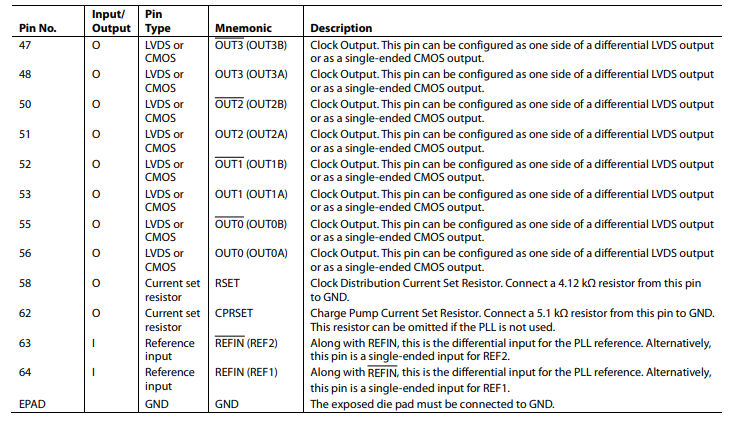

引脚配置描述

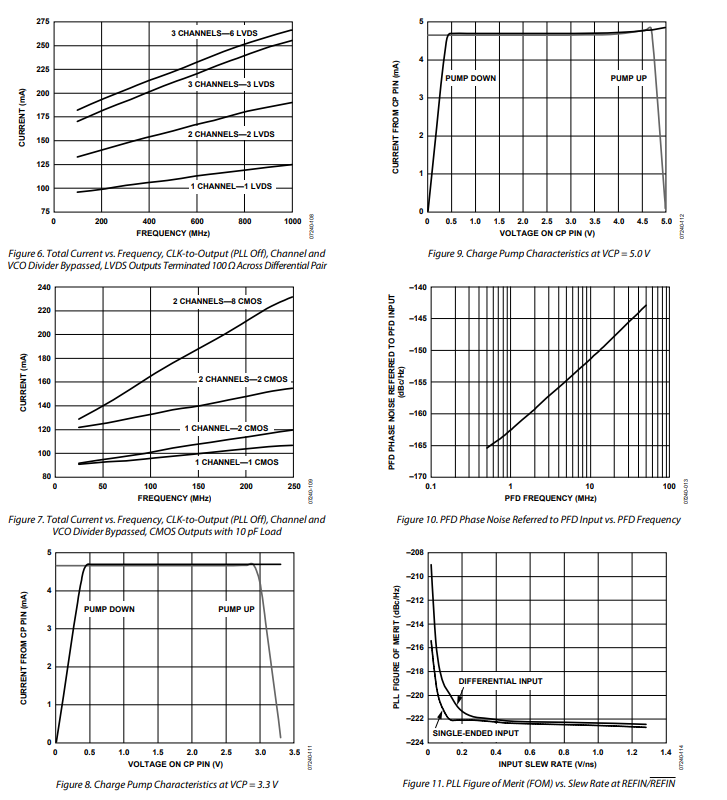

典型性能特征

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

CMOS

+关注

关注

58文章

6236浏览量

243425 -

时钟

+关注

关注

11文章

2000浏览量

135246 -

ad9522

+关注

关注

0文章

13浏览量

2626

发布评论请先 登录

相关推荐

热点推荐

AD9522-5 12 LVDS/24 CMOS Output Clock Generator

电子发烧友网为你提供(adi)AD9522-5相关数据表资料,例如:AD9522-5的引脚图、接线图、封装手册、中文资料、英文资料,AD9522-5真值表,

发表于 02-15 18:39

AD9520-0:12路LVPECL/24路CMOS输出时钟发生器,集成2.8 GHz VCO

AD9520-0:12路LVPECL/24路CMOS输出时钟发生器,集成2.8 GHz VCO

发表于 03-19 09:02

•0次下载

AD9522-1:12 LVDS/24 CMOS输出时钟发生器,集成2.4 GHz压控振荡器数据表

AD9522-1:12 LVDS/24 CMOS输出时钟发生

发表于 04-16 20:21

•1次下载

AD9522-0:12集成2.8 GHz压控振荡器数据表的LVDS/24 CMOS输出时钟发生器

AD9522-0:12集成2.8 GHz压控振荡器数据表的LVDS/24 CMOS

发表于 04-17 20:08

•0次下载

AD9522-3:12集成2 GHz压控振荡器数据表的LVDS/24 CMOS输出时钟发生器

AD9522-3:12集成2 GHz压控振荡器数据表的LVDS/24 CMOS

发表于 04-28 10:38

•7次下载

AD9522-4:12集成1.6 GHz压控振荡器数据表的LVDS/24 CMOS输出时钟发生器

AD9522-4:12集成1.6 GHz压控振荡器数据表的LVDS/24 CMOS

发表于 04-29 19:06

•1次下载

集成2.2 GHz VCO数据表的AD9522-2:12 LVDS/24 CMOS输出时钟发生器

集成2.2 GHz VCO数据表的AD9522-2:12 LVDS/24 CMOS输出

发表于 04-29 20:28

•11次下载

AD9522-2:高性能时钟发生器的深度剖析

AD9522-2:高性能时钟发生器的深度剖析 在电子设计领域,时钟发生器是确保系统稳定运行的关键组件。今天,我们聚焦于Analog Devices的AD9522-2,一款具备

AD9522-3:高性能时钟发生器的技术剖析与应用指南

LVDS/24 CMOS输出时钟发生器,集成了2 GHz VCO,具备低相位噪声、高灵活性等诸多优势,广泛应用于通信、仪器仪表等领域。本文

AD9522-4:高性能时钟发生器的深度解析

AD9522-4:高性能时钟发生器的深度解析 在电子设计领域,时钟发生器的性能直接影响着整个系统的稳定性和可靠性。AD9522-4作为一款12

AD9522-1:高性能时钟发生器的深度剖析与应用指南

/24 CMOS输出时钟发生器,集成了2.4 GHz VCO,具备低相位噪声、高灵活性等诸多优点,广泛应用于通信、仪器仪表等众多领域。今天,我们就来深入了解一下这款芯片。 文件下载:

AD9522-0:高性能时钟发生器的深度剖析

AD9522-0:高性能时钟发生器的深度剖析 引言 在电子设计领域,时钟发生器对于确保系统的稳定性和性能起着至关重要的作用。AD9522-0作为一款

AD9522-5:高性能时钟发生器的设计与应用

AD9522-5:高性能时钟发生器的设计与应用 在电子设计领域,时钟发生器是至关重要的组件,它为各种电路提供精确的时钟信号,确保系统的稳定运行。本文将深入探讨AD

AD9522-5 12 LVDS/24 CMOS输出时钟发生器技术手册

AD9522-5 12 LVDS/24 CMOS输出时钟发生器技术手册

评论