本文作者:Jonathan Dodge, P.E., Mike Zhu, Shusun Qu ,Mike Tian

随着Al工作负载日趋复杂和高耗能,能提供高能效并能够处理高压的可靠SiCJFET将越来越重要。在第一篇文章和第二篇文章中我们重点介绍了SiCJFET并联设计的挑战,本文将介绍演示和测试结果。

演示和测试结果

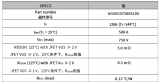

根据上述指南设计了一个演示板,并显示了四个器件的测试结果:

UJ4SC075006K4S

UJ4C075023K4S

UF3SC120009K4S

UF3SC120016K4S

演示板设计

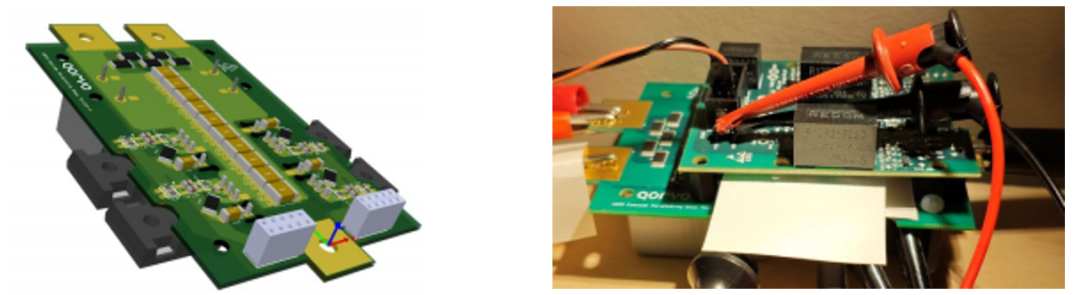

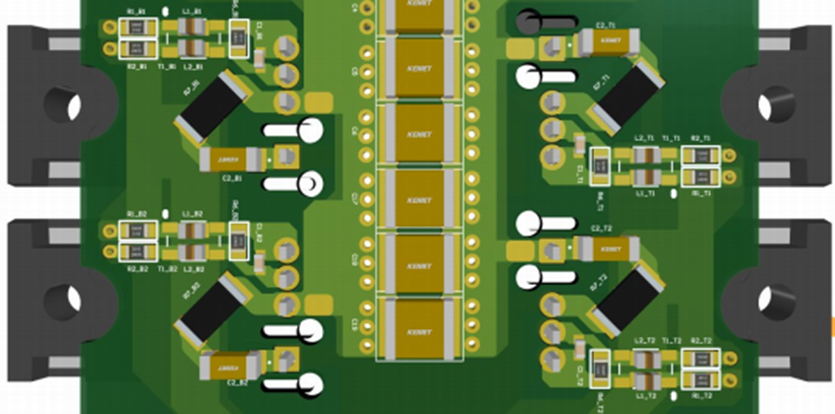

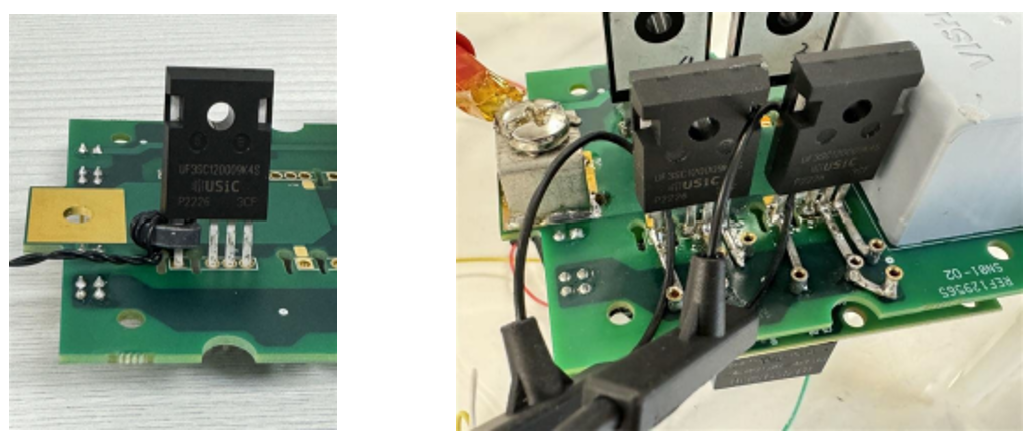

图 1 显示了演示和测试板,其中包括一块并联了两个器件的半桥拓扑电源板和一块栅极驱动器板。

图 1 演示和测试板图片

本设计示例遵循功率环路和栅极驱动电路的对称布局建议。同时,直流母线电容和去耦电容采用对称布局以最小化换流环路。

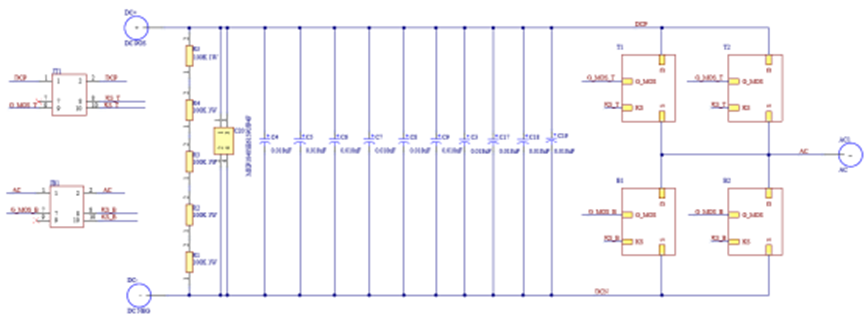

图2和图3展示了该演示设计的原理图,其中使用了铁氧体磁珠和共模电感(可选)用于研究不同条件下的效果。

图 2 演示电路设计示意图

图 3 演示电路设计示意图

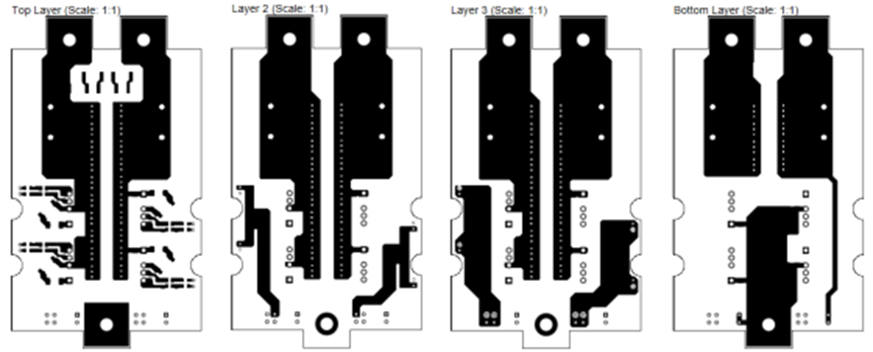

图 4 演示电源板 PCB 布局

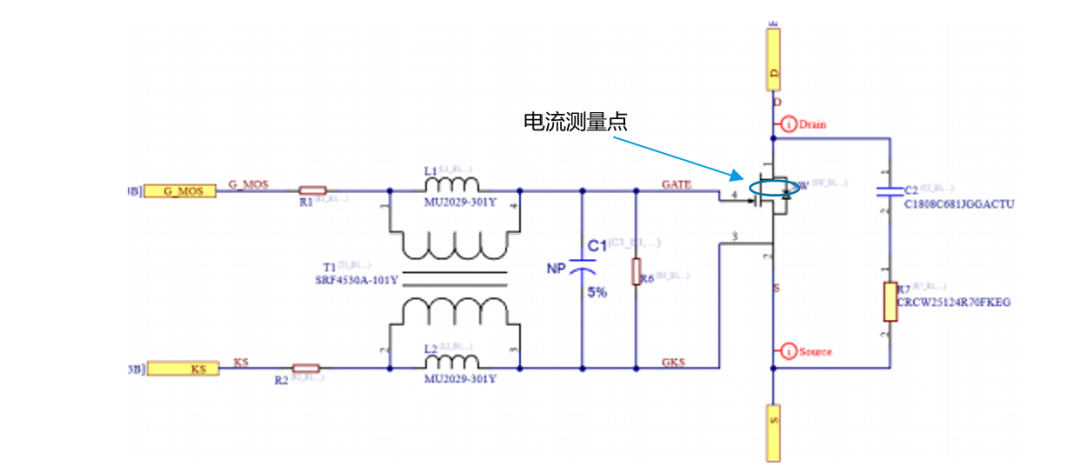

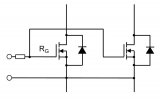

图5展示了器件RC缓冲电路与栅极驱动电路布局的示例设计,该设计的核心要点在于尽可能缩短RC缓冲电路与功率器件的距离,并对并联器件的栅极驱动电路采用对称布局。

图 5 RC 缓冲电路和栅极电路布局示例

测试结果

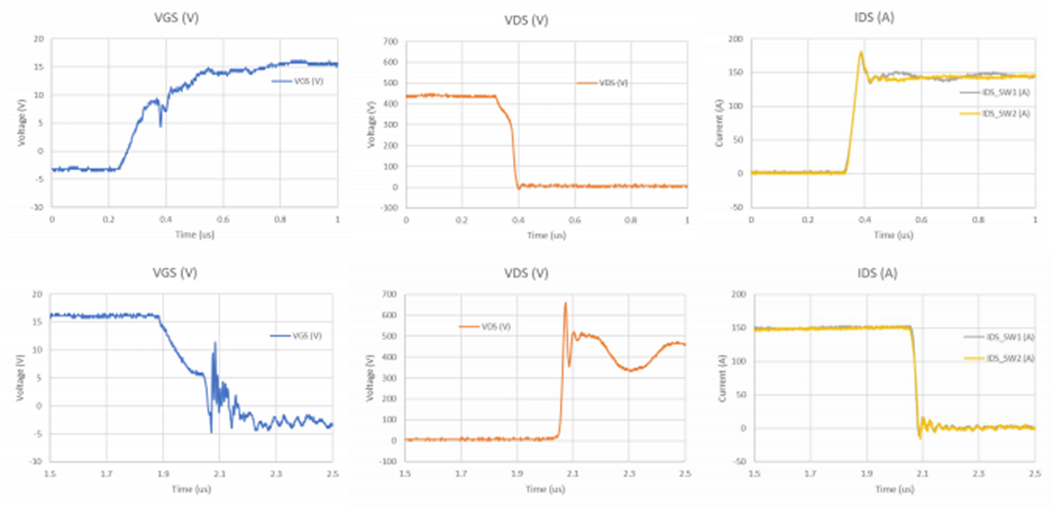

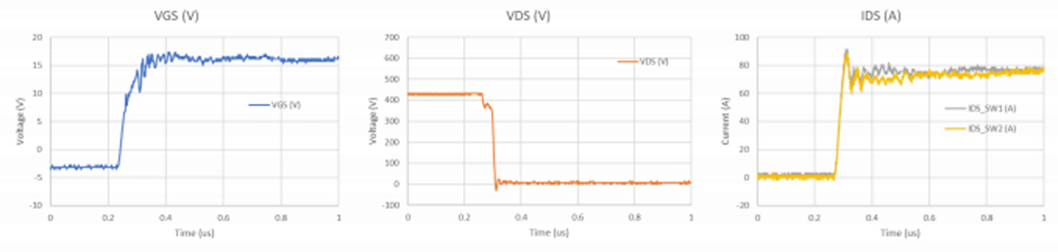

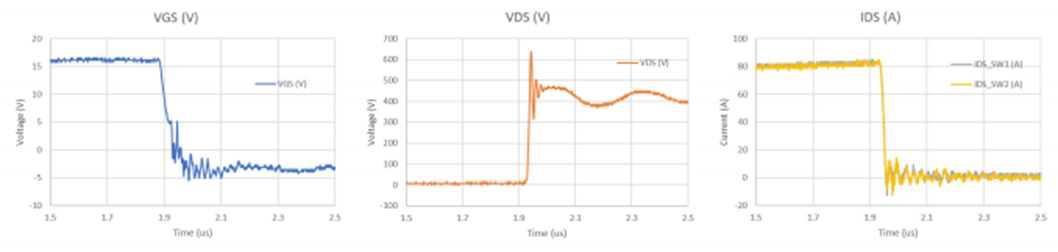

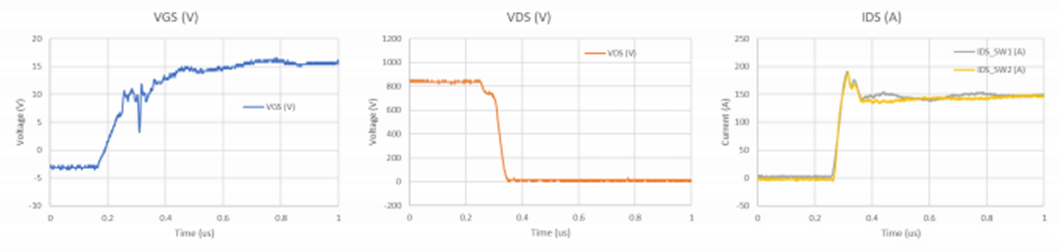

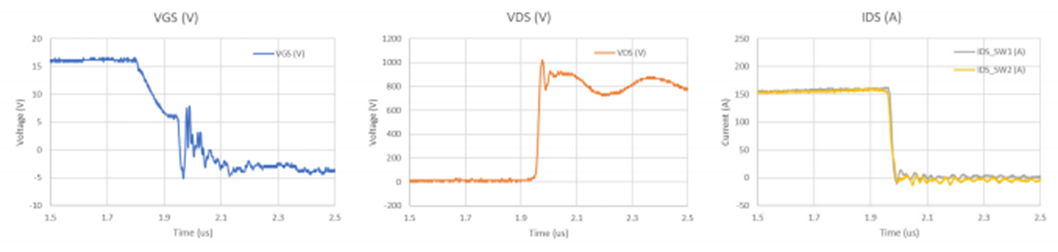

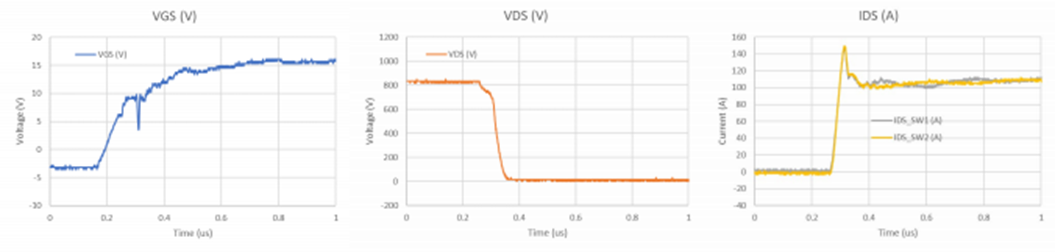

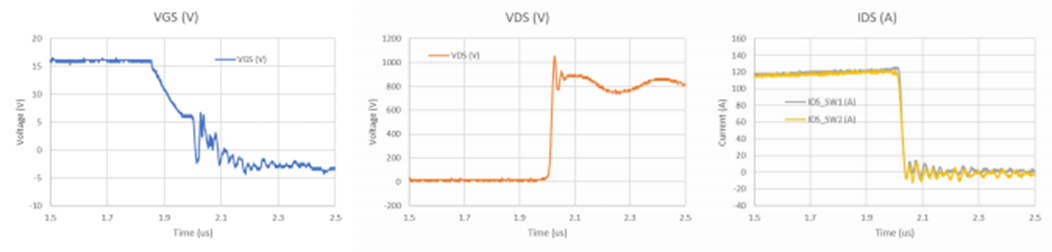

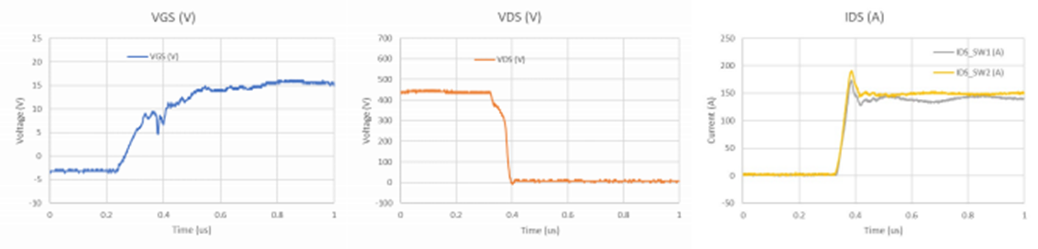

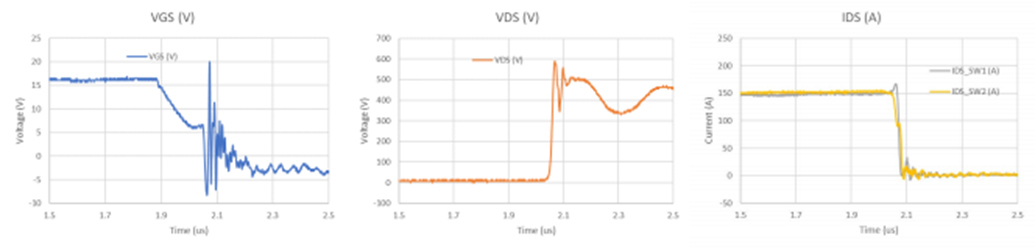

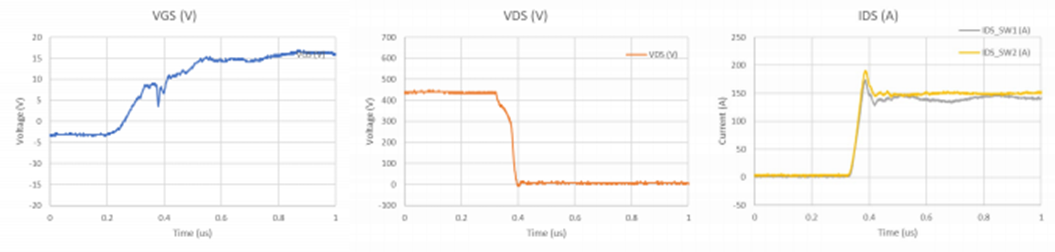

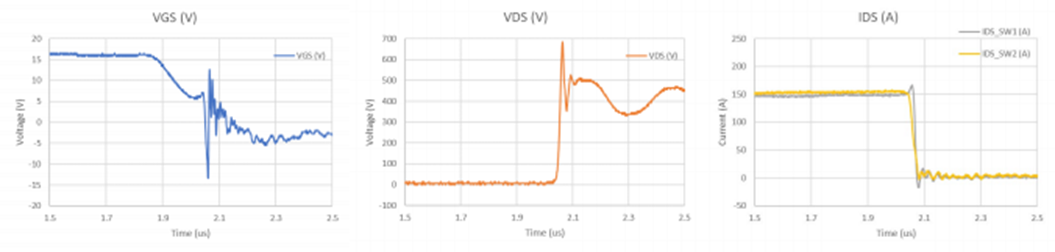

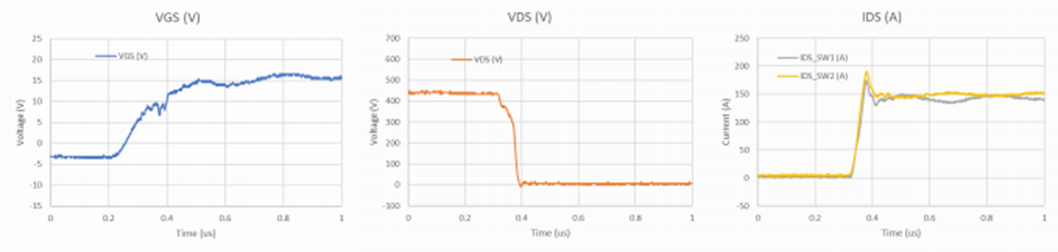

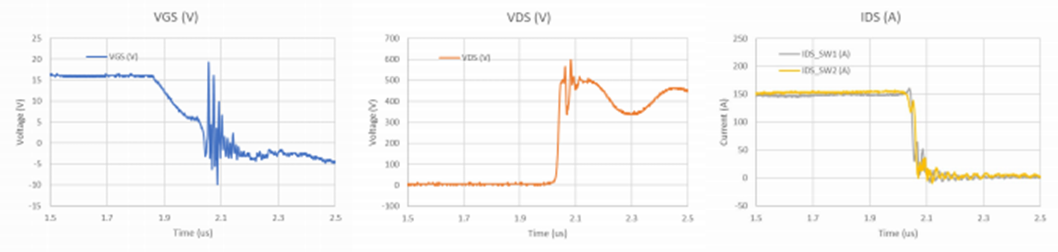

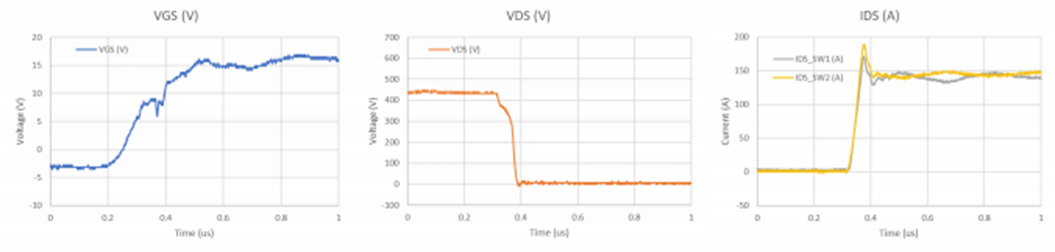

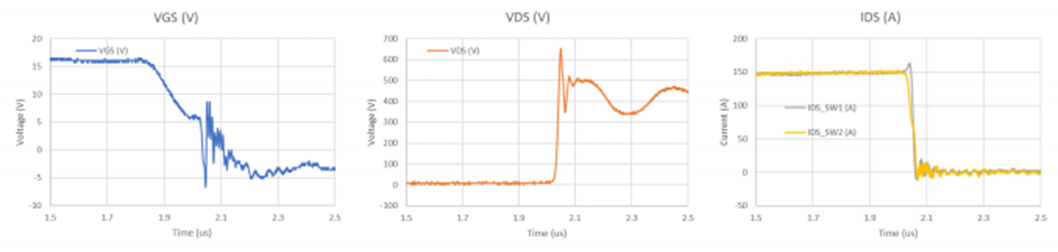

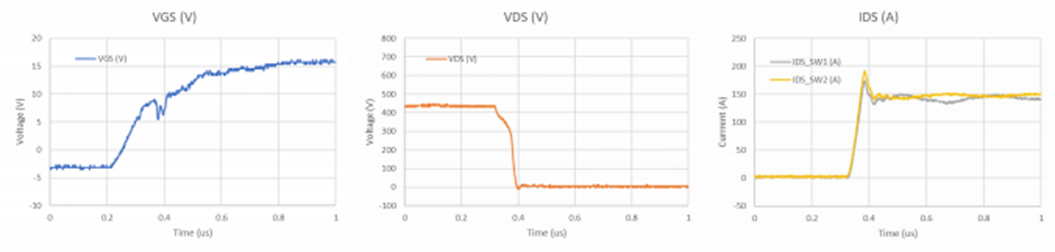

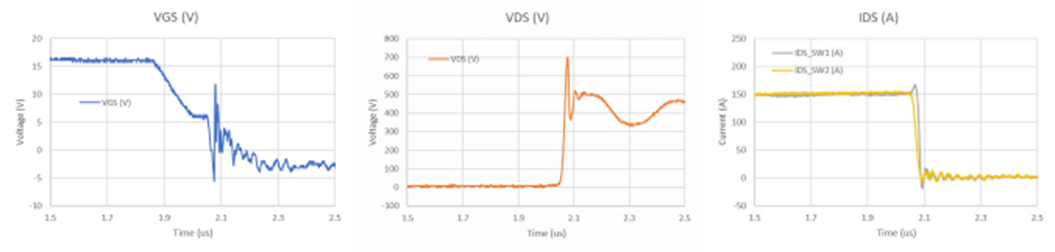

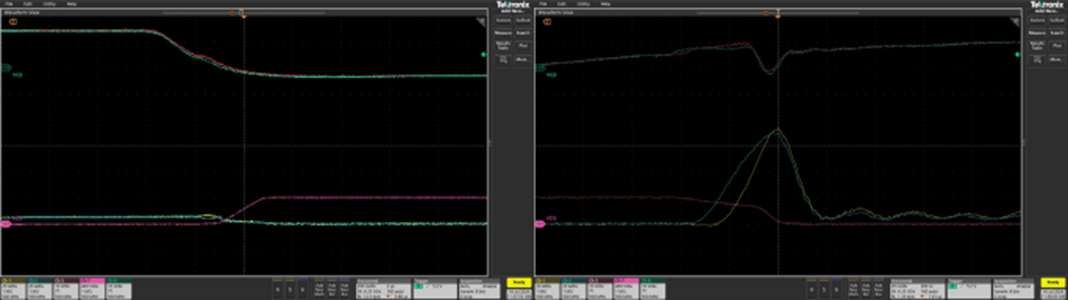

图 6 至图 9 显示了该示例设计的 SiC FET 并联测试结果,栅极和Kelvin源极上都有铁氧体磁珠。

图 6 开关波形-UJ4SC075006K4S

图7 开关波形-UJ4C075023K4S

图 8 开关波形-UF3SC120009K4S

图9 开关波形-UF3SC120016K4S

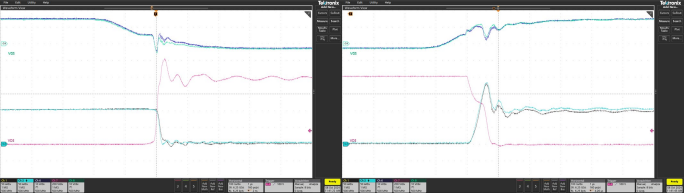

仿真栅极阈值失配

通常,由于各器件的实际参数与数据手册标称值之间存在差异(即便差异微小),此类失配现象不可避免。因此,为了测试铁氧体磁珠和共模电感在栅极电路上的有效性,在基于UJ4SC075006K4S器件搭建的测试平台中,通过改变单个栅极电阻值(一个为 6.8 欧姆,另一个为 6.2 欧姆)来仿真栅极阈值电平失配状态。图 10 至图 14 显示了采用不同措施缓解仿真栅极阈值失配的波形图。

图10 通过改变栅极电阻来仿真栅极阈值失配(未使用铁氧体磁珠)

图11 栅极上有铁氧体磁珠的波形

图 12 Kelvin源上有铁氧体磁珠的波形

图13 栅极和Kelvin源极上均有铁氧体磁珠的波形

图 14 栅极电路上有共模电感的波形

从上述测试结果可以看出,当器件出现不可避免的栅极阈值失配时,栅极电路上的共模电感是减轻 VGS 和 VDS 负面影响的最佳方法。

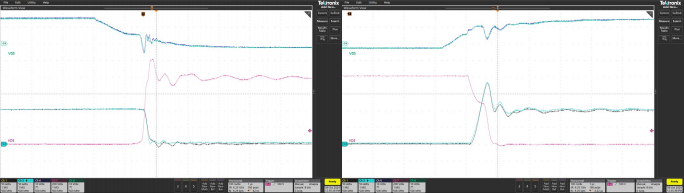

仿真布局导致的失配

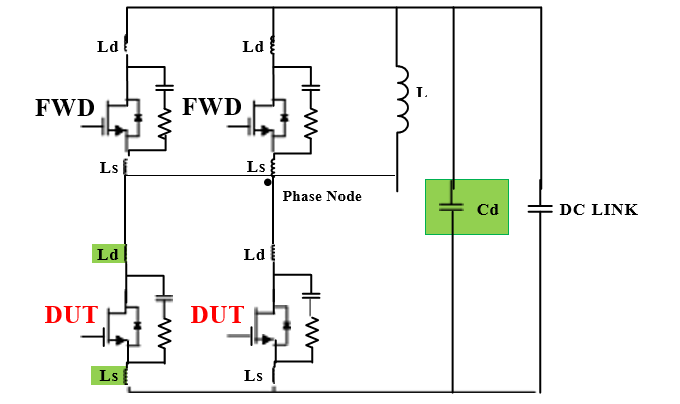

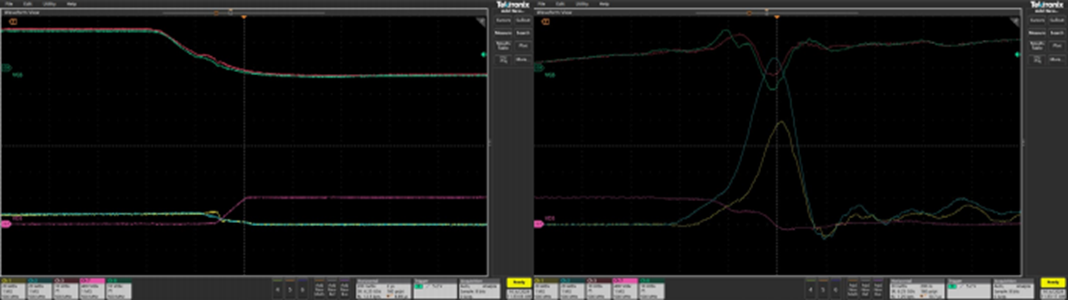

对称布局同样是并联器件设计的关键要点,因为非对称布局会导致不同支路的漏极走线电感(Ld)与源极走线电感(Ls)产生差异,进而引发动态电流失配或瞬态振荡。此外,去耦电容(Cd)在布局中的位置是否对称也是影响因素之一。

因此,为验证铁氧体磁珠与共模电感在栅极电路上的作用,我们以 UF3SC120009K4S 为基础,通过改变漏极/源极引线的长度来仿真失配的 Ld/Ls 布局,并对比了不同Cd布局位置的影响。图14展示了Ld、Ls及Cd的布局位置分布,图15至图19则展示了通过不同优化措施减轻非对称布局负面影响的波形对比。

图14 Ld、Ls 和Cd 的位置

图15 栅极和Kelvin源上均有铁氧体磁珠的Ld 不平衡波形(直流母线400V,Id = 8A)

图 16 栅极和Kelvin源上均有铁氧体磁珠的 Ls 不平衡波形(直流母线 400V,Id = 6A)

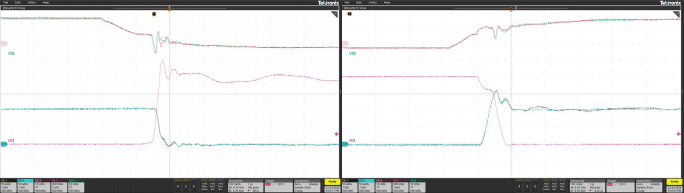

图17 Cd 在不对称位置,栅极和Kelvin源上都有铁氧体磁珠的波形(直流母线800V,Id= 100A)

图18 Cd 在不对称位置,栅极和Kelvin源极上均有共模电感的波形(直流母线800V,Id= 100A)。

图19 Cd 在对称位置,栅极和Kelvin源上均有共模电感的波形(直流母线800V,Id= 100A)。

图15展示了由严重不平衡的Ld所导致的大动态电流失配。Ld不平衡问题只能通过对称的布局设计本身来解决。图16显示了由Ls不平衡引起的动态电流失配。

为避免器件损坏,本测试中我们未设置过大的Ls不平衡,因为Ls不仅会影响功率环路,还会影响栅极环路。Ls不平衡可通过以下方式解决:采用对称布局设计并添加铁氧体磁珠或CMC。添加铁氧体磁珠可以解决Ls 不平衡问题,但效果不如CMC显著。此外,与CMC相比,铁氧体磁珠会降低器件速度,增加开关损耗。因此,我们建议在实际并联应用中采用CMC结合对称布局设计方案。

在实现Ld和Ls的平衡后,图17展示了由Cd不平衡引起的动态电流失配现象(本案例中仍使用铁氧体磁珠)。通过对比图17和图18可以看出,在栅极环路中使用CMC相较于使用铁氧体磁珠,可以更有效地平衡电流失配和Vgs电压。同样,与CMC 相比,铁氧体磁珠会减慢器件的速度,增加开关损耗。

但有一点我们需要注意:CMC 只能消除Vgs 电压失配,但不能消除电流失配。对于电流失配,CMC仅能起到缓解作用。因此,如图19所示,若要彻底消除电流失配,唯一有效的方法是将Cd尽可能靠近并联半桥并实现对称布局。基于上述分析,我们再次建议在实际并联应用场景中使用CMC,并采用对称布局设计。

设计和测试中的最佳实践

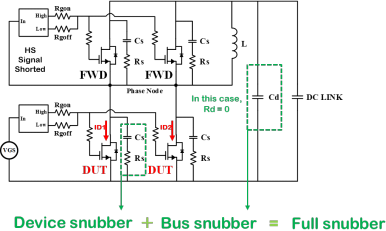

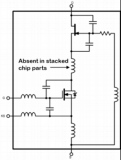

图20 成功并联SiC FET 需要器件漏极至源极缓冲电路和母线缓冲电路

•成功并联SiC FET 需要器件缓冲电路,如图20 所示。用户指南中推荐了起始值。

•对称布局至关重要,测试证实,不对称的漏极和源极杂散电感以及去耦电容的位置会导致开关电流差异过大。

•如果栅极阈值的微小失配和微小的不对称布局不可避免,那么栅极和源极环路上的CMC是消除瞬态电流失配或瞬态振荡的最有效方法。

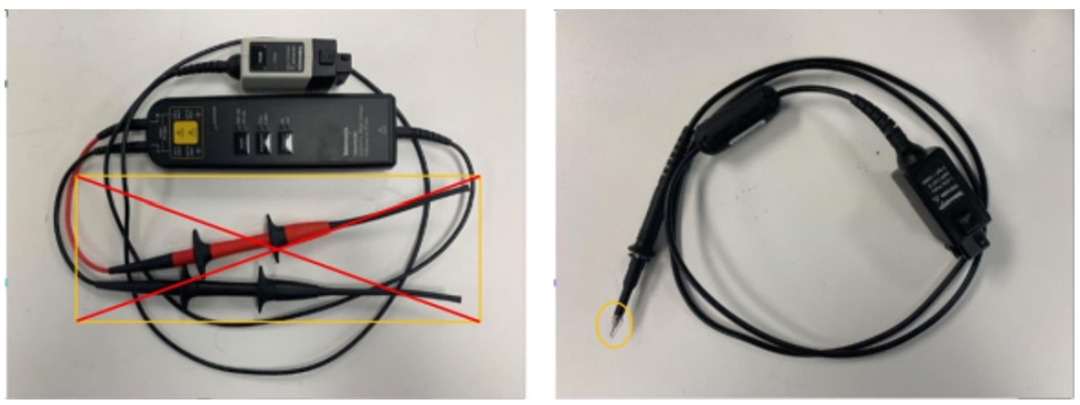

•不推荐使用铁氧体磁芯(环形)电流互感器(CT),因为它会由于引线与磁芯之间的互感而导致不平衡的漏极杂散电感。应使用罗氏线圈电流探头进行电流测量,如图 21所示。

图21 电流测量方法,左:铁氧体磁芯CT(不推荐);右:罗氏线圈探头

• 对于电压测量,不推荐使用差分探头,因为其引线和导线的环路较大(会增加环路电感),建议使用环路电感较小的无源探头,如图22 所示。

图22 电压探头,左:差分探头(不推荐使用);右:环路电感较小的无源探头

• 由于dv/dt很高,共模噪声很容易耦合到栅极到源极的信号测量中,滤除这种噪声的一种方法是在电压探头线缆上添加铁氧体磁芯,并扭转这些线缆,如图23 所示。

图23 将线缆扭转,并使用铁氧体磁芯过滤共模栅源噪声

结语

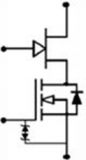

尽管SiC JFET cascode结构具有很高的增益和开关压摆率,只要遵循本应用笔记中概述的指导原则,就能成功实现并联。本文虽然只讨论了两个器件并联的情况,但这些并联准则适用于任何数量的器件并联。最后,这些指导原则不仅适用于cascode,也适用于任何其他类型的电压栅控功率晶体管。

对于需要并联两个以上分立器件、要求低dv/dt 且不需要器件 RC缓冲电路的大功率逆变器等应用,安森美(onsemi)建议使用Combo-FET 器件。

-

并联

+关注

关注

5文章

257浏览量

36958 -

原理图

+关注

关注

1341文章

6423浏览量

244849 -

JFET

+关注

关注

3文章

191浏览量

23316 -

SiC

+关注

关注

32文章

3521浏览量

68170

原文标题:速看!SiC JFET并联设计白皮书完整版

文章出处:【微信号:onsemi-china,微信公众号:安森美】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

SiC MOSFET模块并联应用中的动态均流问题

安森美SiC Combo JFET的静态特性和动态特性

电源设计笔记:适用于高性能应用的SiC JFET

安森美SiC Cascode JFET的背景知识和并联设计

安森美SiC Combo JFET技术概览和产品介绍

UnitedSiC推出业界最佳6mΩ SiC FET

电源设计说明:用于高性能应用的 SiC JFET

SiC MOSFET的器件演变与技术优势

虚幻引擎的纹理最佳实践

安捷伦LTE和WiMAX测试设备获最佳实践奖

安森美SiC cascode JFET并联设计的挑战

SiC JFET并联设计和测试中的最佳实践

SiC JFET并联设计和测试中的最佳实践

评论