文章来源:学习那些事

原文作者:小陈婆婆

本文介绍了逻辑集成电路制造中有关良率提升以及对各种失效的分析。

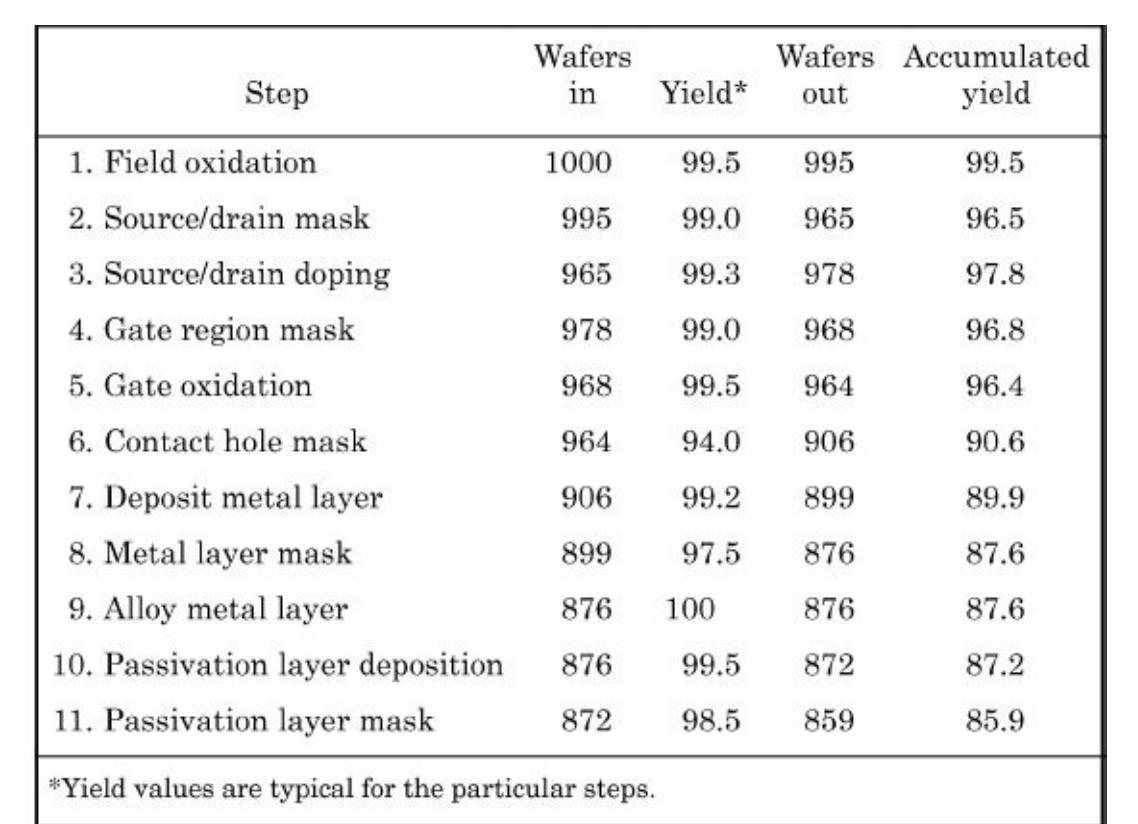

良率是衡量生产线能力的重要指标,在制造过程中,每个环节都有可能引起产品失效,良率会受到多种因素的影响,包括机台参数漂移、工艺波动等。

工艺引起的器件失效可以分为参数性失效和功能性失效。参数性失效主要与器件的物理参数有关,如栅极尺寸、有源区尺寸等,而蚀刻工艺对参数性失效有很大影响。功能性失效则往往由晶圆上的缺陷引起,如物理性异物、化学性污染等,等离子体蚀刻对功能性失效也有显著影响。

良率与缺陷

在逻辑集成电路制造中,良率提升是一个复杂而关键的过程,其中缺陷管理起着至关重要的作用。缺陷可以分为随机缺陷和系统性缺陷,两者对良率的影响不同,需要采取不同的策略进行改善。

随机缺陷与系统型缺陷

随机缺陷在时间和空间上随机出现,通常保持在很低的水平,且难以完全消除。这类缺陷一般通过统计方法进行监控和管理,以确保它们对良率的影响控制在可接受范围内。

相比之下,系统性缺陷与特定的工艺条件或版图特征紧密相关,具有较高的发生概率。例如,蚀刻反应腔室掉落的颗粒物,如果数量较多且频繁,就属于系统性缺陷。这类缺陷可以通过改进工艺设备、优化工艺参数或改变材料等方法来消除或降低其影响。以蚀刻工艺为例,通过改进腔室内材料或涂层、定期清理腔室以及优化蚀刻参数等措施,可以有效减少颗粒物的掉落,从而提升良率。

良率提升与缺陷查找

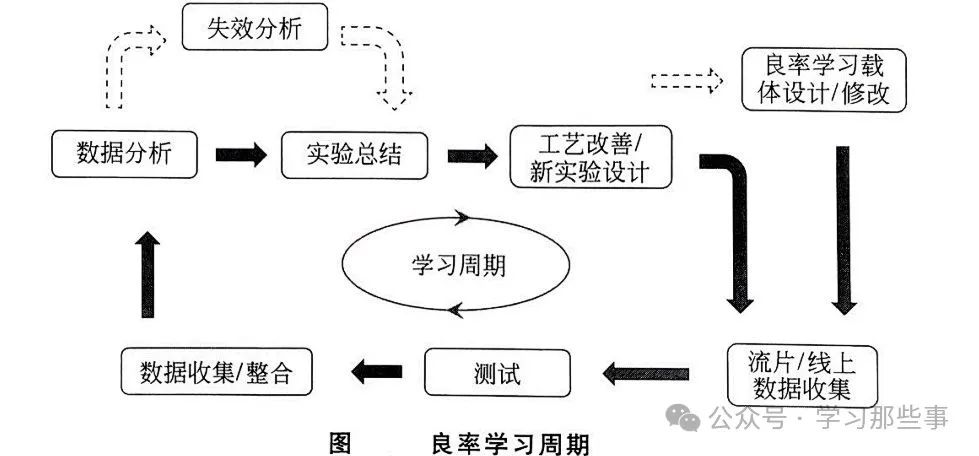

良率提升的实质是一个不断学习和改进的过程。每个学习周期包括实验设计、结果分析、工艺优化和反馈实施等环节。为了快速提升良率,需要缩短学习周期,尽快将实验结果反馈到生产线上进行下一轮的工艺改善。

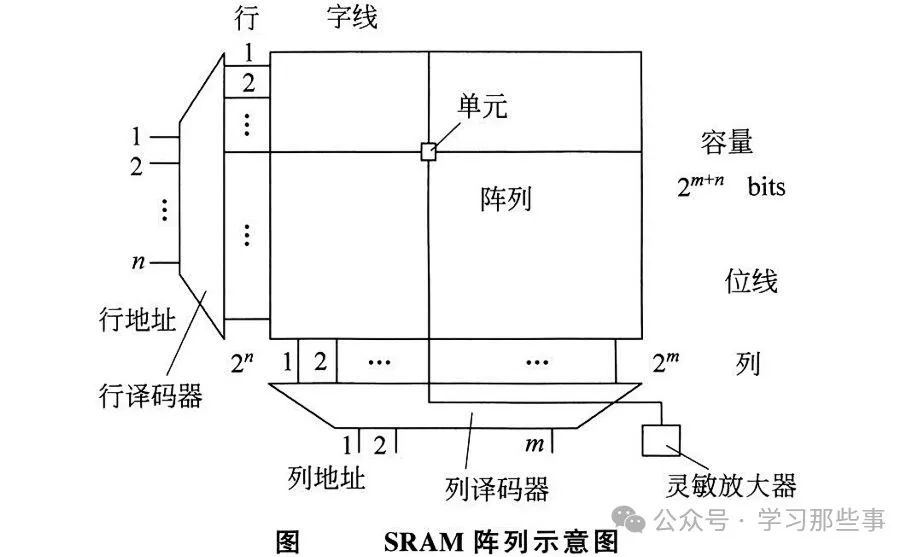

在制造厂开发新一代成套工艺时,通常会使用SRAM作为良率学习载体。SRAM具有较高的密度和缺陷覆盖能力,能够快速并精准地定位缺陷,便于进行失效分析和工艺优化。然而,需要注意的是,SRAM并不能完全覆盖逻辑电路版图中的各种难点,因此在逻辑产品上也需要进行良率学习。SRAM良率学习的经验可以为逻辑产品良率的提升提供有益的参考。

为了有效分析良率数据并确认影响良率的原因,可以将良率分解为各种因素单独起作用时的良率。其中,缺陷有限良率(DLY)是一个重要的指标,它反映了只有缺陷这一种机理起作用时产品能达到的最高良率。通过监控DLY,可以更准确地评估工艺上的缺陷情况,并采取相应的措施进行改善。

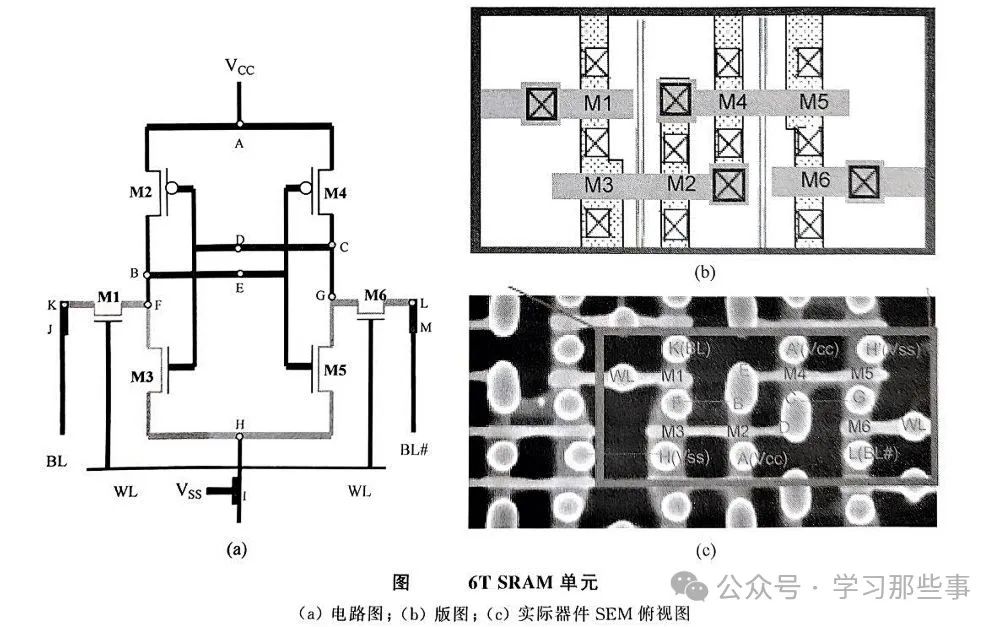

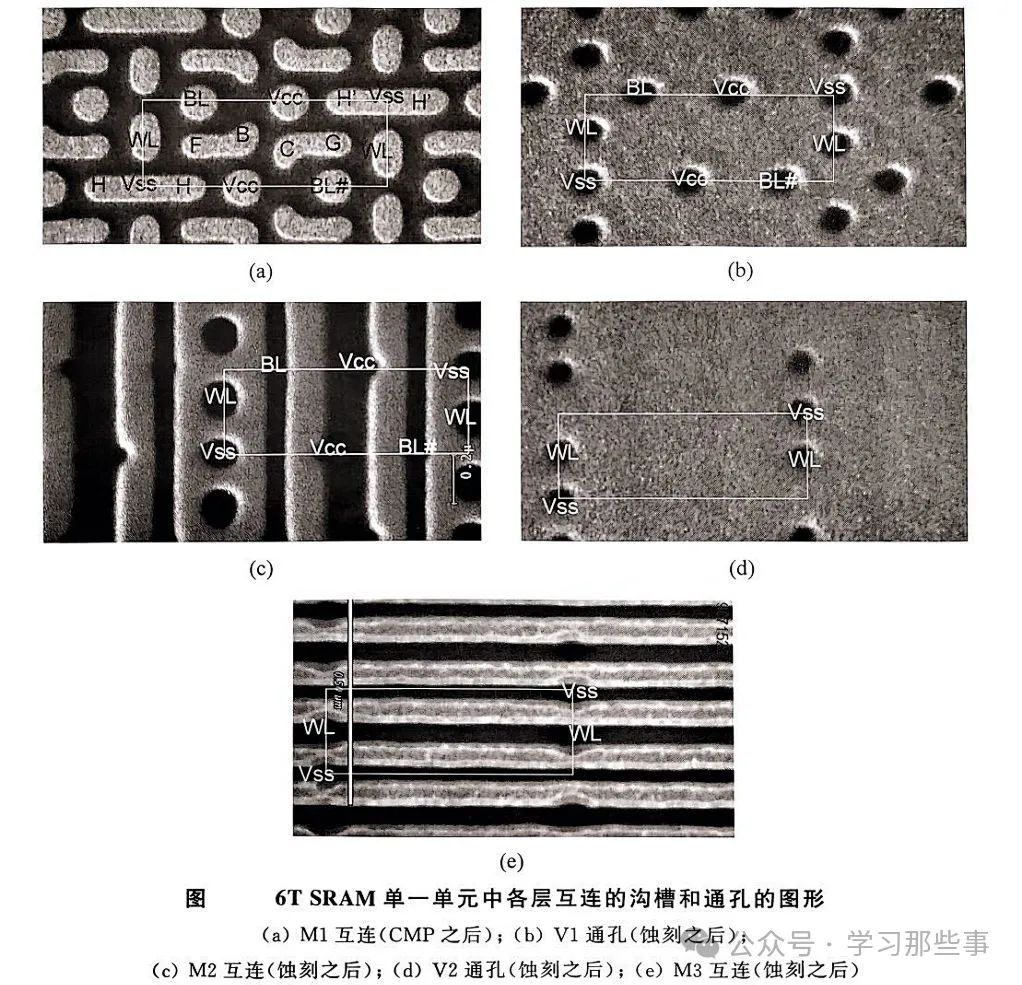

在SRAM单元的结构中,6T SRAM是一种常见的类型,由6个MOSFET构成。这些晶体管通过接触孔和各层金属层进行互连,形成存储阵列。随着集成电路尺寸的不断微缩,光刻工艺的极限成为了制约因素之一。因此,在先进工艺节点下,需要采用多层掩膜版等技术来降低图形密度,提高可制造性。同时,铜互连和双大马士革工艺等先进技术的应用也为良率的提升提供了有力支持。

失效分析

在6T SRAM良率测试完成后,为了确定失效的具体原因,需要进行失效定位(Failure Isolation)和失效分析(Failure Analysis, FA)。这一过程中,我们依赖于多种电气失效分析(EFA)和物理失效分析(PFA)的方法和技术。

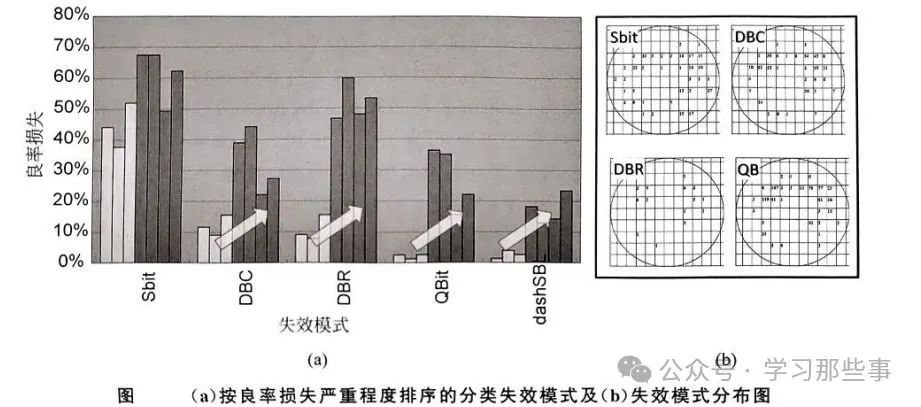

电气失效分析(EFA)是一种通过电气测试手段来定位和分类失效单元的方法。它能够帮助我们识别出SRAM阵列中所有失效的单元,并根据失效模式(Failure Mode)对它们进行分类。这些失效模式包括但不限于单比特失效(SB)、双比特列失效(DBC)、双比特行失效(DBR)、四比特失效(QB)、位线失效(BL)、字线失效(WL)以及块状区域失效(Block)。通过分析这些失效模式,我们可以对失效的原因进行初步的判断。例如,如果Vcc通孔断路,可能会导致上下两个单元失效,形成DBC模式;而如果WL通孔断路,则会导致左右两个单元失效,形成DBR模式。

为了更深入地了解失效的分布和特性,我们可以将失效模式按严重性进行排序,并比较不同晶圆间失效模式的差异。通过绘制失效模式在晶圆上的分布图,我们可以发现某些失效模式在晶圆上的特定区域更为集中。这种特殊图形的分布可以作为怀疑某些特定工艺与失效存在关联性的重要线索。

一旦通过EFA定位了失效位置,我们就可以使用物理失效分析(PFA)的方法来进一步找出失效的根源。PFA依赖于一系列高精度的物理测试手段,如聚焦离子束(FIB)、扫描电子显微镜(SEM)、透射电子显微镜(TEM)以及能量分散光谱仪(EDS)等。这些工具能够帮助我们直接观察和分析失效区域的微观结构和化学成分,从而揭示失效的根本原因。

操作实例

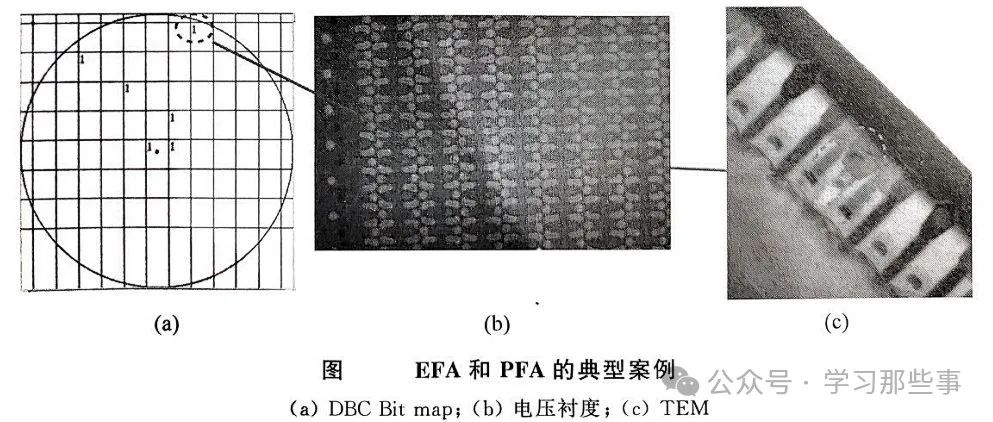

以一个典型的失效分析案例为例,通过Bitmap我们发现晶圆边缘位置存在DBC失效。

随后,我们使用电压衬度(VC)方法在M1金属层上发现了某一块金属(BL位置)在电压下发暗,与周围类似区域表现不一致。进一步切开后,剖面显示接触孔(CT)填充存在问题,这就是导致失效的根本原因。

-

集成电路

+关注

关注

5446文章

12469浏览量

372691 -

MOSFET

+关注

关注

150文章

9424浏览量

229657 -

工艺

+关注

关注

4文章

708浏览量

30114 -

逻辑集成电路

+关注

关注

0文章

3浏览量

5675

原文标题:详谈逻辑电路良率

文章出处:【微信号:bdtdsj,微信公众号:中科院半导体所】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

集成电路制造技术的应用

良率提升工程数据分析系统工具

集成电路的设计与分工

光刻胶在集成电路制造中的应用

什么是集成电路?

如何保证半导体良率

良品学习在高良率制造业中缺陷检测的应用

逻辑集成电路制造中良率提升与缺陷查找

逻辑集成电路制造中良率提升与缺陷查找

评论