高速先生成员--黄刚

这不马上就要过年了嘛,高速先生就不打算给大家上难度了,整一篇简单但很实用的文章给大伙瞧瞧好了。相信这个标题一出来,尤其对于PCB设计工程师来说,心就立马凉了半截。他们辛辛苦苦进行PCB的过孔设计,高速先生居然说设计多大的过孔他们不关心!另外估计这时候就跳出很多“挑刺”的粉丝了哈,因为翻看很多以往的文章,高速先生都表达了过孔孔径对高速性能的影响是很大的哦!咋滴,今天居然说孔径不关心了?别,别急哈,听高速先生在这篇文章中娓娓道来。首先还是要对各位设计工程师的设计表示肯定,毕竟像我们公司有非常非常多资深的设计工程师,在现在行业内动不动就二三十层的高速项目板盛行的年代,我们工程师每块都完成的非常出色。正如上篇文章《链接文章不是!让高速先生给个过孔优化方案咋就那么难吗?》所言,过孔的很多参数都影响了高速的性能。但是只要是多层板就肯定会有过孔嘛,说明工程师们对于高速过孔的设计还是非常的到位的,必须要先点个赞!

设计孔径、完成孔径和钻孔孔径这三个孔径到底一样不一样嘛?那我们先说说设计工程师接触最多的设计孔径呗。我们以一个测试板上的差分过孔的设计和仿真包括加工来给大家理清这三个名字哈!

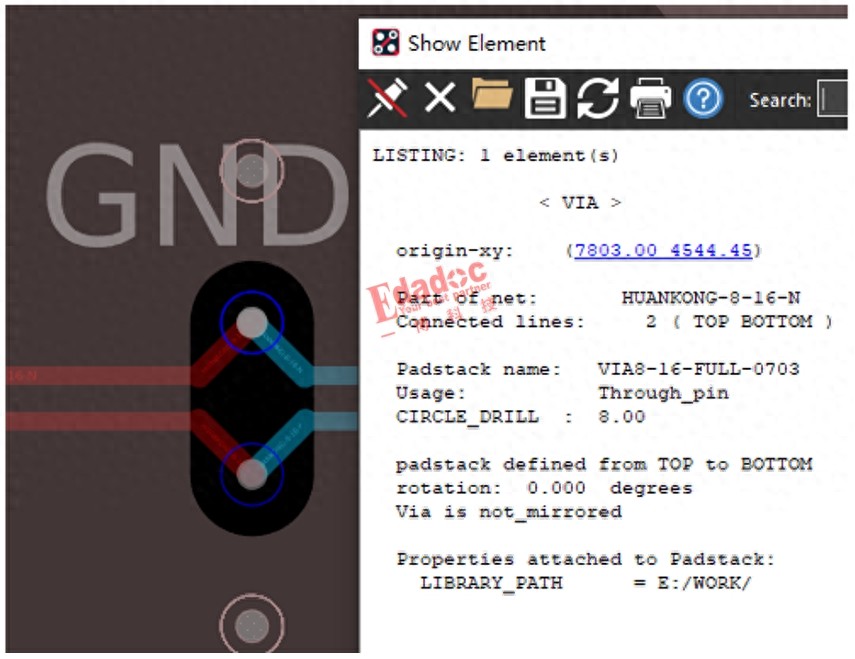

首先对于设计工程师来说,在layout版图上打的过孔的直径就称为设计孔径,就像下面这对差分设计例子一样,设计工程师打了一对差分过孔,然后去show过孔的属性,看到过孔的孔径是8mil,这个8mil就是设计孔径了。

设计孔径估计大家都知道,那么完成孔径呢?啥叫完成孔径啊,到底完成了啥?我们知道过孔用钻刀钻完之后,其实在Z方向上还不是导通的,需要在电镀这个环节把过孔孔壁镀上铜,这样就是导通的过孔。钻刀长啥样?其实就和你们平时看到的螺丝刀也大差不差,就是这样子的。

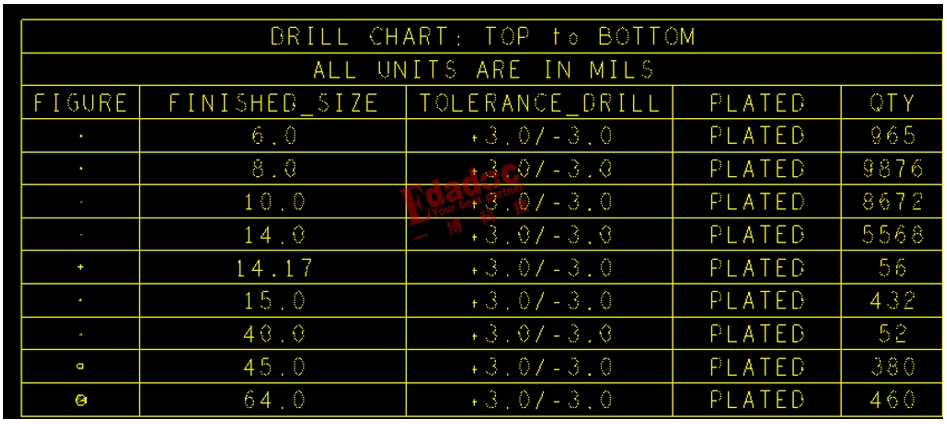

IPC的标准会告诉我们过孔电镀的厚度在0.7mil左右。所以完成孔径就是过孔电镀后的孔径了。我们也可以在设计文件输出的钻孔表上看到对完成孔径的描述。

咦,这不和设计孔径一个概念嘛!的确,对于设计工程师来说,会把设计孔径和完成孔径等同起来。就像上面那对差分过孔,设计孔径是8mil,在这个钻孔表上显示的完成孔径也是8mil。事实上,设计孔径和完成孔径其实也不是一定一样哈,加工上还是要看看电镀之后的情况,只不过我们可以认为大体一致而已。

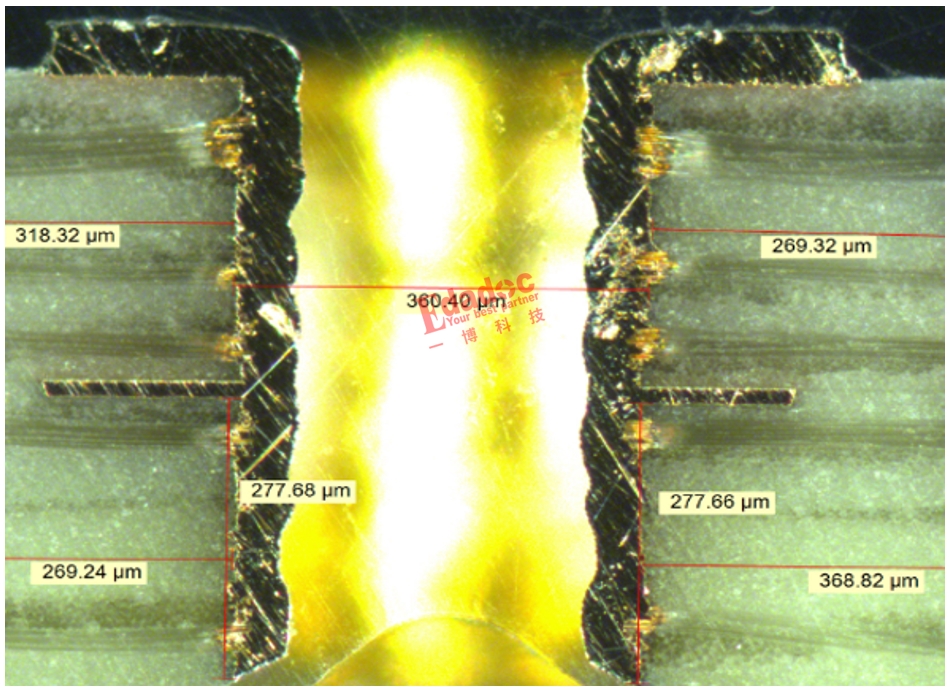

好,那最后就是钻到孔径了哈。其实上面已经说到了,那就是一开始用上面的那把钻刀钻的那一下的孔径,再说白一点,就是这把钻刀的直径了。由于钻刀钻完后要进行过孔电镀,电镀后的孔径是完成孔径,然后设计工程师又把设计孔径和完成孔径等同起来。所以孔径大小来排序的话,那就是钻刀孔径>完成孔径≈设计孔径了。下面是一张切片的过孔图,能清晰的看到钻刀孔径和完成孔径的区别。

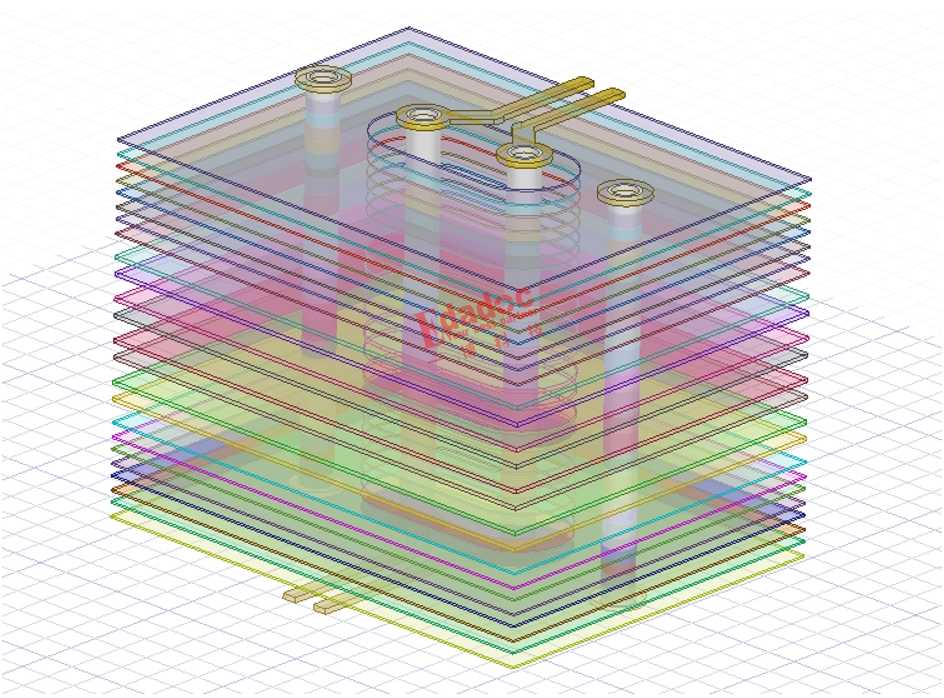

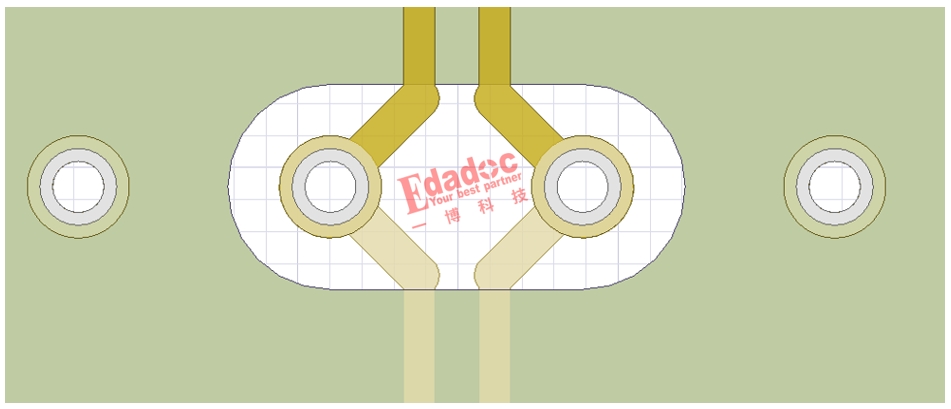

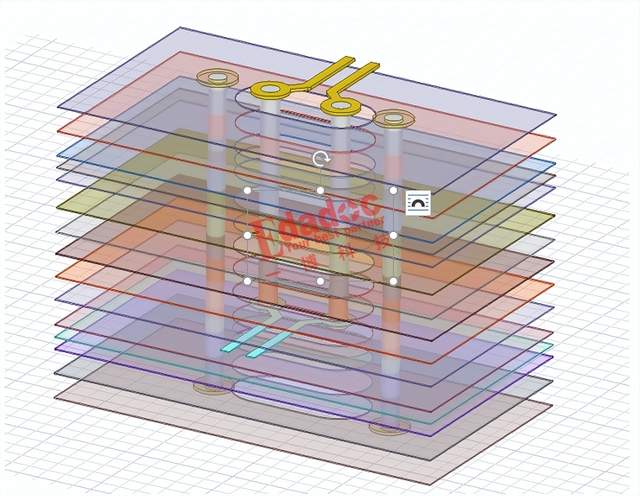

妈呀,说了那么多都没进入SI的正题啊!粉丝都不耐烦啦,纷纷等着高速先生怎么解释自己说过的设计孔径不关心这个说法啦!马上安排哈,我们把上面的这对差分过孔提取到3D模型里去,就是下面这个了。

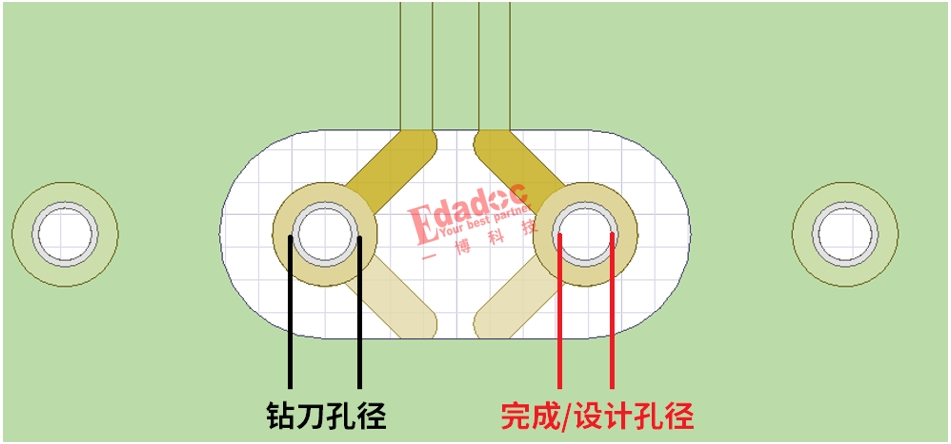

按照常规板厂的流程,如果设计工程师在版图上约束完成孔径是8mil的话,那么大部分一线的板厂会用10mil的钻刀进行钻孔,然后把电镀后的过孔做到我们要求的8mil。所以我们从俯视图就能看到钻刀孔径比完成孔径大2mil的直径。下图大家可以放大来仔细看看标注的位置哈!

为什么我们说不关心设计孔径也就是上图红色标注的直径是多大呢?我们首先对上面这个模型进行仿真,仿真结束后不急着看过孔的阻抗,先看看电磁场在过孔的分布情况。为了让大家有更直观的感受,我们把电磁场在过孔的分布结果做成一个动图,就是下面这个。

哪里是重点呢?我们可以看看蓝色的位置,也就是没有电磁场能量分布的地方。然后大家就会惊奇的发现,在过孔的内壁居然是没有能量分布的!

当然大家会惊讶是因为可能不知道一个SI的基本理论,那就是趋肤效应。用通俗易懂的话翻译就是,当传输的信号达到了一定频率之后,能量就不会像直流一样均匀分布在过孔的每个角落了,而是会慢慢集中到过孔的外表面去。哪个面算外表面呢?就是靠近回流地过孔方向的那一面。然后一定频率是多少呢?真的低到大家不信,基本上从几百MHz的低频开始,就有比较强的趋肤效应了。

既然能量都不会在过孔的内表面走,没有能量到的地方就意味着这个地方不影响过孔的性能。内表面是哪里呢?说的就是过孔的完成孔径,也就是工程师说的设计孔径的位置了。

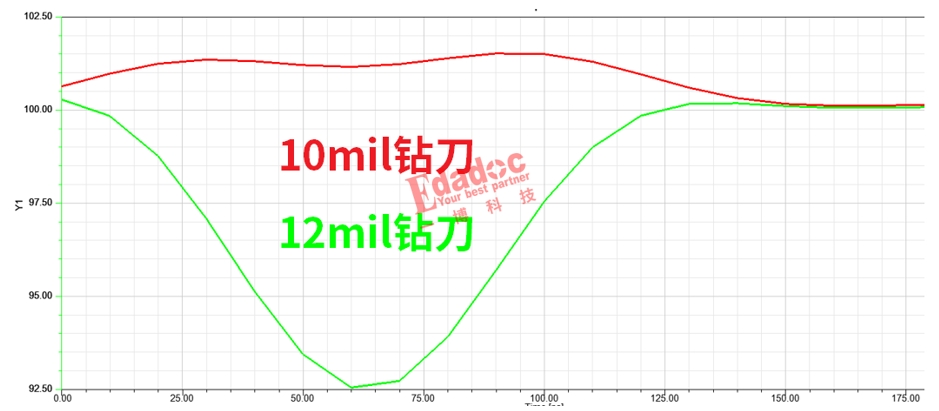

那既然能量都集中到了外表面,就不难得出结论,到底是哪个孔径对过孔的影响最大了吧。必须就是钻孔孔径了。刚刚也说了,对于8mil的设计孔径而言,大多数一线板厂会用10mil的钻刀去钻孔,如果是二线的板厂用更大的钻刀就对过孔的影响可就大了。我们再建一个模型,模拟用12mil的选钻刀去钻孔,但是同样也能电镀成8mil的完成孔径,也就是它这样搞其实也没违反我们的约束的case。

我们仿真10mil钻刀和12mil钻刀去钻孔,然后都电镀成8mil的两个过孔模型的性能。从TDR阻抗的角度上,12mil的钻孔阻抗差不多比10mil钻孔低10个欧姆!对,你没看错,有接近10个欧姆的差异!

这就是高速先生所说的我们不关心高速过孔的设计孔径的来龙去脉了。其实这个案例一方面是设计工程师不了解钻孔孔径才是对过孔产生最大影响的因素这个问题点,另一方面,对过孔的加工过程也不够了解。对于板厂来说,如果能用更大的钻刀进行钻孔,就相当于放松了加工厚径比的要求,降低了加工难度。但是从信号质量角度说,明显我们看到钻孔孔径的加大对过孔性能的影响是巨大的,因此问题就变成了板厂能不能用我们预期的更小钻刀去钻孔的问题了。所以友情提示一下,假设你们设计8mil的过孔,板厂的EQ回来写着用12mil的钻刀去钻,最后电镀成8mil,大家千万别随便同意哦!最后再加上一句哈,对于厚径比的加工要求,我们板厂是非常有信心的,有需求的粉丝可以咨询下我们板厂的加工能力哈,绝对不会让大家失望!

问题:大家知道上面说的厚径比是什么意思吗,另外有了解常规板厂的通孔厚径比大概做到什么水平吗?

审核编辑 黄宇

-

过孔

+关注

关注

2文章

223浏览量

22720 -

DeepSeek

+关注

关注

2文章

837浏览量

3392

发布评论请先 登录

泰晶科技推出625M超低抖动差分振荡器,15fs“纯净心跳”直击单波400G高速互连!

【「玩转高速电路:基于ANSYS HFSS的无源仿真实例」阅读体验】+单端信号2

隔离地过孔要放哪里,才能最有效减少高速信号过孔串扰?

PCB过孔STUB对DDRX地址信号的影响

DeepSeek R1 MTP在TensorRT-LLM中的实现与优化

PCB为啥现在行业越来越流行“浅背钻”了?

【「DeepSeek 核心技术揭秘」阅读体验】--全书概览

【「DeepSeek 核心技术揭秘」阅读体验】书籍介绍+第一章读后心得

这下真的EMO了:过孔阻抗越匹配,信号衰减反而越大!

【书籍评测活动NO.62】一本书读懂 DeepSeek 全家桶核心技术:DeepSeek 核心技术揭秘

Allegro Skill布线功能-添加差分过孔禁布区

当DeepSeek被问到:如何优化112Gbps信号过孔阻抗?

当DeepSeek被问到:如何优化112Gbps信号过孔阻抗?

评论