前面两期的芝识课堂,我们介绍了大量关于CMOS逻辑IC应用的一些细节事项,本期课堂让我们进入实际的应用案例,解决电路设计中的噪声问题。

开关噪声类型

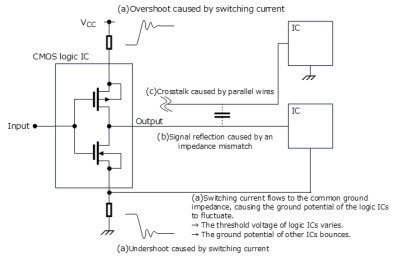

使用CMOS逻辑IC时,应注意开关噪声。主要噪声类型包括:开关噪声(过冲、欠冲、接地反弹)、信号反射串扰噪声。这些噪声是由输出转换速率(di/dt或dv/dt)和输出走线引起的。除此之外,还应注意在多种组合条件下产生的电磁干扰(EMI)噪声和附近电子设备发出的电磁敏感性(EMS)噪声。

降低开关噪声的问题

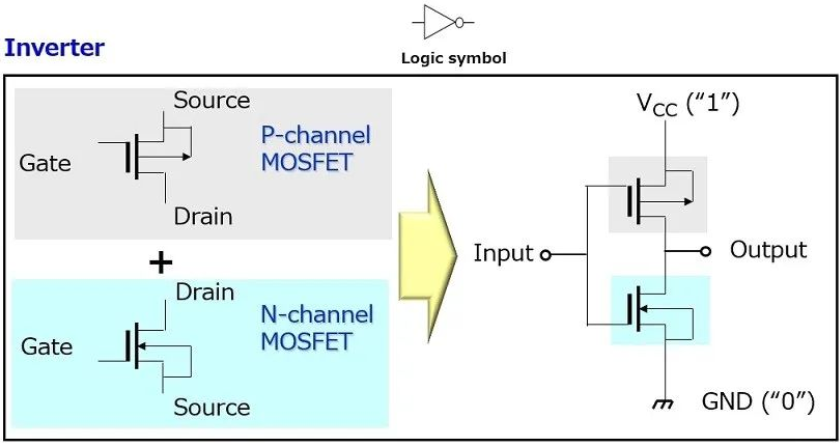

CMOS逻辑IC中的MOSFET在对内部和外部负载电容进行充放电的同时进行开关转换。开关过程中的走线阻抗可以看作是一个LCR电路。由于开关电流(i)流过电感(L),所以在CMOS逻辑IC的VCC和GND线上出现峰值电压(=L(di/dt))。这种噪声便称为开关噪声。多个同步开关输出会消耗较大的充电/放电电流,因此会产生较大的开关噪声(称为同步开关噪声)。

降低开关噪声的对策

(1)分别增加和减小VCC和GND线的宽度和长度,以减小它们的电感。

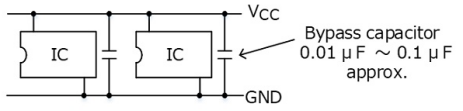

(2)将旁路电容器放置在CMOS逻辑IC的VCC和GND引脚之间并尽可能使其靠近。

(3)注意时钟和重置信号。未使用的门输入端(如驱动器)应连接到VCC或GND。将一个低通滤波器连接到使用的门输出端,以消除噪声。

(4)选择低噪声IC。

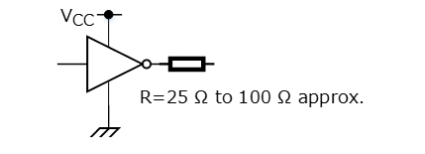

(5)在使用的门输出端添加一个阻尼电阻器。但必须检查输出波形以调整阻尼电阻器的值。

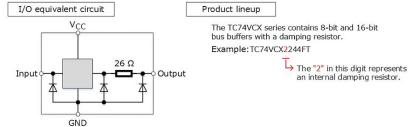

东芝为CMOS IC提供内部阻尼电阻器,这不仅有助于降低开关噪声,而且有助于减少零件数量。

信号反射的问题

对于高速CMOS逻辑IC,反射会导致信号延迟、振铃、过冲和欠冲增加。

传输线路反射:典型走线的特性阻抗(*1)为50至150 Ω。但是高速CMOS逻辑IC的I/O阻抗与典型走线的特性阻抗不同。这种阻抗的不匹配将导致一部分发射信号被反射到传输线路的发送端和接收端。

信号反射不影响缓慢上升的输出,因其上升周期与反射信号的上升周期重叠。当反射信号上升后返回到输出时,即当下列等式成立时,信号反射才会导致问题:

tr<2T

tr:输出信号上升时间

T:从传输线路的发送端到接收端的传输延迟时间

假设输出上升时间为3 ns,沿传输线路的传输延迟时间为5 ns/m。当传输线路为30 cm或更长时,信号反射会产生显著影响。

*1特性阻抗

特性阻抗是传输线路(如电路板迹线、同轴电缆)的特性之一。

传输线路特性阻抗的一般表达式是Z_0=√(L/C),其中L是单位长度的电感,C是单位长度的电容。特性阻抗的单位为欧姆(Ω)。当50 Ω的终端电阻器连接到特性阻抗为50Ω的传输线路末端时,连接点处不会发生信号反射。

如果特性阻抗与电阻值不匹配,则在连接点处会发生信号反射。

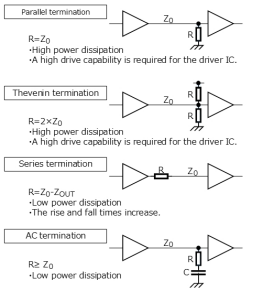

减少信号反射的对策

(1)提高电路板组装密度,减少电路板走线的长度,以减小其电感和电容。但是在这种情况下,需要注意相邻轨迹之间的串扰。

(2)不要使用输出电流高于必要值的IC。

(3)提供电气终端,以便CMOS逻辑IC的I/O阻抗与传输线路的特性阻抗匹配。

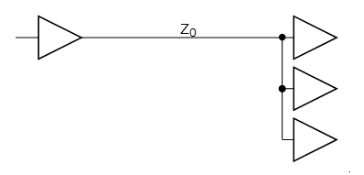

(4)当一个CMOS逻辑IC的输出驱动多个CMOS逻辑IC时,输出走线应在靠近被驱动IC的位置呈扇形展开。

串扰的问题

串扰噪声是由并行延伸的两条相邻传输线路(分别称为干扰线路和受干扰线路)之间的电容或电感耦合引起的。关于串扰,应注意快速上升或下降的信号。当此类信号通过传输线路时,串扰噪声将在相邻的线路(受干扰线路)中产生并且在与干扰信号相同的方向和与干扰信号相反的方向上同时传播。由于串扰传播的速度与干扰信号的速度相等,因此在与干扰信号相同方向上传播的串扰噪声(称为远端串扰)将显示为脉冲状噪声。

另一方面,当干扰信号沿线路传播时,沿相反方向传播的串扰噪声(称为近端串扰)保持恒定水平。串扰噪声也沿着干扰线路传播,然后返回到受干扰线路。

串扰应对措施

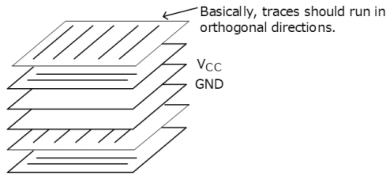

(1)在并行走线之间添加接地走线。(或者使用多层电路板,其中低阻抗层(如VCC或GND层)位于信号层之间。)

(2)减少并行运行的走线长度。

(3)如果是多层电路板,在相互正交的交替层上走线。

(4)增加走线之间的间距。

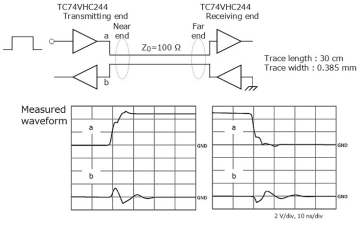

下图展示了沿30 cm走线传播的典型串扰噪声水平。这个例子显示的是近端串扰。如果受干扰走线的近端是接收端,则很容易受到串扰影响。

本篇文章,我们针对CMOS逻辑IC应用中的噪声问题做了讲解,并分享了不同噪声的应对之策。在下期文章中,我们还将继续介绍电路设计中可能出现的其他困扰及相关对策,大家不要错过哦!

关于东芝电子元件及存储装置株式会社

东芝电子元件及存储装置株式会社是先进的半导体和存储解决方案的领先供应商,公司累积了半个多世纪的经验和创新,为客户和合作伙伴提供分立半导体、系统LSI和HDD领域的杰出解决方案。

东芝电子元件及存储装置株式会社十分注重与客户的密切协作,旨在促进价值共创,共同开拓新市场,期待为世界各地的人们建设更美好的未来并做出贡献。

-

CMOS

+关注

关注

58文章

6233浏览量

243407 -

开关噪声

+关注

关注

0文章

21浏览量

11411 -

逻辑IC

+关注

关注

0文章

38浏览量

7040

原文标题:芝识课堂【CMOS逻辑IC的使用注意事项】—深入电子设计,需要这份指南(三)

文章出处:【微信号:toshiba_semicon,微信公众号:东芝半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

CMOS逻辑IC应用中的噪声问题和解决对策

CMOS逻辑IC应用中的噪声问题和解决对策

评论