产品设计的可测试性(De sign For Testability. OFT) 也是产品可制造性的主要内容从生产角度考虑也是设计的工艺性之一。它是指在设计时考虑产品性能能够检测的难易程度,也就是说设计产品时应考虑如何以最简单的方法对产品的性能和加工质量进行检测,或者产品的设计尽量能使产品容易按规定的方法对其性能和质量进行检测。尤其是电子产品的设计,对产品的性能测试是必不可少的。DFT 好的产品设计,可以简化生产过程中检验和产品最终检测的准备工作,提高测试效率、减少测试费用,并且容易发现产品的缺陷和故障,进而保证产品的质量稳定性和可靠性。DFT 设计不好的产品不仅要增加测试的时间和费用,甚至会由于难于测试而无法保证产品的质量和可靠性。所以对产品设计与测试的方法和设备相兼容的可测试性设计,是电子产品设计必须考虑的重要内容之一。

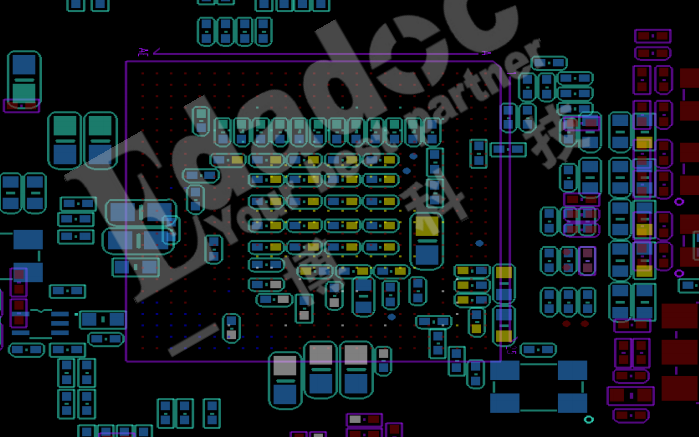

一、印制板设计的可测试性印制极设计的可测试性与可制造性同属于印制板的工艺性设计,同样包括了印制板制造及成品印制板(光板)的可测试性和印制板组装件的可测试性两个部分。这两部分的测试方法和内容完全不同,但是要在同一块印制板的设计中反映出来,对设计者来说,既需要了解印制板上需要测试的性能和方法,又要了解印制板组装件的安装测试要求和方法。对于印制板光板的测试方法和性能要求有统一的标准规定,只要查阅相关印制板的标准就可以找到。对于印制板组装件的测试,应根据电路和结构的特性和要求由设计人员通盘考虑,在布局布线时采取适当措施合理设置测试点或者将测试分解在安装工序中进行。特别是随着电子产品的小型化,元器件的节距越来越小,安装密度越来越大可供测试的电路节点越来越少,因而对印制板组装件的在线测试难度也越来越大,所以设计时应充分考虑印制板可测试性的电气条件和物理、机械条件,以及采用适当的机械电子设备。

二、印制板的光板测试印制板的光板测试是保证待安装元器件印制板质量的重要手段,也是保证印制板组装件质量和减少返修、返工及废品损失的有力措施。光板测试的质量有保证,可以提高印制板的安装效率、降低成本。如果光板的质量不能保证,待印制板安装后再发现板的质量问题时需要拆下元器件,不但费工费时而且可能要损坏元器件,其时间和经济的损失更大。所以在国内外的电子行业都非常重视对印制板各项性能的测试,制定了许多检测标准和方法。主要的检测项目有外观检测、机械性能测试、电气性能测试、物理化学性能测试和可靠性(环境适应性)测试等方面。印制板光板的测试项目很多,但对设计的限制较少。外观检测一般是在成品印制板上通过目检或适当的光学仪器进行检测,主要是检查制造的质量,外观检测对设计的可测试性要求不多。在这些性能的测试中受印制板设计布局布线影响强大的是电气性能测试,它包括耐电压、绝缘电阻、特性阻抗、电路通断等测试项目且测试点设计应符合测试要求。与设计的可测试性关系最大的是电路通断测试,而该项测试又是保证印制板质量的关键性能需要对每块印制板进行l00%的逻辑通断测试。所以进行印制板设计时。应考虑测试时可能采用测试设备的测试探头与测试电路物理尺寸的匹配问题。否则将会由于印制板上被测点的位置和尺寸误差。引起测试的差错或测试的可重复性差的问题。对于有破坏性的机械、物理、化学性能测出一般采取从同批产品中抽样或设计专用的试验板或附连试验板按标准进行试验和评定。设计时应当熟悉测试板和附连试验板的设计及测试要求和方法。三、印制板组装件的测试性印制板组装件的测试是指对安装了元器件后的印制板进行的电气和物理测试。影响印制板组装件测试的困难很多,其检测的方法要比印制板的光板检测复杂得多。对组装件的可测试性设计应包括系统的可测试性问题。系统的可测试性功能要求应提交整机总体设计的概念进行评审。印刷板组装件可测试性必须与设计的集成、测试和维护的完整性相兼容。PCB组装件的可测试性在设计开始之前。应同印制板的制造、安装和测试等技术人员进行评审。以保证可测试性的效果。评审的内容应涉及电路图形的可视程度、安装密度、测试操作方法、测试区域的划分、特殊的测试要求以及测试的规范等。

PCB组装件级的测试主要有两种类型,一种是对有独立电气功能的组装件进行功能测试,在组装件的输入端施加预定的激励信号,通过监测输出端的结果来确认设计和安装是否正确。另一种测试是对组装件进行光学检测和在线测试,光学检测对设计没有明确的制约,只要保持电路有一定的可视性就可以检测,该法主要检查安装和焊接的质量。在线测试对印制板的限制主要是测试点应设计在坐标网格上能与测试针床匹配的地方,并且能在焊接面测试。如果用飞针测试,则既要保证测试点位于坐标网格上,又要在布局时保持有足够的空间能使探头(飞针)撞触被测试点,飞针测试可在板的两面进行,主要检测组装焊接质量和加工中元器件有无损坏。常用的测试方法有人工检测和仪器自动测试。人工测试通过万用表、数字电压表、绝缘电阻测试仪等仪器进行检测,效率低、记录和数据处理复杂,并且受组装密度的限制,小型化的高密度组装的印制板难于靠人工检测。自动化仪器检测具有精度高、可靠性好、重复性好、效率高的特点并且有的仪器还具有自动判定、记录、显示和自动故障分析的能力。常用的自动化测试技术有自动光学检测(AOD)、自动X 射线幢测(AX I)、在线测试(ICT) 和功能测试等。在印制板设计时就应考虑印制板组装件的测试兼容性,如果不考虑采用的测试方法和必要的测试机械规则即使在电气方面具有良好的可测试性电路在印刷板组装件上也比较难于测试,如测试点的位置、大小以及测试点的节距与测试探头或针床的匹配问题。在线测试时电气条件设置问题、防止测试对元器件的损坏等都是测试性要考虑和解决的问题。

-

pcb

+关注

关注

4418文章

23979浏览量

426274 -

可测试性

+关注

关注

0文章

9浏览量

7924

原文标题:PCB设计的可测试性概念

文章出处:【微信号:pcbworld,微信公众号:PCBworld】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

PCB设计的ESD抑止准则解析

PCB设计有哪些误区PCB设计的十大误区上部分内有下部分链接

PCB设计的可测试性的2个部分解析

PCB设计的可测试性的2个部分解析

评论