在电子信号的精密传输领域,阻抗匹配扮演着至关重要的角色。当信号在传输过程中遭遇阻抗不匹配时,就如同水流在管道中遇到了障碍,不可避免地会产生反射现象。这种反射不仅会导致合成信号出现过冲,使信号波形在逻辑门限附近波动不定,更可能引发信号完整性受损,影响系统的整体性能。

要消除因阻抗不匹配而引发的反射问题,根本途径在于实现传输信号的阻抗良好匹配。这意味着,我们需要精心设计电路,使得负载阻抗与传输线的特性阻抗之间的差异尽可能缩小。因为,阻抗差异越大,反射现象就越严重。同时,我们还需密切关注PCB上的传输线设计,避免出现突变或拐角等可能导致阻抗不连续的因素。只有保持传输线各点阻抗的连续性,才能有效减少在传输线各段之间可能出现的反射现象。

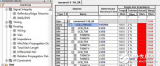

在高速PCB布线领域,为了实现良好的信号阻抗匹配,我们必须严格遵循一系列布线规则。以USB布线为例,要求USB信号采用差分走线方式,线宽设定为10mil,线距保持6mil,同时地线与信号线的距离也需控制在6mil。这样的布线设计能够有效减少信号间的串扰,提高信号传输的稳定性和可靠性。

对于HDMI布线而言,同样要求采用差分走线方式,线宽和线距的设定与USB布线相似,但每两组HDMI差分信号对的间距需超过20mil。这样的布线规则旨在进一步降低信号间的相互干扰,确保HDMI信号的高质量传输。

LVDS布线则要求信号采用差分走线方式,线宽设定为7mil,线距保持6mil。这样的布线设计旨在控制HDMI的差分信号对阻抗达到100+-15%欧姆的标准范围内,从而确保信号的稳定传输和接收。

在DDR布线方面,对于DDR1而言,走线时要求信号尽量不走过孔,保持信号线等宽且等距。同时,走线必须满足2W原则,以减少信号间的串扰。而对于DDR2及以上的高速器件而言,除了要求高频数据走线等长以实现阻抗匹配外,还要求信号线在布局上更加精细和合理,以确保信号在高速传输过程中的稳定性和可靠性。

良好的信号阻抗匹配是优化电子信号传输质量、提升系统稳定性的关键所在。通过精心设计电路、遵循严格的布线规则以及关注传输线各点阻抗的连续性等措施的实施,我们可以有效消除因阻抗不匹配而引发的反射问题。

-

lvds

+关注

关注

2文章

1240浏览量

70207 -

PCB布线

+关注

关注

22文章

473浏览量

43647 -

高速PCB

+关注

关注

4文章

103浏览量

25765 -

信号阻抗

+关注

关注

0文章

4浏览量

1371

发布评论请先 登录

PCB设计高速差分信号的布线技巧

高速PCB设计中的阻抗匹配

高速PCB布线技巧、EMI问题、设计规则

高速PCB信号布线的设计规范

高速PCB中的阻抗匹配

高速PCB布线中信号阻抗不匹配的原因

高速PCB布线中信号阻抗不匹配的原因

评论