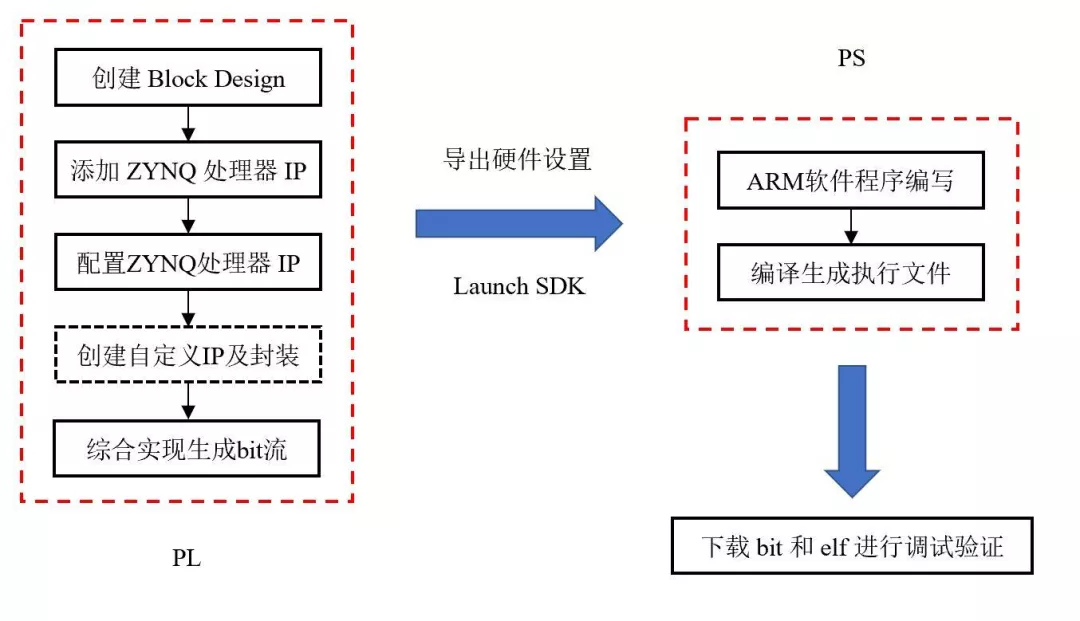

在电子系统设计中,无任是用CPU作为系统的主要器件,还是用FPGA作为系统的主要器件,系统设计中首先要考虑到的问题就是处理器的启动加载问题。 XILINX推出的ZYNQ可扩展处理平台,片内包括两个高性能的ARM Cortex A9硬核(称为处理系统processing system (PS))和FPGA(称为可编程逻辑programmable logic (PL)),在基于该平台的系统设计时具有极大的灵活性,本文就ZYNQ系统设计时都会遇到启动加载问题作一个抛砖引玉的描述,如有不当之处还请高手斧正。

一、器件配置单元

ZYNQ器件都带有一个器件配置单元(device configuration unit (DEVCFG) ),该模块由PS控制,提供软件控制下的PS和PL的初始化和配置功能。以前单个FPGA器件提供的下载方法已经不在适用,PL的配置下载必须在PS的参与下进行。

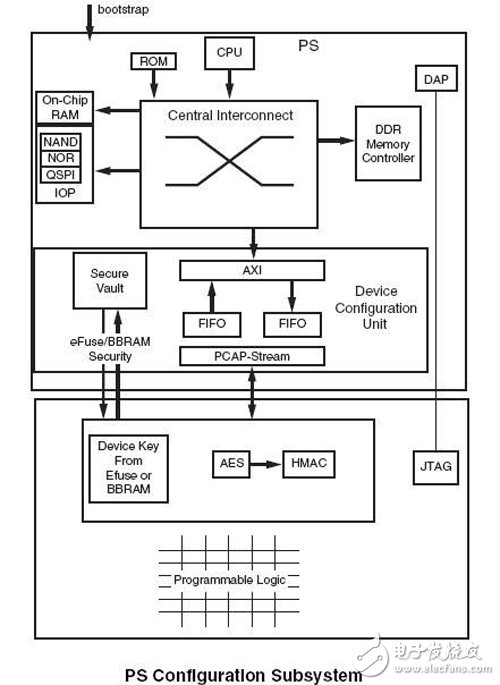

Zynq-7000的器件配置单元包括下面的PS单元:

① CPU

② OCM(引导ROM和共享RAM)

③ 部分顶层总线和外设

④ PS器件配置模块

在PL侧,下面的单元也将参与:

① PLS器件配置逻辑和接口

② 解密/鉴权硬件

③存储在eFUSE单元或者电池备份RAM(BBRAM)内的解密密钥

下图为PS器件配置子系统框图:

提供的关键特性如下:

A.提供3种不同的PS配置方法,包括2种主模式和1种从模式。

① 加密主模式

② 非加密主模式

③ 非加密从模式

B.3种不同的主模式启动源

① NOR FLASH

② NAND FLASH

③ QSPI FLASH

C:JTAG非加密从模式

D:用AES-256和HMAC (SHA-256)进行PS/PL的加密下载

E:高速配置用的主DMA接口

F:100 MHz 32-bit PCAP流接口

H:SoC加密调试功能

在系统上电复位时,PS采样专用bootstrapping signals引脚电平来决定从什么方式引导器件。这个引导过程是由一个Cortex A9核执行片内的ROM code实现的,ROM code的功能是初始化L1 cache和基本的总线系统,加载相应的NAND, NOR, Quad-SPI, and PCAP驱动,从指定接口加载第一级BOOTLOADER(the first stage boot loader (FSBL))到片内执行。由于OCM RAM大小有限制,第一级BOOTLOADER大小最大为256KB。用户只需要按要求提供启动映像和设置正确的bootstrapping signals引脚电平,系统上电复位时由ROM code自动加载到片内并且程序调转到启动映像,此时系统的全部控制功能交由用户的启动映像控制,用户如要实现的第二级BOOTLOADER功能由启动映像的程序实现。

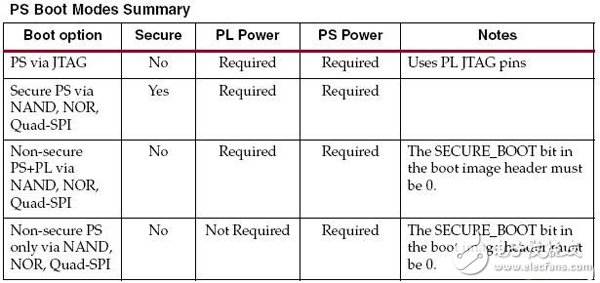

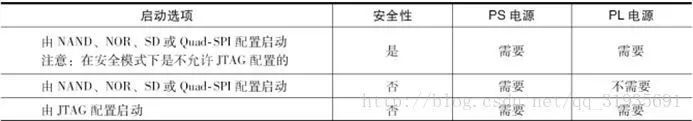

对于加密配置方法,需要用到AES-256解密代码和SHA-256签定(签名)算法, PS需要用PL内硬连线的AES-256 和SHA-256模块,这时就要求在加密配置情况下PL就必须上着电,既使系统并不配置PL部分也需上电。器件的加密密钥可以由用户选择是存储在片内的eFUSE单元(具有掉电非易失性)或者内部电池供电的BBRAM内(具有掉电易失性,适用于安全级别要求更高的场合), 下表总结了配置模式和相关信息:

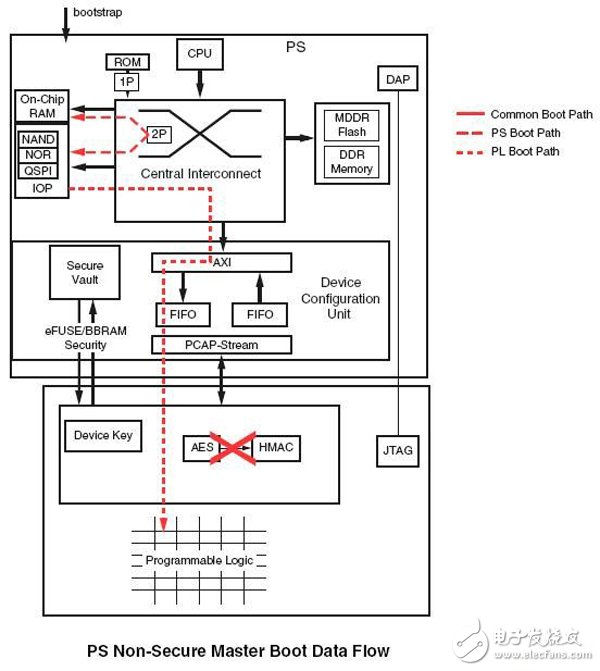

二、PS非加密主模式配置过程

这种模式下PS启动映像是直接从外部非易失存储器(NAND, NOR, Quad-SPI)内加载到片内OCM内,随后PL映像可以直接配置到PL内,整个过程如下图示:

PL映像的配置可由配置接口模块用DMA来高速实现,在非加密情况下速度可以达到400MB/s, 加密情况下速度可以达到100MB/s, 这在FPGA需要部分重配置时十分有用。

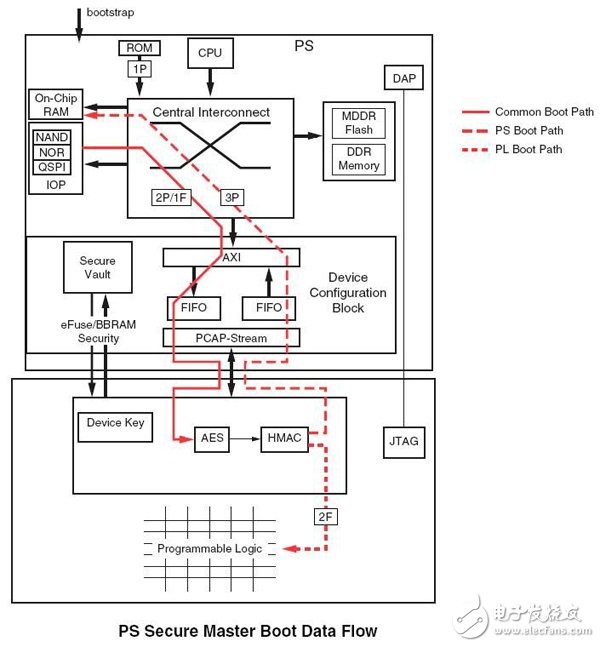

三、PS加密主模式配置过程

PS加密主模式用到了位与片内PL部分的硬件AES-256解密模块和SHA-256模块来对PS启动映像进行解密和完整性鉴定,器件密钥存储在片内的eFUSE单元或者内部BBRAM内,当PS加载成功后,用户可以选择用下面缺省的PL引导过程来配置PL部分,如下图示:

其中配置PL时的比特流既可以是已经经过AES-256加密的比特流,也可以是先经过PS先进行解密后成为明文比特流送到PL内,这个过程的保密性由用户选择使用。

在保密ROM引导阶段如果PS完整性鉴定失败,CPU就立即断言PROG_B信号而清除PL内容,同时发出一个加密复位信号,这使PS内部的RAM和寄存器进行复位,然后CPU进入睡眠模式,系统只有重复上电才能复位。PL配置发生在BOOT的第二阶段,这个过程完成可以由用户选择自己的方法在任何时间内来配置一次或多次,并不需要一定按缺省的PL引导过程来配置PL部分。

四、启动模式引脚

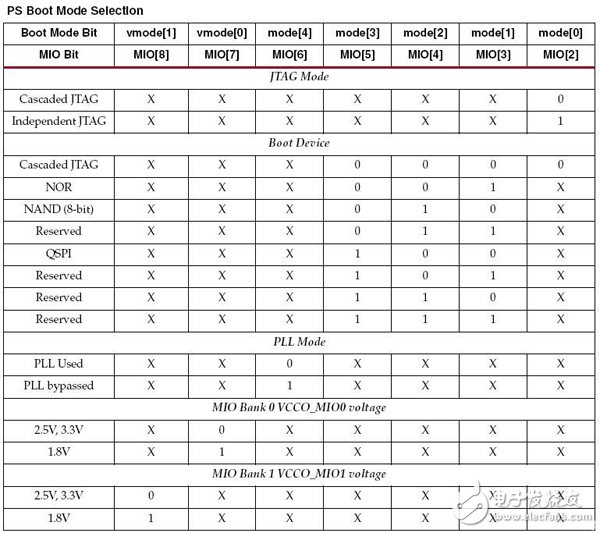

ZYNQ器件有5个启动模式信号mode[4:0],用来指出从哪里启动,是否是JTAG模式,PLL是否旁路等。另外有两个电压模式信号vmode[1:0]用来指明MIO BANK的电压模式,vmode[1:0] 信号和mode[4:0] 信号通过上拉和下拉来确定电平值,上拉和下拉电阻建议为20k欧姆,上拉是连接到VCCO_MIO0电压,下拉是连接到地。系统在释放PS_POR_B复位脚后这些启动模式引脚信号会被采样3个PS_CLK时钟用来确定启动方式。vmode[1:0] 信号和mode[4:0] 信号对应的I/O管脚为MIO[8:2],各信号具体含义如下:

① Mode[0] 用来指明是否是JTAG 模正。

② Mode[3:1]用来选择启动源,是从NOR Flash还是从NAND Flash还是从QSPI启动。

③ Mode[4]用来使能PLL。

④ Vmode[1:0] 用来配置I/O BANK电压。

这些信号和MIO管脚的对应关系如下表表示:

注:上表中X表示不关心。

实际设计中,由于MIO管脚数量有限(只有54个),且只分为两个BANK(MIO Bank 0对应管脚为PS_MIO[15:0],PS_CLK,PS_POR_B;MIO Bank 1对应管脚为PS_MIO[53:16],PS_VREF_MIO和PS_SRST_B),并不建议系统设计为从并行的NOR Flash启动,因为这种方式NOR Flash占用的MIO管脚数量大多(大于40个管脚),系统设计为从NAND Flash或QSPI启动都可以,这两种方式占用的MIO管脚数量要少些,NAND Flash的优点是容量比较大,缺点是读写速度要慢些(典型速度 10MB/s), QSPI也是一种NOR Flash,不过接口是四线串行接口,可以获得比较高的读写速度(典型速度 50MB/s),如果系统希望从其它方式如USB, Ethernet, SD/SDIO等方式启动,这都需要用户在第一级启动映像内自行设计启动引导代码。

-

PS

+关注

关注

0文章

73浏览量

37250 -

Zynq

+关注

关注

10文章

625浏览量

49239

发布评论请先 登录

详解Zynq的两种启动模式

通过JTAG启动Linux的方法和脚本

Zynq在非JTAG模式下的启动配置流程

ZYNQ器件的启动配置方法

ZYNQ 7系列FSBL的启动过程与配置方法

Xilinx FSBL如何操作启动Zynq器件

Zynq的启动与配置过程详解

如何在 Vitis 中调试 Zynq UltraScale 器件启动镜像

一文详解ZYNQ器件的启动配置方法

一文详解ZYNQ器件的启动配置方法

评论