一、启动流程介绍

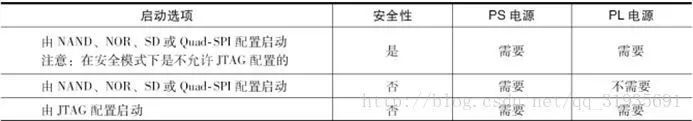

普通的 FPGA 一般是可以从 flash 启动,或者被动加载,但是ZYNQ不行,ZYNQ必须PS端参与

ZYNQ 的启动是由 ARM 主导的,包括 FPGA 程序的加载, ZYNQ 启动一般为3个阶段,最少2个阶段:

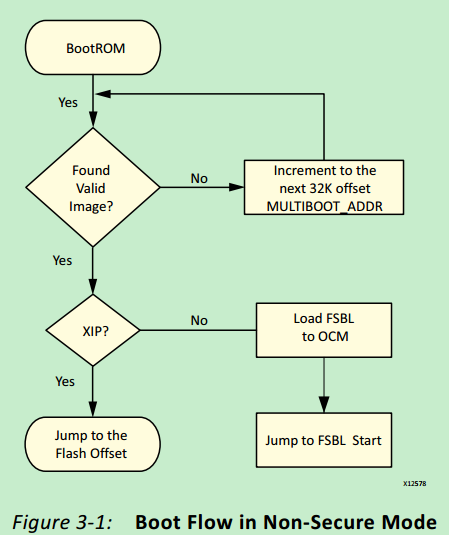

1、阶段0:Stage-0 Boot (BootROM)

阶段0,主要是运行芯片内部固化的BootROM程序,这个BootROM主要是识别启动模式(spi/sd/nand/nor/)是哪一种?

1)、根据启动模式,设置相应的外设,当然有引脚复用了,还有时钟;

2)、将FSBL从启动介质中搬移到OCM(On-Chip Memory)中

3)、跳转到FSBL处执行,将控制权交给FSBL程序

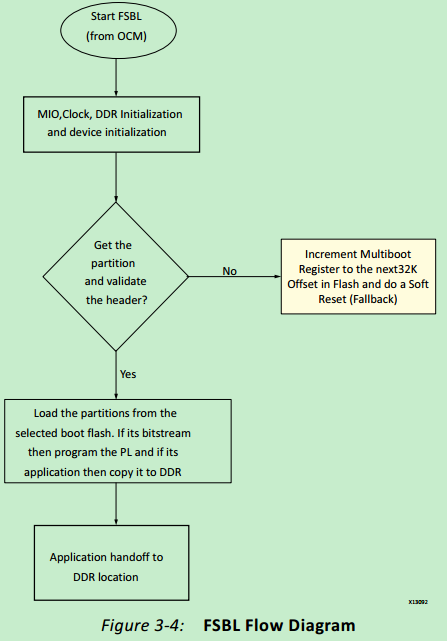

2、阶段1:FSBL(First Stage Bootloader )

FSBL(第一阶段引导加载程序)在BootROM之后启动,这个BootROM将FSBL加载到OCM(On-Chip Memory )

FSBL负责下面的几项工作:

1)、初始化PS端的配置数据(使用Xilinx硬件配置工具提供的);

完成MIO分配、时钟PLL、DDR控制器初始化,SD、QSPI控制器初始化

2)、通过启动模式从启动介质读取bitsttream文件,并用它烧写PL端程序

3)、加载第二阶段BootLoader或者逻辑代码到DDR内存

4)、切换到第二阶段BootLoader或者逻辑代码运行

下图是一个简单的FSBL流程图:

3、第二阶段启动流程:Second Stage Bootloader

第二阶段引导加载程序是可选的,并由用户设计,一般是在跑系统的情况下使用,比如 linux 系统的u-boot(用petalinux 工具制作 linux 系统 )

二、制作FSBL第一阶段的启动代码

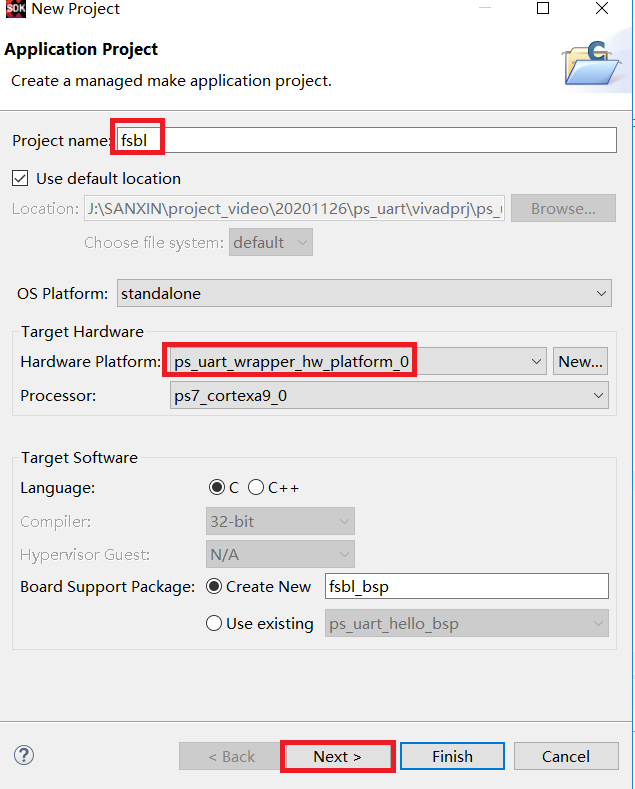

1、新建一个名为 fsbl 的 APP,特别注意硬件平台选择我们自己配置的ps_uart_warpper_hw_platform_0 ,点击next

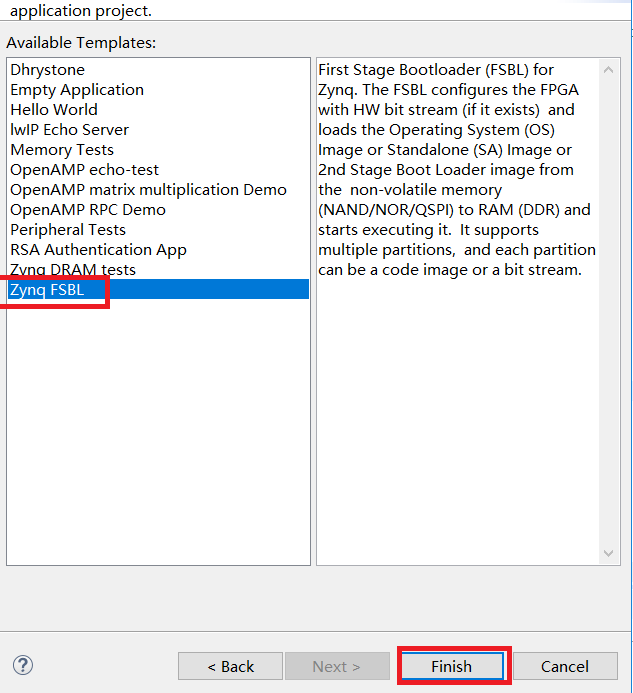

2、在弹出的对话框选择Zynq FSBL,点击Finish

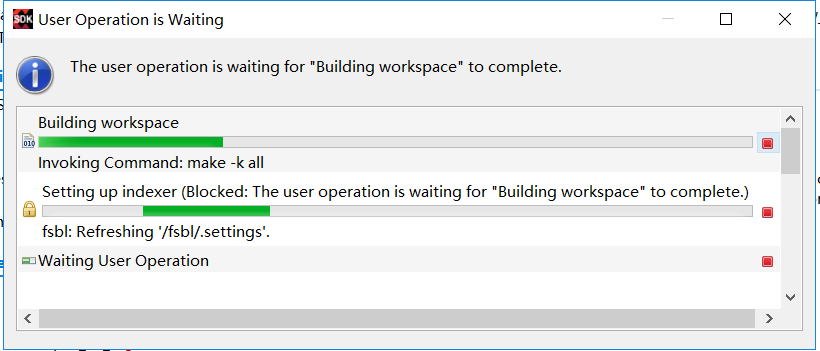

3、然后软件会自动的进行编译FSBL,时间看电脑的性能

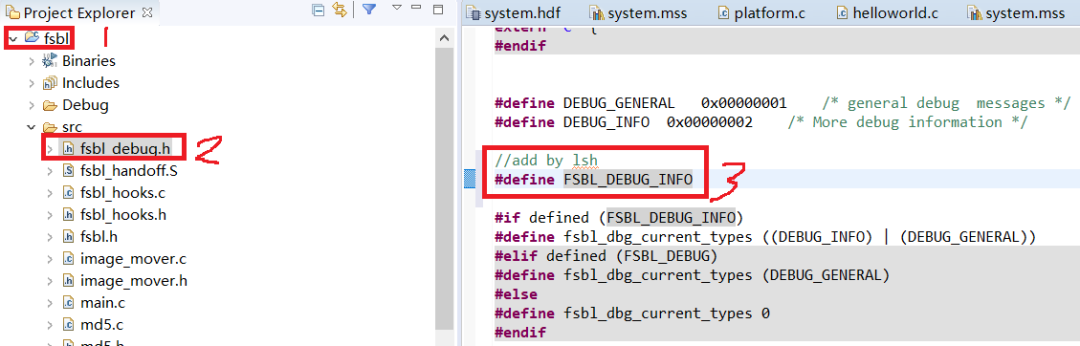

4、等编译完成,修改代码,添加调试宏定义 FSBL_DEBUG_INFO

这个宏可以在启动输出 FSBL 的一些状态信息,有利于调试,但是会导致启动时间变长。

5、修改后保存, SDK 默认会自动编译,生成 fsbl.elf 文件。也可以右键点击build project手动编译

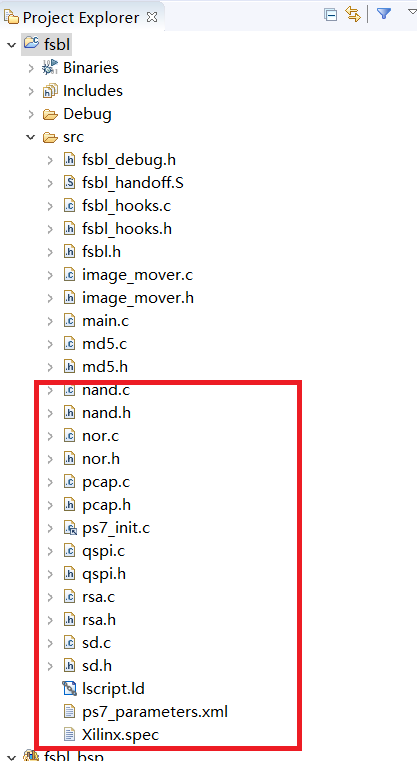

6、我们的工程文件夹包含很多外设文件ps7_init.c, nand, nor, qspi, sd 等

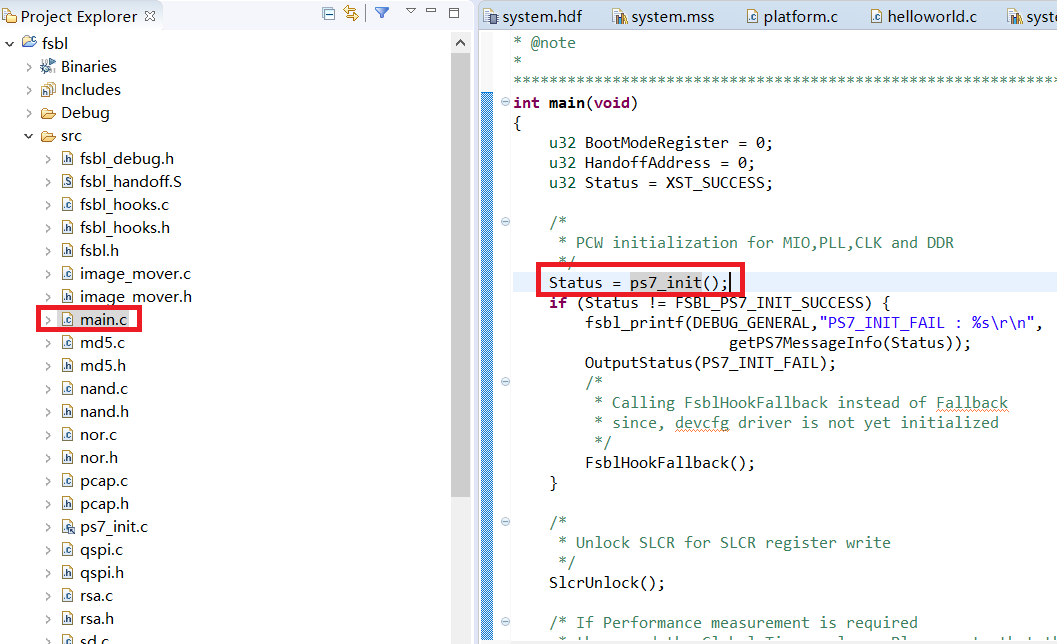

7、fsbl的 main.c 中,第一个运行的函数就是 ps7_init ,这个fsbl内容也可以根据自己需要进行更改,例如加点自己的打印信息

8、创建 BOOT 文件

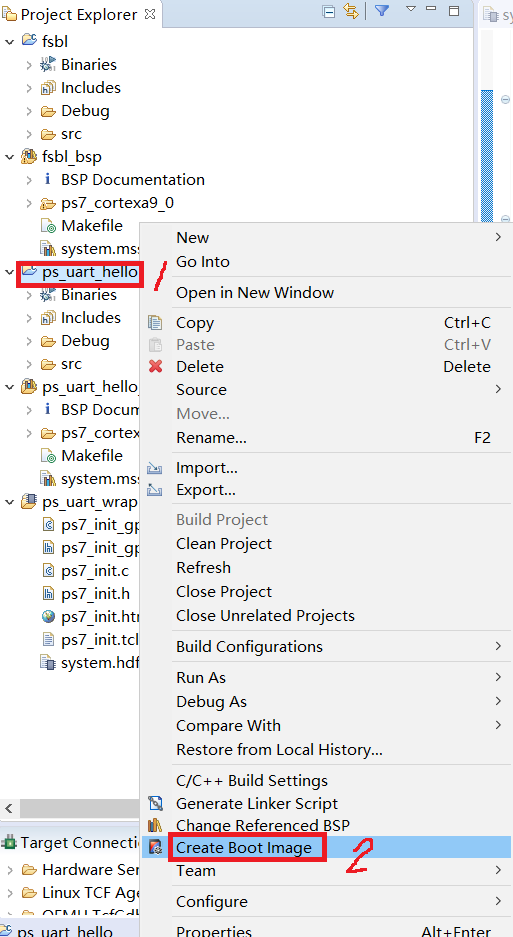

8.1、选择 APP (就是我们的应用:ps_uart_hello)工程,右键选择 Create Boot Image

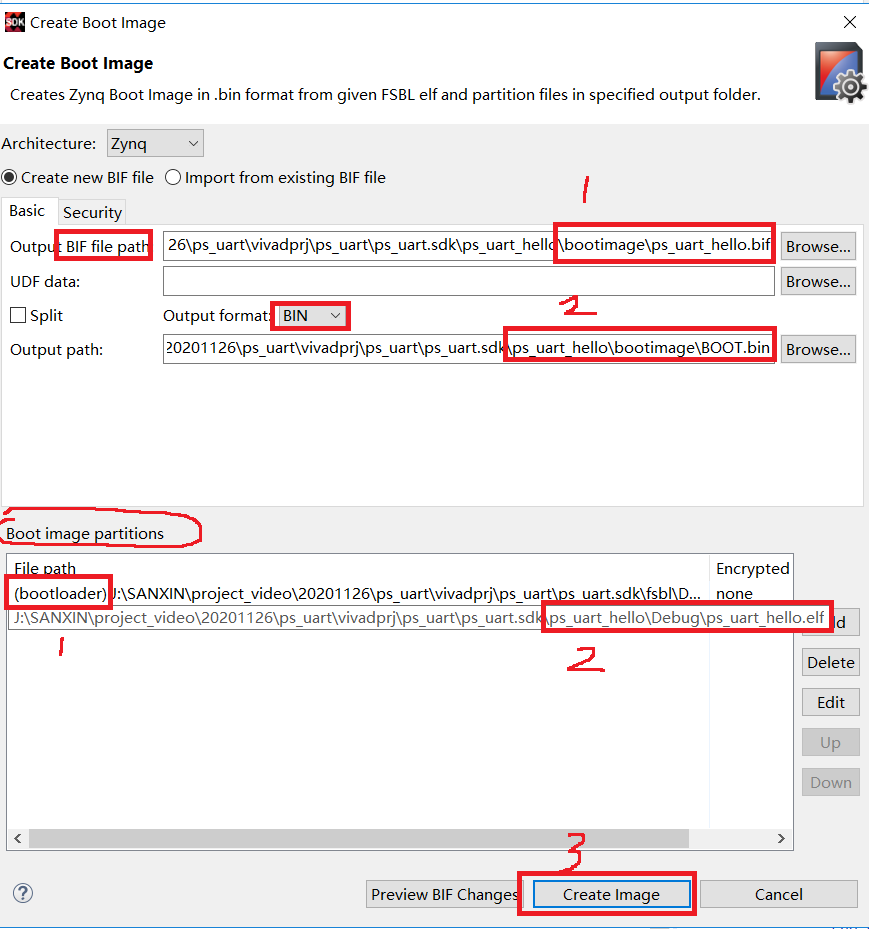

8.2、在弹出的对话框中可以看到BIF文件和BOOT.bin的生成路径

BIF文件是生成BOOT.bin文件的配置文件;

BOOT.bin是我们需要的启动文件,可以烧写到SD卡、QSPI里

8.3、在弹出的对话框,Boot image partitions 列表中有要合成的文件

第一个文件一定是 bootloader 文件,就是上面生成的 fsbl.elf 文件;

第二个文件是 FPGA 配置文件 bitstream,本实验没有PL端程序,所以bitstream,不需要添加;

第三个是应用程序,在本实验中为 ps_uart_hello.elf

8.4、由于没有 bitstream,在本实验中只添加 bootloader 和应用程序。点击 Create Imag

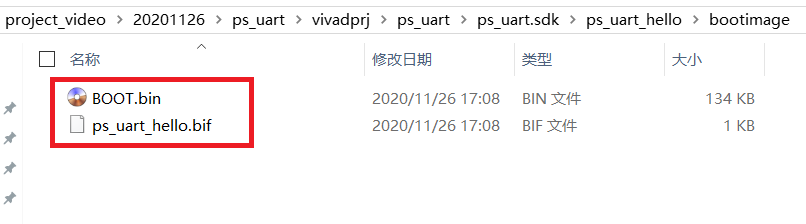

8.5、在生成的目录下可以找到BOOT.bin文件

三、SD卡烧写及测试

1、格式化 SD 卡,只能格式化为 FAT32 格式,其他格式无法启动

2、放入 BOOT.bin 文件,放在根目录

3、D 卡插入开发板的 SD 卡插槽

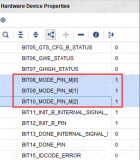

4、启动模式调整为 SD 卡启动

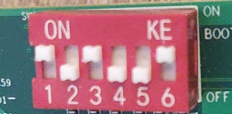

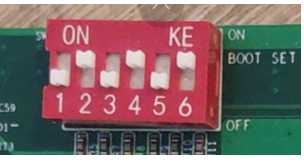

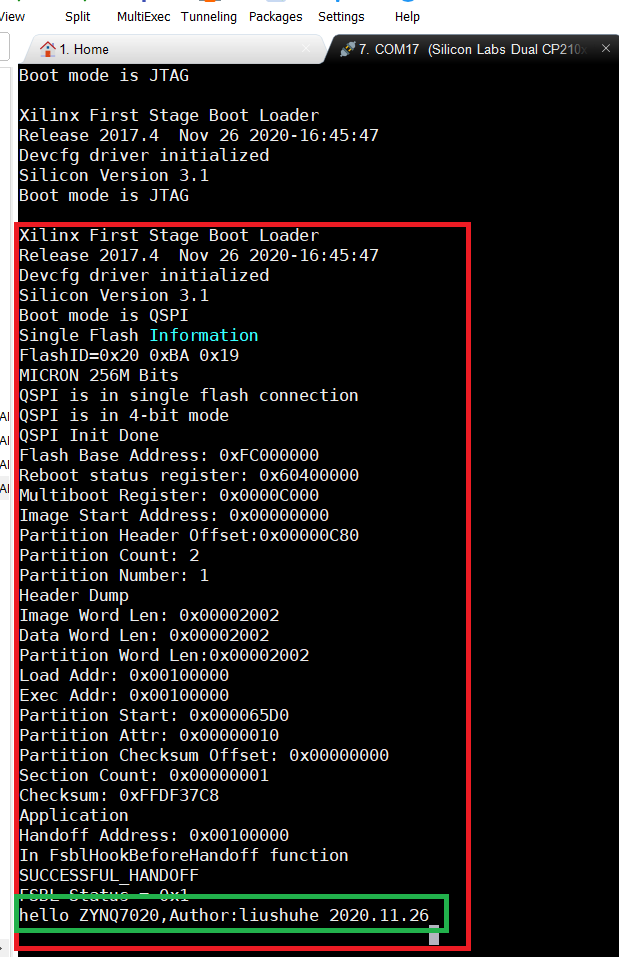

开发板设置拨码为【 101001(1~6 SD卡 模式)】

5、打开串口,开发板上电

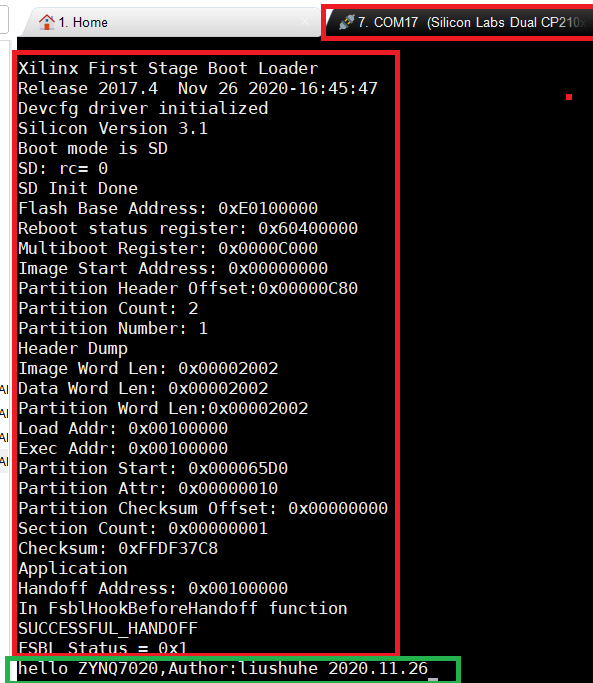

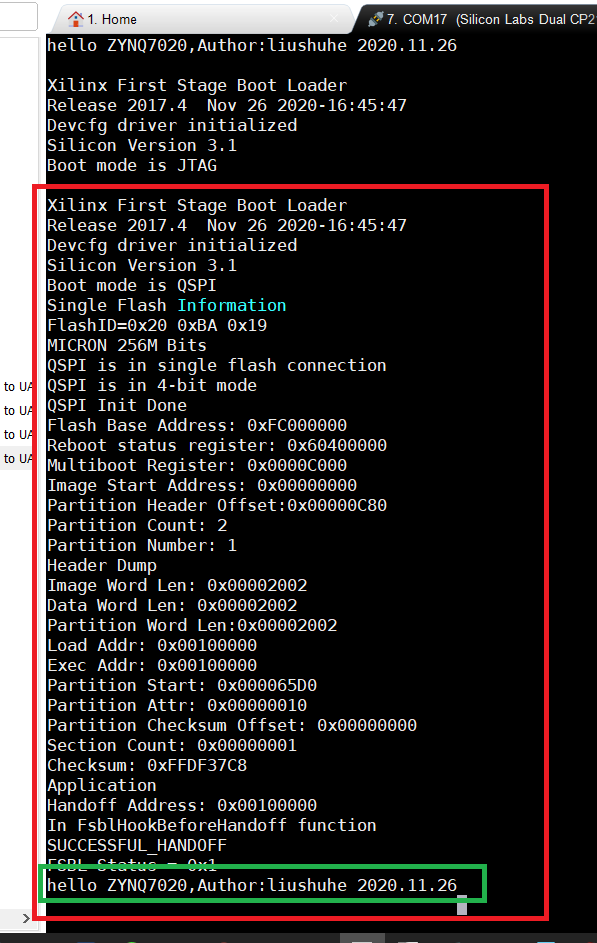

6、可以看到SD卡启动成功,红色部分为FSBL打印信息,绿色为我们的APP打印信息

7、SD卡固化成功

四、QSPI程序固化

QSPI 烧写有2种方式:xSDK软件烧写、或者Vivado软件烧写

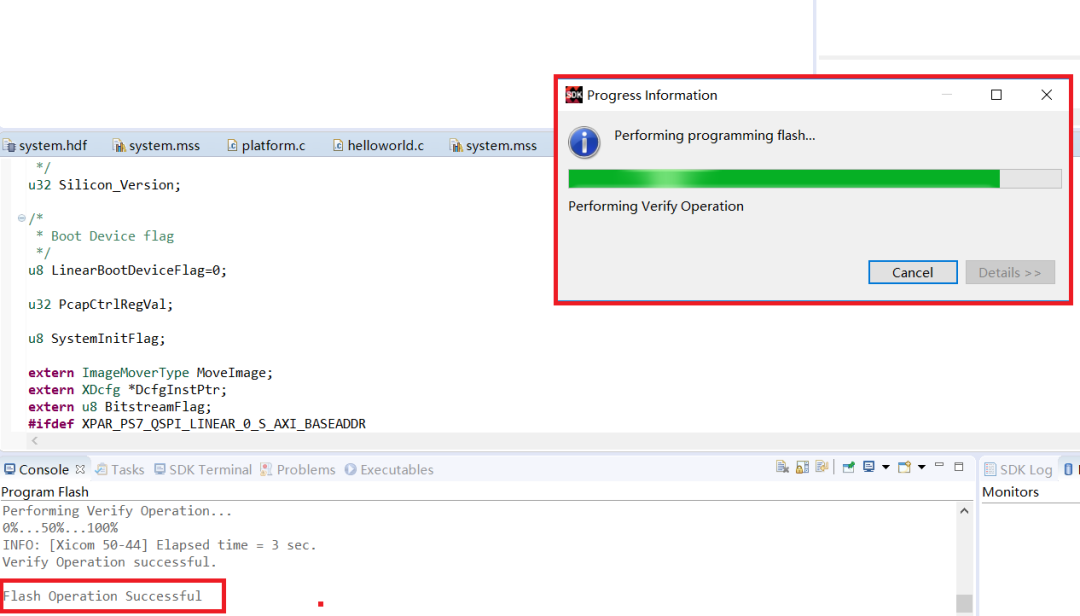

五、QSPI烧写及测试(xSDK软件烧写)

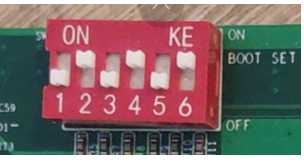

首先将开发板设置为JTAG模式【 010101(1~6 JTAG 模式)】

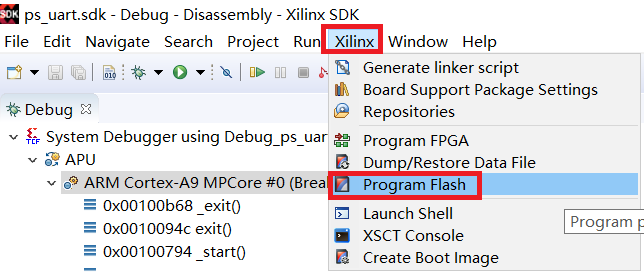

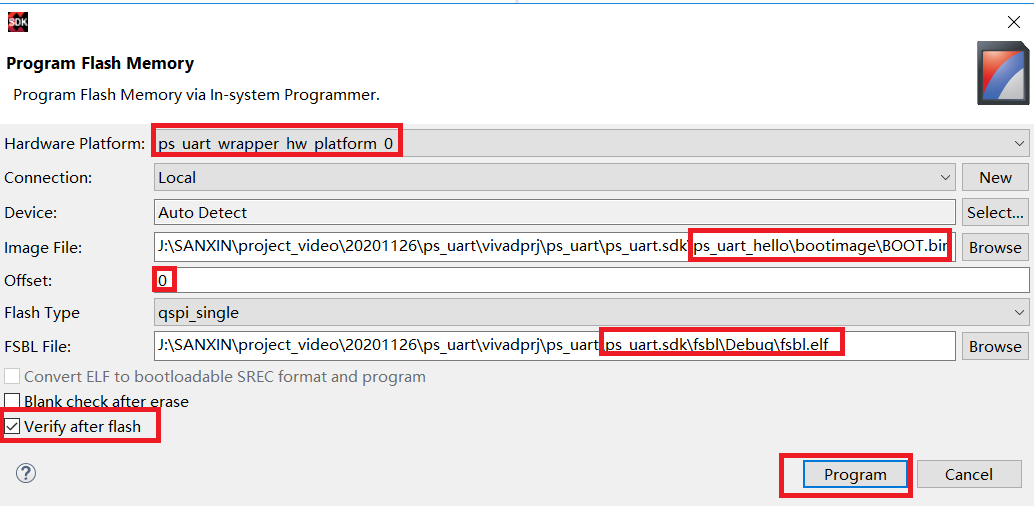

1、在 SDK 菜单 Xilinx -》 Program Flash

2、参数配置

《1》、Hardware Platform 选择我们自己定制的平台;

《2》、Image FIle 文件选择要烧写的 BOOT.bin;

《3》、FSBL file 选择创龙定制的 fsbl.elf,只有用这个 fsbl 才能烧写(我会另写一篇博客单独写怎么定制fsbl.elf文件);

《4》、选择 Verify after flash,在烧写完成后校验 flash

3、注意:第一次固化的时候,里面有uboot在执行,烧写不成功,所以要先在软件点固化,然后快速给开发板上电

4、将启动设置为QSPI【 100101(1~6 QSPI 模式)】,验证固化有没有成功

5、打印的信息和我们在DUBUG的时候一致,代表我们固化成功

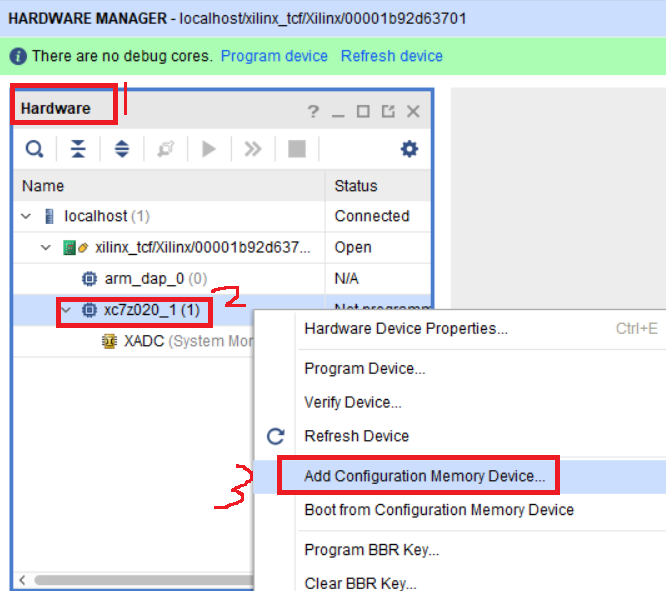

五、QSPI烧写及测试(vivado软件烧写)

1、在 HARDWARE MANGER 下选择器件,右键 Add Configuration Memory Device

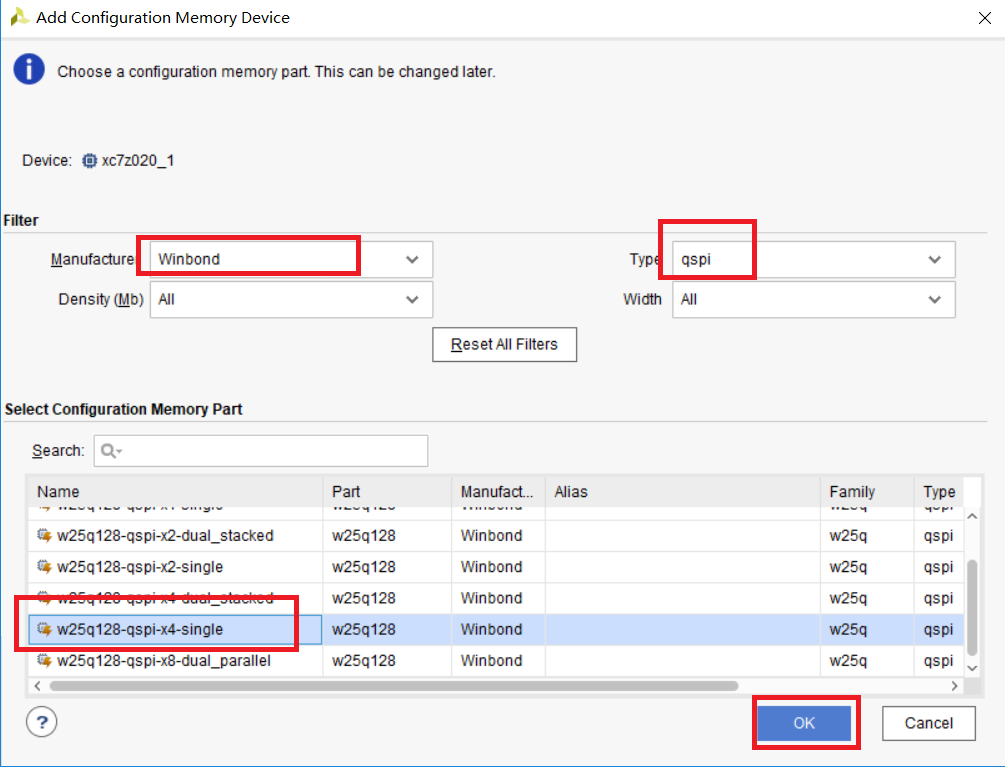

2、选择尝试 Winbond,类型选择 qspi,宽度选择 x4-single,这时候出现 w25q128

选择红框型号,开发板使用 MT25QL256ABA1EW9-0SIT,但是不影响烧录

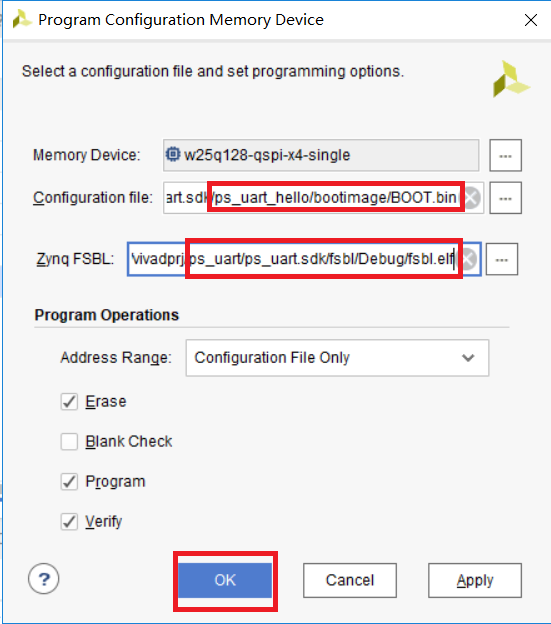

3、在弹出的对话框,提示我们是否立即烧写,点击OK

选择ps_uart_hello/bootimage/目录的BOOT.bin,选择fsbl/debug/目录下的fsbl.elf文件

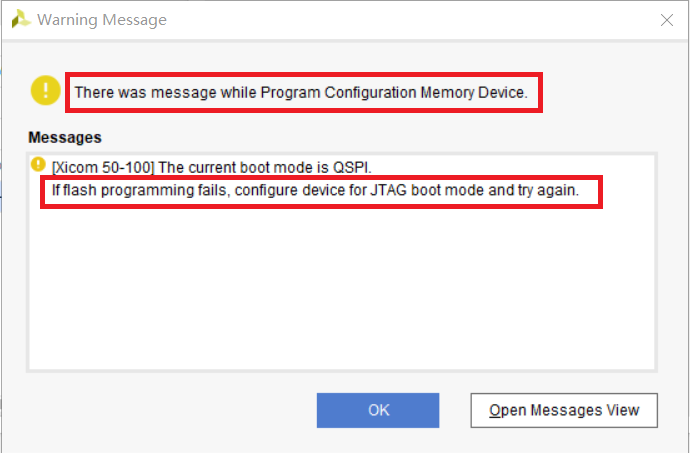

4、提示我们当前是处于QSPI模式的,如果编程失败,请更改模式,再次重试

5、我们将启动模式改为JTAG模式【 010101(1~6 JTAG 模式)】

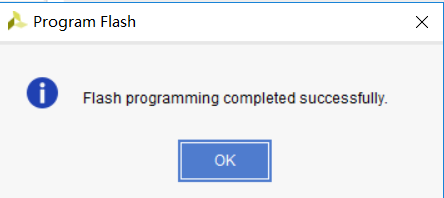

6、断电上电,再次尝试烧写,没有刚才的警告信息了

7、再将启动模式切换为QSPI模式,QSPI【 100101(1~6 QSPI 模式)】,验证固化有没有成功

六、到此PS端的程序固化成功

-

FPGA

+关注

关注

1664文章

22503浏览量

639284 -

FlaSh

+关注

关注

10文章

1759浏览量

155908 -

程序

+关注

关注

117文章

3848浏览量

85472 -

Zynq

+关注

关注

10文章

633浏览量

49574

原文标题:学员笔记精选 | ZYNQ7000系列基本开发流程 之 《PS端程序固化》篇

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

如何在Zynq UltraScale+ MPSoC平台上通过JTAG启动嵌入式Linux镜像

详解Zynq的两种启动模式

ZYNQ 的启动流程介绍

ZYNQ 的启动流程介绍

评论