凭借晶圆级制造工艺,集成光子学领域近年发展迅速,在红外(激光雷达和通信等应用)和可见光(深入新兴应用领域,如显示、光遗传学和量子系统等)波段都已有报道集成光子学平台和制造工艺。然而,这些进展主要集中于硅衬底上的制造工艺,获得的是刚性光子晶圆和芯片,限制了其潜在的应用空间。

柔性集成光子晶圆有望使更多应用领域受益,例如贴合人体或衣物的可穿戴医疗监护设备和柔性显示器等。受益于光子功能的可穿戴医疗保健监护设备可以佩戴于手腕(智能手表)、手指(智能戒指)或上臂(作为贴片),考虑到典型成人的手腕周长、戒指尺寸和上臂尺寸,这些监测设备需要的弯曲直径分别约为4厘米、1.5厘米和7.6厘米。

迄今,已有一些关于柔性光子学制造的报道。实现柔性光子学的一种流行技术是异质集成,即首先在刚性衬底上制造器件,然后通过direct-flip或stamp-assisted工艺将器件转移到柔性衬底上。另一种流行的技术是单片集成,即直接在柔性衬底上对器件进行图案化,而柔性衬底则由刚性衬底临时支撑。不过,这些现有柔性光子学仅限于单个器件或芯片规模的制造工艺,这限制了其可扩展性。

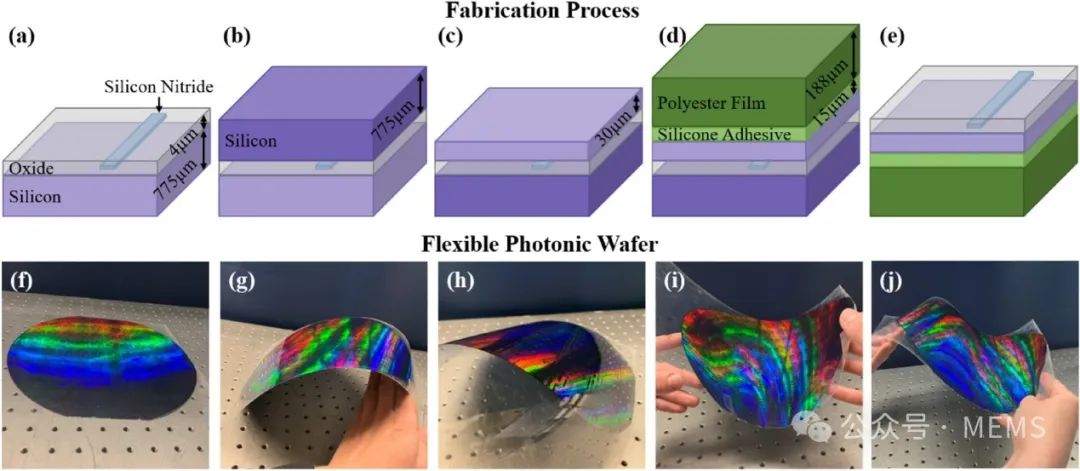

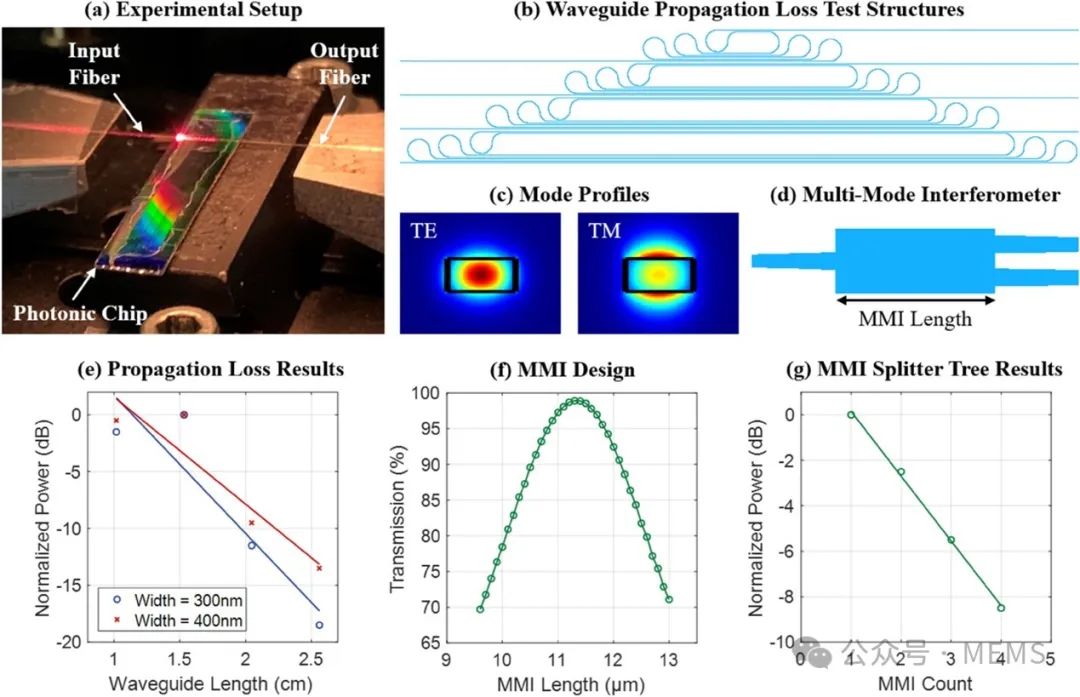

据麦姆斯咨询介绍,美国麻省理工学院(MIT)的研究人员开发并实验表征了第一个可以制造柔性光子晶圆及芯片的300毫米晶圆级平台。首先,研究人员开发了300毫米晶圆级CMOS兼容的柔性平台和制造工艺。接着,通过实验演示了可见光波长下的关键光学功能,包括芯片耦合、波导路由和无源器件。实验证明了光纤到芯片的边缘耦合,耦合损耗为8 dB/facet,300 nm宽和400 nm宽波导的传播损耗分别为12.1 dB/cm和9.4 dB/cm,1 x 2多模干涉仪(MMI)分路器的分路比为2.9 dB,所有这些都在632.8 nm工作波长下实现。

然后,研究人员进行了弯曲耐久性研究,以表征光子芯片的机械柔性。研究人员演示了将单个柔性光子芯片绕直径从5厘米到1.25厘米圆柱体弯曲2000次,其光学性能没有明显下降。最后,研究人员通过实验表征了弯曲柔性光子芯片所引起的偏振效应,比较了柔性芯片平放与围绕两个直径不同圆柱体弯曲时的器件性能,发现输出光的偏振会随着芯片的弯曲而发生变化。

柔性光子芯片的制造工艺

柔性光子芯片的实验表征

展望未来,研究人员将继续开发这种晶圆级制造工艺,深入研究柔性光子芯片的特性。首先,研究人员将在平台上引入晶圆级蚀刻切割沟槽,以实现更平滑的切面和更低损耗的边缘耦合器;其次,探索退火步骤,以及改用LPCVD氮化硅的可行性,以进一步降低波导传播损耗;第三,对柔性光子芯片的机械性能进行进一步数值分析和实验表征,包括量化杨氏模量、弹性常数和断裂强度;第四,研究应变对波导光学特性的影响,进行数值模拟,并将模拟结果与弯曲引起的偏振旋转的实验结果进行比较;第五,探索芯片向另一方向弯曲的影响,由于波导受到的应力和应变不同,预计这将对偏振旋转产生影响;第六,开发一套自动弯曲测试装置,以便对芯片的耐久性进行严格的高通量表征;第七,设计更多量身定制的光子器件,进一步研究芯片弯曲对偏振和损耗的影响。

总体来说,这项研究成果为可扩展的柔性集成光子学制造铺平了道路,推动集成光子学进入需要柔性光子芯片的新应用领域,例如与人体或织物相适应的可穿戴医疗监护仪以及柔性显示器等。

论文链接:

https://doi.org/10.1038/s41598-024-61055-w

审核编辑:刘清

-

CMOS

+关注

关注

58文章

6233浏览量

243409 -

晶圆

+关注

关注

53文章

5450浏览量

132763 -

激光雷达

+关注

关注

982文章

4549浏览量

197107 -

分路器

+关注

关注

0文章

19浏览量

2471

原文标题:柔性晶圆级集成光子学制造平台

文章出处:【微信号:MEMSensor,微信公众号:MEMS】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

一个可以制造柔性光子晶圆及芯片的300毫米晶圆级平台

一个可以制造柔性光子晶圆及芯片的300毫米晶圆级平台

评论