电子发烧友网报道(文/周凯扬)无论是长视频串流平台,还是短视频社交媒体,每日庞大的视频上传数据和访问量都对其背后的硬件平台提出了极高的要求,比如网络带宽、时延、视频处理等,为了进一步优化成本,硬件的选择成了一大难题。比如在视频编解码上,面临效率较低的CPU软件转码和成本较高的GPU硬件转码,不少公司决心改用更具性价比的VPU。

为什么我们需要VPU?

对于视频流媒体网站而言,高效的编码可以在有效节省带宽成本的同时,保证视频质量不变,诸如H265、VP9和AV1等。然而,依赖软件编码虽然能够带来极高的画面质量,但对硬件占用和配置要求高,使得编码效率极低,远不如FPGA、GPU之类的硬件加速。而基于ASIC的VPU,则进一步提高了编码效率,在成本上也要低于FPGA、GPU等硬件。无论是租用服务器还是采用本地服务器,都能使性价比成倍增长。

除了视频串流之外,VPU在另一个云端应用场景中同样起到了至关重要的作用,那就是云游戏。对于云游戏而言,服务器内部的GPU和CPU已经贡献出了一部分算力用于游戏的运行和图形处理,如果再加上视频编码的工作,无疑会进一步加重负载,这也就意味着同规格硬件的并发数会进一步降低。这样的改变反映到租用服务器的游戏厂商上,就等效于支持单个用户的成本降低。

坐拥全球最大视频网站,谷歌选择了自研VPU

要论播放量、规模、地区覆盖以及视频质量,排名第一的视频网站自然是谷歌的Youtube。每分钟500小时以上的视频上传量,超过19亿的月活跃用户,让其成为独一档的视频串流与分享平台。然而,在各大视频网站中,谷歌在图像质量上依然有着绝对的优势,这一方面归功于谷歌的网络基础设施建设,另一方面也与其自研的VPU脱不了干系。

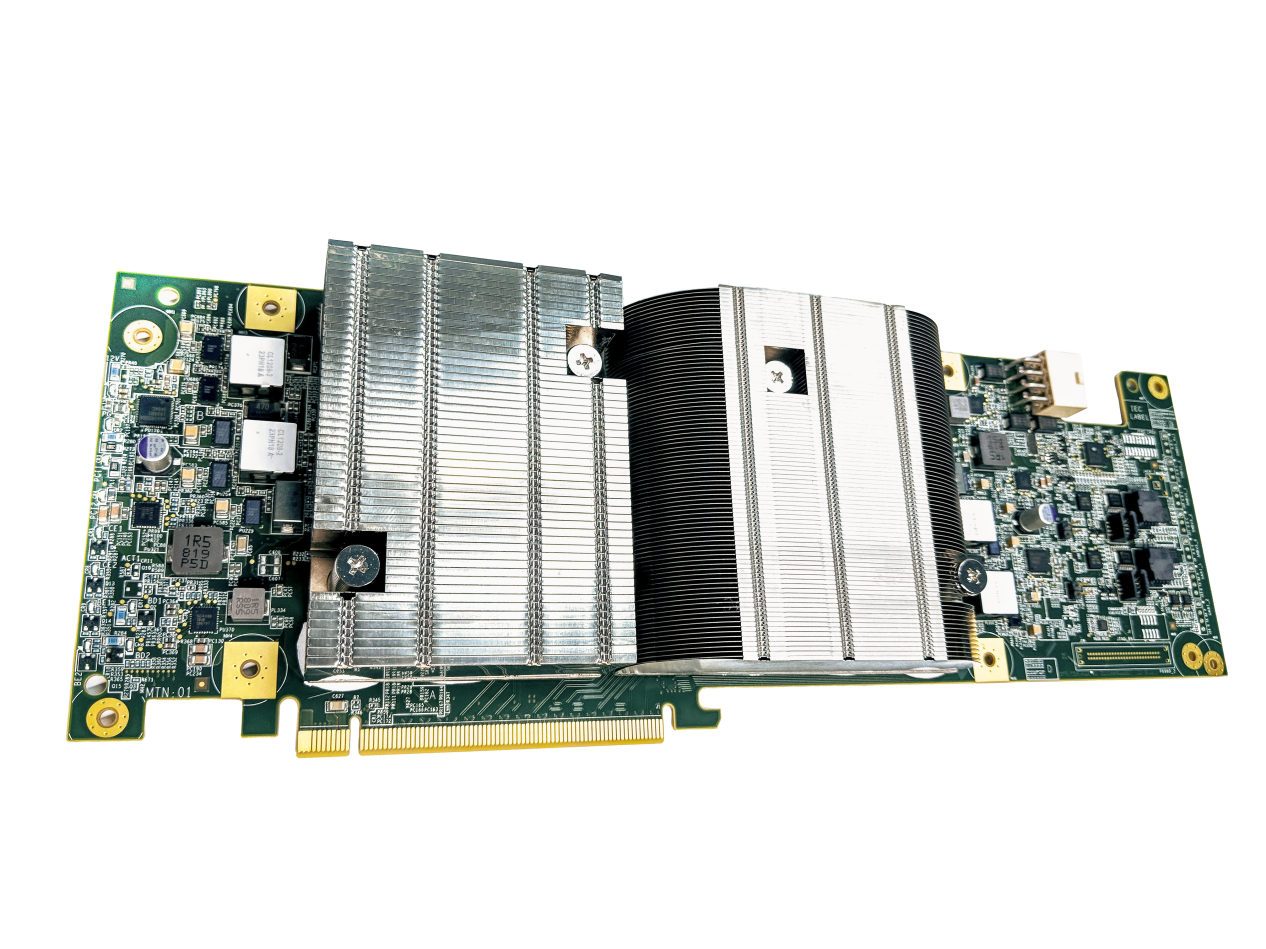

从2015年起谷歌就开始研究独立的视频处理单元,从而用到更加高效的编码,比如VP9。2021年,谷歌发布了首个自研的视频处理单元,谷歌将其称为Argos VCU。这个谷歌自研的ASIC芯片,对最高4K60fps的H.264和VP9编码提供了完整的支持,同时支持单/多输出转码、速度/质量微调等。

谷歌VPU / 谷歌

谷歌声称,相比在传统服务器上使用经过优化的软件转码方案,VCU给他们带来了20到33倍的计算效率提升。与此同时,与谷歌的TPU一样,谷歌已经准备好了硬件迭代的方案,比如增加对AV1编码的支持、进一步提高负载等。

第三方ASIC VPU,智能化成为趋势

有了谷歌的前车之鉴,不少厂商都开始打起了VPU的主意,这也包括了不少第三方VPU设计厂商。以NETINT为例,他们推出了Codensity G5这一ASIC芯片,单芯片可以支持32个1080p30、8个4kp30和2个8kp30视频流的实时编码,时延仅有8ms。Codensity G5既支持H.264、HEVC、AV1的编码,也支持H.264、HEVC和VP9等格式的解码。

与此同时,基于Codensity G5打造的VPU模组还具备18TOPS的AI算力,可以用于视频分析之类的AI从处理器,比如背景去除、画面加强、面部检测和物体检测等。Codensity G5也可与不同架构的CPU混合使用,比如x86的AMD EPYC处理器、Arm的Amepre Altra Max处理器等等。

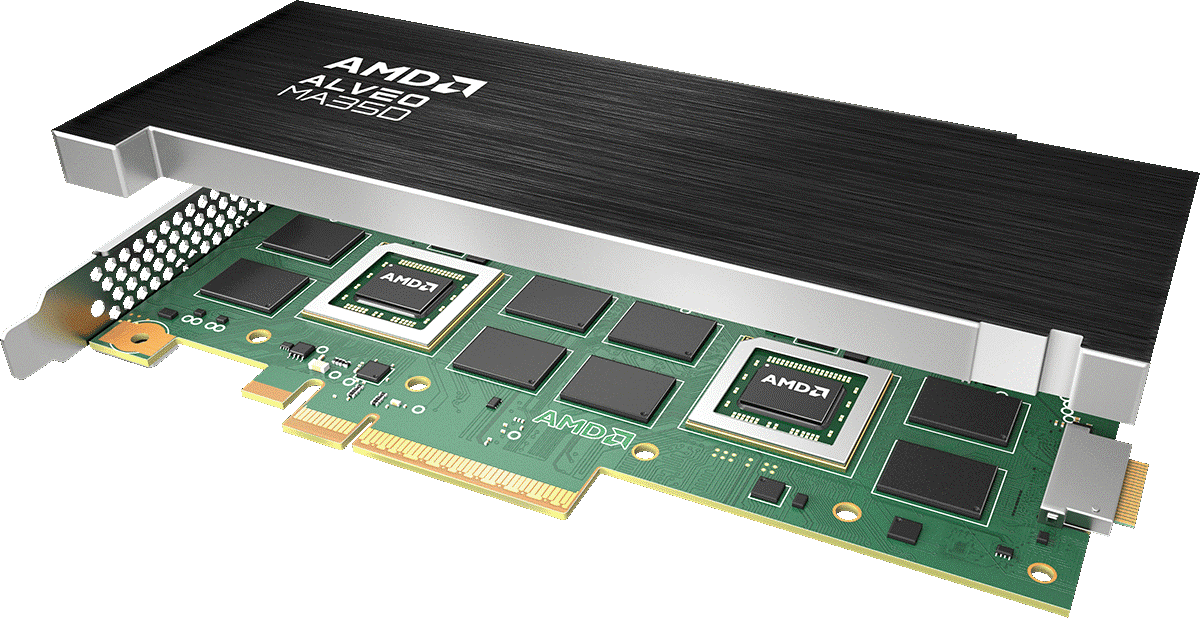

Alveo MA35D / AMD

除此之外,还有曾经以FPGA媒体加速卡方案闻名的AMD/Xilinx,其Alveo U30就是一款混合了ASIC和FPGA设计的处理器。但从去年发布的Alveo MA35D媒体加速卡开始,就成了不折不扣的ASIC VPU方案。相比上一代Alveo U30,Alveo MA35D实现了4倍的通道密度和1.8倍的压缩效率,编解码除了支持主流格式外,也新增了AV1的编码和VP9、AV1的解码。同样是4Kp60的视频,相较于U30的32ms转码时延,MA35D也能做到与Codensity G5一样的8ms。

写在最后

对于多数视频平台而言,有关视频处理类的工作也不仅仅是依赖VPU等硬件,还有一整套预处理管线等。但随着视频在社交媒体内的占比越来越高,VPU能够带来的成本、部署时间优势将越来越明显,尤其在带宽费用寸土寸金的国内。

-

gpu

+关注

关注

28文章

5099浏览量

134455 -

vpu

+关注

关注

0文章

15浏览量

12036

发布评论请先 登录

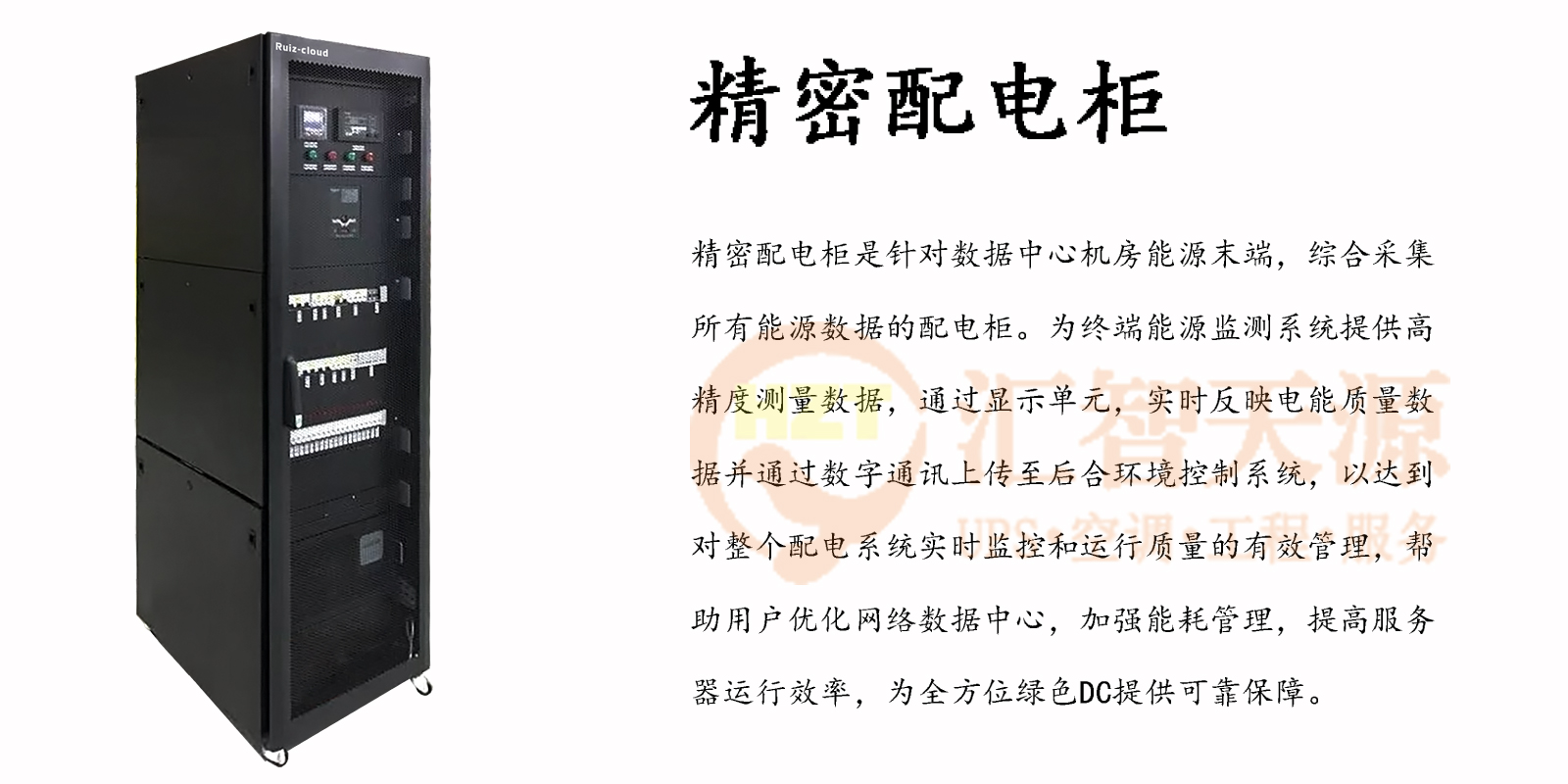

电能质量在线监测装置的暂态数据补传的优先级如何在实际应用中进行动态调整?

电能质量在线监测装置的暂态数据补传的优先级是怎样的?

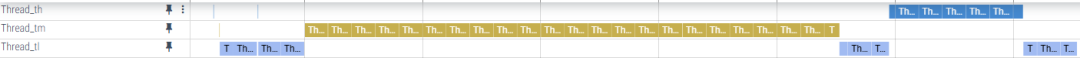

FreeRTOS任务调度及优先级问题

低优先级线程无法调度怎么解决?

什么是RTOS中的优先级反转

求助,关于MS51设置中断优先级问题求解

揭秘!基于RT-Thread探究“优先级反转”下的任务调度究竟是什么样的?| 技术集结

大串流时代,VPU的优先级甚至高过GPU

大串流时代,VPU的优先级甚至高过GPU

评论