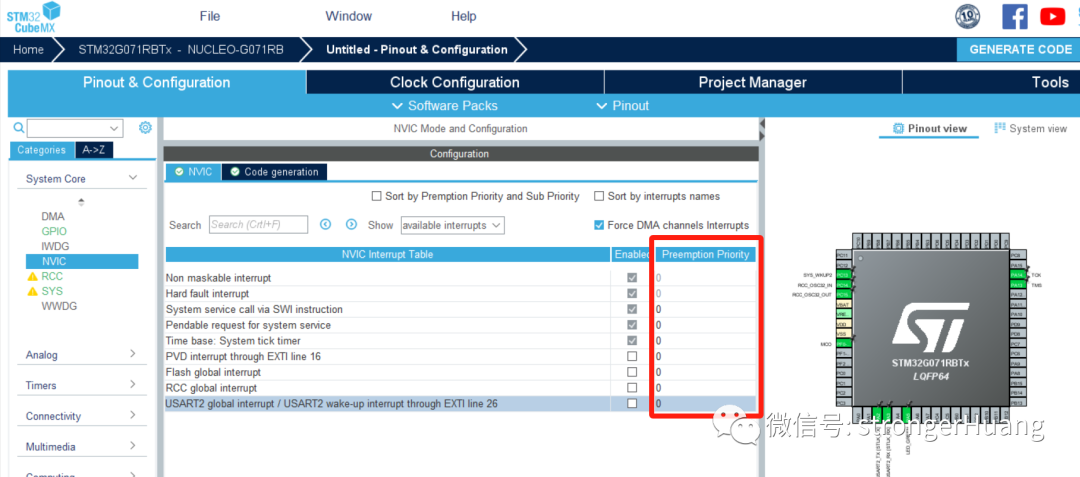

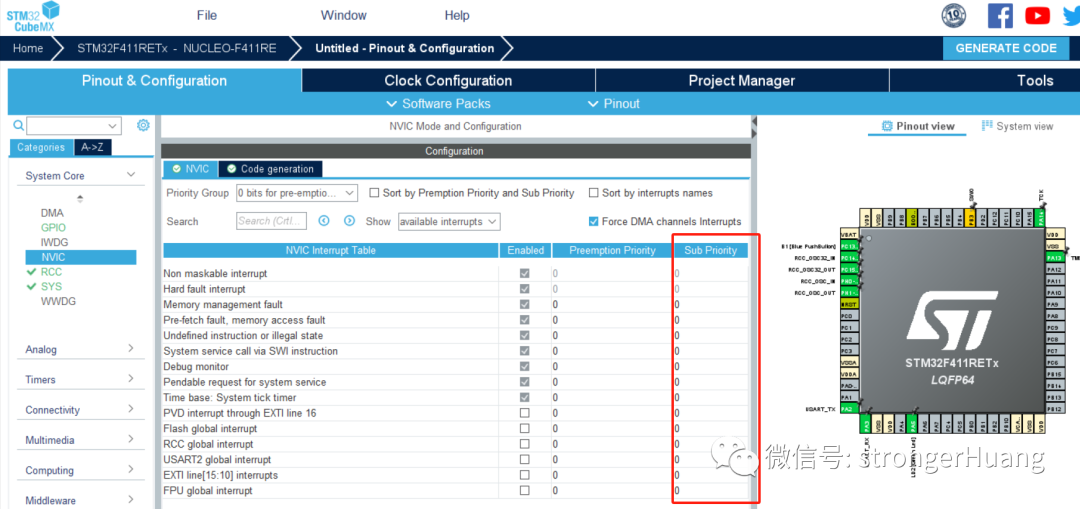

看到一个交流群在讨论关于【关于STM32中断优先级的话题】,其中就有小伙伴提到:为什么有些STM32中断没有【子优先级】? 比如,有时候你在使用STM32CubeMX配置时,你会发现只有Preemption Priority【抢占优先级】,而没有Sub Priority【次优先级】:

这个问题就牵涉到STM32,准确的来说的是 Cortex-M NVIC嵌套向量中断控制器的问题。

关于Cortex-M的NVIC

NVIC:Nested Vectored Interrupt Controller,嵌套向量中断控制器。 在每个Cortex-M内核中都有这么一个NVIC嵌套向量中断控制器,当MCU使用的内核不同,其中的NVIC也可能不同。 比如,Cortex-M0和Cortex-M3内核中NVIC功能就不同。 其中,中断优先级分组功能就不同。 Cortex-M0的NVIC没有优先级分组功能,Cortex-M3、 M4、M7有分组功能。 所以,你在使用STM32CubeMX配置时,M0/M0+内核的STM32是没有【次优先级】那个选项的。

Cortex-M0包含STM32F0、L0、G0等处理器。

对底层感兴趣的朋友可以继续往下看。

所以,你在使用STM32CubeMX配置时,M0/M0+内核的STM32是没有【次优先级】那个选项的。

Cortex-M0包含STM32F0、L0、G0等处理器。

对底层感兴趣的朋友可以继续往下看。

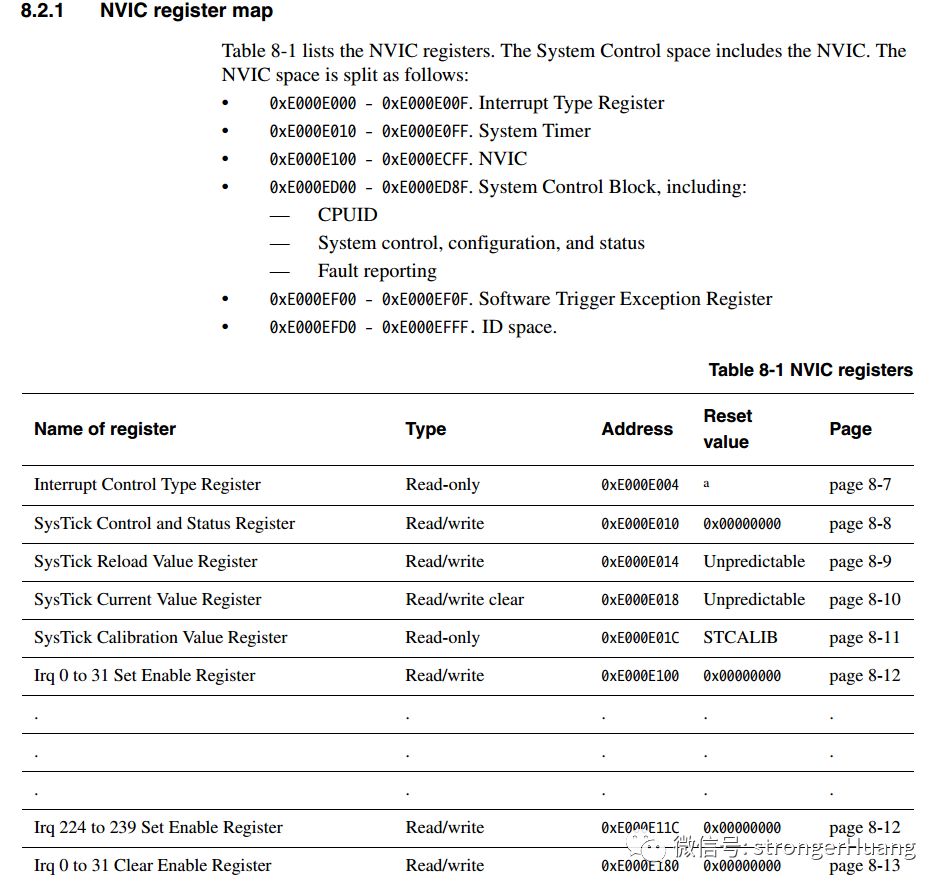

NVIC寄存器

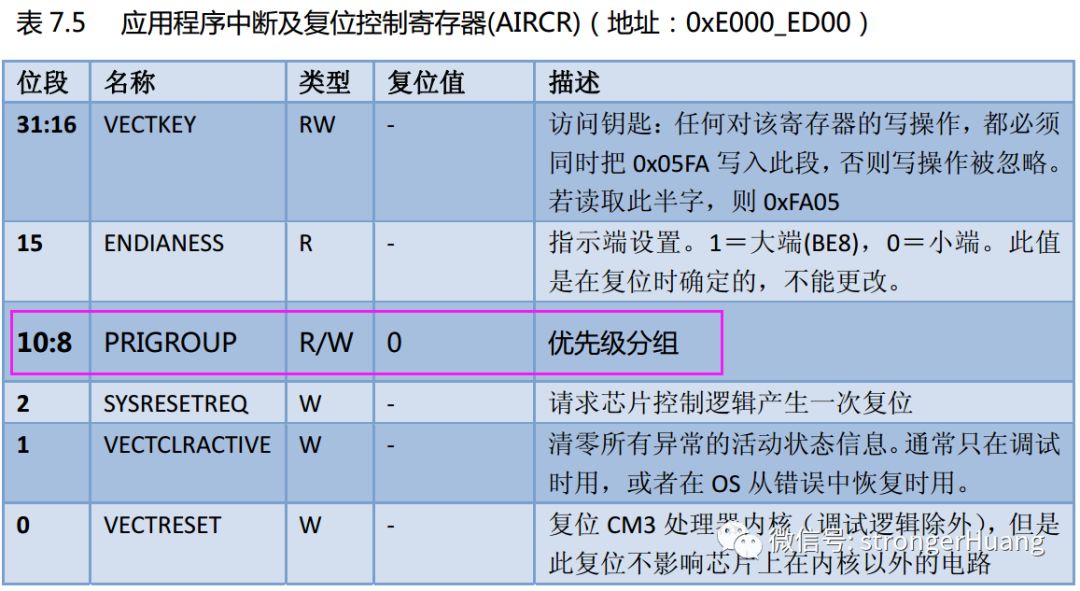

NVIC寄存器,需查看对应的内核(Cortex-M)手册,在ARM官网能找到(M3也有对应的中文翻译版,大家可以自己网上搜索)。 内核中的寄存器和我们STM32参考手册中寄存器一样,不同的Bit位代表含义不同。 但是,对于NVIC来说,由于包含众多优先级相关配置,寄存器数量相对较多(NVIC寄存器族)。 拿M3来说,优先级分组的配置,位于NVIC的AIRCR应用程序中断及复位控制寄存器中:

拿M3来说,优先级分组的配置,位于NVIC的AIRCR应用程序中断及复位控制寄存器中: 这里推荐阅读之前我写过的一篇文章:Cortex-M中断在RTOS中的应用及注意事项

这里推荐阅读之前我写过的一篇文章:Cortex-M中断在RTOS中的应用及注意事项

中断入口

额外提下一个小伙伴问的问题:为什么外部中断8和9都使用同一个中断?

void EXTI9_5_IRQHandler(void)

{

if(EXTI_GetITStatus(EXTI_Line8) != RESET)

{

/* 代码 */

EXTI_ClearITPendingBit(EXTI_Line8);

}

if(EXTI_GetITStatus(EXTI_Line9) != RESET)

{

/* 代码 */

EXTI_ClearITPendingBit(EXTI_Line9);

}

}

我想,这个问题应该不难。好比一个main程序入口,进入之后需要处理很多事情,只是在里面需要区分事件。

很多外设中断,都会使用同一个中断入口,有一个原因:节约中断入口资源分配。

像USART发送和接收中断,TIM不同通道捕获中断等。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

mcu

+关注

关注

147文章

18604浏览量

386670 -

控制器

+关注

关注

114文章

17638浏览量

190195 -

STM32

+关注

关注

2305文章

11120浏览量

371080

发布评论请先 登录

相关推荐

热点推荐

电能质量在线监测装置的暂态数据补传的优先级如何在实际应用中进行动态调整?

电能质量在线监测装置的暂态数据补传优先级在实际应用中通过 事件驱动、主站指令、资源状态感知和动态策略调整 等多层机制实现灵活调控,确保关键数据的实时性与可靠性。以下是具体实现方式和典型场景的动态调整

电能质量在线监测装置的暂态数据补传的优先级是怎样的?

电能质量在线监测装置的暂态数据补传优先级设计遵循 事件驱动、主站指令优先、资源动态分配 的原则,结合行业标准和设备机制,形成以下多层级优先级体系: 一、最高优先级:紧急事件驱动补传 1

FreeRTOS任务调度及优先级问题

都有容错,但是心里没底,想向大家了解一下实际工作中有没有遇到到类似的问题,如果有又是怎么解决的呢?

另外有前辈可以分享一下任务的优先级在实际项目中该基于什么原则来划分呢?

发表于 11-06 02:18

低优先级线程无法调度怎么解决?

1,设置了3,5,6,8几个优先级,设备在现场正常运行了一年多后,显示、前端、后端这3个低优先级线程异常了,表现为屏幕不动,前端采集数据没有变化等,其他高优先级的线程如通讯,按键都能正

发表于 09-25 07:33

什么是RTOS中的优先级反转

当一个高优先级任务正在等待一个资源,但一个低优先级任务正在持有它,一个中等优先级任务继续在中间运行时,就会发生优先级反转——阻止低优先级任务

求助,关于MS51设置中断优先级问题求解

我确实发现在库代码和 TRM 之间设置中断优先级有一些差异,如下图所示。

Could you check what's wrong with me?

发表于 08-25 07:01

请问STM32的内部Flash操作是不是优先级最高?

STM32的内部Flash操作是不是优先级最高?目前在内部Flash的单独一页存储了数据,发现在进行页擦除的时候正常工作的定时器中断无法进入了

发表于 08-13 07:03

STM32G474进入Fault3中断没办法设置成周期性触发吗?

手动操作硬件触发了Fault3故障,进入了Fault3中断,此时若故障一直存在程序就在中断里无法出来,FreeRTOS停止运行,把故障解除后FreeRTOS正常运行,即使把Fault3中断优先

发表于 08-01 07:23

STM32中断没有子优先级?

STM32中断没有子优先级?

评论