共读好书

刘倩,邱忠文,李胜玉

(中国电子科技集团公司第二十四研究所)

摘要:

为了响应集成电路行业更高速、更高集成度的要求,硅通孔技术(ThroughSilicon Via, TSV)成为了半导体封装核心技术之一,解决芯片垂直方向上的电气和物理互连,减小器件集成尺寸,实现封装小型化。本文介绍了硅通孔技术的可靠性,包括热应力可靠性和工艺技术可靠性两方面。过大热应力可能会导致通孔侧壁粗糙,并影响内部载流子迁移率,从而使器件功能失效。可以通过采用热硅通孔、浅层沟槽隔离技术、合理调整通孔结构和深宽比来减小热应力。TSV 工艺可靠性主要体现在通孔侧壁光滑程度和通孔导电材料填充效果,可通过循环氧化、在电镀液中加入抑制剂和加速剂以及熔融法进行改善。

引言

在过去的半个世纪里,摩尔定律引导着集成电路行业朝着低功耗和高性能的目标迈进,推动着科学技术的发展。但随着集成电路的不断发展和人们对电子产品的需求不断提高,对芯片能够实现越来越多功能的要求也更加急迫,通过不断缩小芯片特征尺寸来提高系统集成程度和处理速度的局限性就凸显出来。当芯片的尺寸不断减小,会出现散热降低、泄露电流增加等问题,导致器件性能参数漂移,器件甚至直接失效[1] 。为了克服这些问题,可以从两方面进行研究:一方面积极研究使用新型材料和结构来设计制造器件,实现摩尔定律的延续;另一方面,不再局限于传统的二维结构,在平面的基础上向垂直方向发展,实现高密度小尺寸封装。三维封装技术的发展和成熟使得器件封装密度的不断提高成为了可能,如何将多个芯片在垂直方向上进行层叠并实现电气互连成为了未来集成电路发展的重要方向之一,即芯片互连。

为了在芯片与芯片、芯片与基板之间进行信号的传递,芯片互连技术对于实现物理连接和电气连接都有不可或缺的重要作用。其中,硅通孔技术是实现这种物理和电气连接的关键技术之一,该技术是在垂直方向上堆叠的晶圆之间制作通道,在通孔内进行高导电性材料的填充,晶圆以较大密度堆叠在一起,从而能够实现目前电子器件多功能集成且封装尺寸更小的技术要求。因此,TSV 也被称第四代互连封装技术,为加快三维集成封装技术的迅速发展提供了可能[2] 。

1 可靠性概述

目前,TSV 技术主要是以小孔径尺寸和高深宽比通孔为发展目标和方向,不仅带来了集成电路行业发展的机遇,也迎来了新的挑战。作为实现晶圆或芯片之间电气和物理连接的重要技术,TSV 技术对于三维封装技术的实现以及多系统整合有着不可替代的作用。因此,TSV 技术的高可靠性对于高集成度芯片可靠性发展至关重要,其可靠性涉及了热应力和工艺等方面。

随着三维封装技术的应用和芯片封装密度的增大,芯片工作时不能迅速有效散热,会引起严重的热应力问题[3] 。铜、硅和二氧化硅的热膨胀系数之间有较大的差别,这种不同材料间热膨胀系数的差距引起的热应力会使得二氧化硅和填充材料之间的界面发生分层,导致器件出现性能参数漂移、使用寿命缩短等问题,会严重影响器件的使用可靠性 [4, 5] 。另外,在高温下,硅通孔的存在引入的热应力会使器件有源区受到影响,使得器件内部载流子迁移率发生改变,也可能会引起器件发生重大的可靠性问题[6] 。根据研究显示,孔径大的硅通孔会产生较大的热应力,这种热应力的存在会改变晶体管内部的载流子迁移率。相关数据表明,在 100 MPa 应力的作用下,晶体管内部载流子的迁移率能达到 7 % [7] 。因此,解决硅通孔引起的热应力问题对于保证器件的正常使用至关重要。

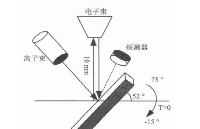

从工艺角度考虑,目前通用的硅通孔刻蚀技术有两种,干法刻蚀和湿法刻蚀,其中干法刻蚀工艺中常用的是 Bosch 刻蚀。先使用六氟化硫气体与硅刻蚀反应形成通孔,然后用八氟环丁烷气体与之反应,在通孔的内侧和底部形成钝化膜,再使用六氟化硫刻蚀钝化层和硅层[8] 。这种刻蚀和钝化过程相间进行的干法刻蚀方法会导致通孔的内侧壁粗糙,产生扇贝纹,如图 1 所示,进而妨碍了后续其他导电材料的填充,致使导电材料和硅层之间的界面不平滑,从而严重影响了 TSV 的导电性能,进而影响芯片的功能和使用寿命[9] 。因此,通过改进当前的技术工艺,可以进一步提高 TSV 技术的可靠性,从而提高三维封装可靠性。

2 热应力可靠性

2.1 采用 TTSV 降低 TSV 热应力

对于三维集成技术来说,实现了多层叠堆和高集成度,却不可避免地影响芯片的散热问题。从提高导热性能方面出发,可以采用热硅通孔(thermal through siliconvia,TTSV)来促进垂直方向上堆叠的芯片之间产生的热量传递,增强芯片的散热,以减小热应力的产生。通过插入具有铜芯和氧化物衬底的 TTSV,最高芯片温度将显著降低约 62 ℃[10] 。不同于传统的 TSV,TTSV 有较高的热传导率,能够迅速传导热量。崔玉强[11]等通过有限元方法仿真发现,与使用钨、铜作为 TTSV 导热芯相比,使用碳纳米管作为 TTSV 的导热芯材料能够明显降低芯片温度。尽管与其他填充材料相比,碳纳米管的传热性能十分突出,在芯片降温方面优势显著,但是其在实际应用当中仍然有较多问题函待解决,例如,碳纳米管的成本与性能之间的矛盾,且工艺复杂等。

2.2 采用 STI 降低 TSV 热应力

目前常用的改善器件内部热应力问题的方法是在硅通孔附近划分一个保留区域(keep-outzone,KOZ) [12] ,一般不会将对应力敏感的器件放置在载流子迁移率大于5 %的区域内。这种方案虽然改善了热应力对载流子迁移率的消极影响,却使得衬底面积被大量浪费,也不能适应高集成度的需求。一种浅层沟槽隔离技术(ShallowTrench Isolation,STI)可以在提高衬底面积利用率的同时更有效地降低硅通孔热应力的产生,这种 STI 技术是通过在硅通孔和有源区之间刻蚀一圈浅层沟槽来减小热应力。先在半导体基底上沉淀一层氮化硅,接着通过腐蚀在 KOZ 区得到一个沟槽,然后将沟槽进行氧化,沉淀二氧化硅,最后对侧壁进行平坦化,提高其光滑程度。相关试验发现,这种技术会引起硅通孔周围产生压缩应力[13] ,将该应力充分利用,使其与硅通孔所引入的热应力进行叠加抵消,可以明显削弱热应力。通过仿真计算对比使用 STI 技术的 TSV 和没有 STI的 TSV 的 KOZ区,STI 技 术 使 得 KOZ 减 小 了(0.644~4.346)μm(10.3~25.8)% [14] 。事实证明使用浅层沟槽隔离技术可以有效减小 KOZ 区域大小,从而在不浪费面积的同时,降低了热应力的负面影响。孙汉

[15]等人为了解决大尺寸硅通孔结构热应力问题,设计了一种热应力释放槽结构。通过仿真分析发现,由于释放槽的存在,TSV 槽外的热应力约为没有释放槽 TSV 的 50 %,同时还减小了 KOZ区的面积,提高衬底面积使用率,且应力释放槽与硅通孔的距离越远,基片表面热应力的减小程度越大。

2.3 不同深宽比和通孔结构的影响

采用有限元软件对铜填充 TSV 进行仿真分析,得出其等效热应力大小及分布。仿真分析表明,最大热应力出现在金属层与介质层的界面处,且最大热应力点与最高温度值点相对应。当硅通孔的孔径大小不变时,随着通孔深度的不断增大,其产生的最大热应力也随之减小,同时通孔附近的最高温度值也随之降低,这说明通孔越深,TSV 的散热性能越强;当 TSV 深度保持不变,通孔的尺寸越小时,其热应力越小,即硅通孔的深宽比越大,产生的热应力就越小,其散热功能越强[17, 18] 。

通孔结构对于热应力也有一定影响。将圆柱型 TSV与圆台型 TSV 的热应力等效值进行对比,发现圆台型TSV 热应力比圆柱型的大,且圆台型的平均温度也比圆柱型的高,这表明圆柱型硅通孔能够更好的进行散热。另外,根据热应力云图可以发现,圆台型 TSV 的热应力主要集中在小孔径处,而圆柱型 TSV 的热应力主要集中在上表面。总的来说,圆柱型硅通孔的总体散热性能明显强于圆台型,但圆台型硅通孔的热应力更集中,在大孔径处的热应力反而低于圆柱型的[19] 。掌握通孔结构和不同深宽比通孔对 TSV 热应力的影响,可以更好地进行硅通孔散热方面的设计,对其可靠性也具有积极的指导作用。

3 工艺可靠性

3.1 降低通孔内壁扇贝纹起伏

硅片经过刻蚀工艺形成硅通孔,不同的刻蚀工艺会得到不同光滑程度的通孔内侧,而内侧的光滑程度对于后续进行金属导电材料的填充有着直接的影响,填充效果对于 TSV 的物理和电气连接可靠性来说至关重要。目前广泛使用的硅通孔刻蚀技术之一是Bosch 刻蚀技术,但该方法不可避免地会在通孔内壁形成扇贝纹[20] 。通孔内壁的光滑程度越高,硅通孔引起的平均热应力也会越小。同时,内壁扇贝纹的形成会引起峰值应力的产生,其值明显高于平均热应力,这种现象的出现使得峰值应力所在区域的应力差异过大,这种应力值差异甚至会引起硅通孔的结构失效,严重影响 TSV 技术的可靠性[8] 。因此,降低通孔内壁扇贝纹的出现对于提高硅通孔以及芯片的可靠性是非常重要的。

Morikawa 等人[21]采用平面磁中性环路放电等离子体深孔刻蚀技术,虽然能够得到高深宽比和无扇贝纹的通孔,但通孔侧壁仍然具有一定的粗糙度。赵鸿[22]等人基于电感耦合等离子体(ICP)技术也实现了小孔径、高深宽比通孔的刻蚀,并且,使用 ICP 技术能够降低衬底温度,同时缩短刻蚀和钝化时间,削弱了扇贝纹起伏幅度,但依然不能完全消除。采用反应离子刻蚀(RIE)技术避免了通孔顶部的侧壁波纹,与传统的 Bosch 刻蚀工艺进行对比发现,最大均方根粗糙度由 15.1 nm 降至6.89 nm [23] 。采用循环氧化法也可以有效降低扇贝纹的出现。先将硅片进行热氧化操作,之后通过湿法腐蚀进行清洗,可以得到较为光滑的通孔内侧壁。经过重复循环高温热氧化和腐蚀二氧化硅的过程 , 可明显减小扇贝纹尺寸,得到更加光滑的硅通孔内壁[24] 。

3.2 导电材料填充技术

硅是一种半导体材料,通过在通孔中进行导电物质的填充来实现硅通孔的导电性能,其中铜是一种被广泛使用的导电物质。通孔导电材料填充技术的主要关键点在于一方面要能够高效率、低成本地进行通孔导电材料的填充,另一方面又要保障填充后通孔内部无空洞,且在受到剧烈温度变化刺激时,界面不会发生分层或开裂等现象[6] 。为了达到通孔内部无空洞的填充效果,在减缓金属在硅片表面沉积速度的同时需要提高金属在硅通孔内的沉积速度,可以通过在电镀液中加入抑制剂和加速剂等添加剂的方法实现。这两种添加剂的存在可以在电镀过程中减小电镀液的表面张力,同时增强其分散能力。当下常用的加速剂通常是小分子含硫有机物,可加速铜离子的沉积;常用的抑制剂一般是大分子物质,如聚乙二醇,这种抑制剂可以吸附在通孔顶部和底部的表面,从而抑制顶部和底部的沉积速率[25] 。

熔融法填充硅通孔是一种可以实现 TSV 通孔导电材料快速、无空洞填充的技术,在真空压力下将熔融状态的金属填充进通孔中,可以实现快速、无空洞的充填,且生产效率高,但是在多次高低温循环的过程中,由于不同材料的热膨胀系数也不同,金属材料填充物与硅之间的界面会产生裂缝[26] 。采用一种新的 Bi-Sn-Ag 合金材料作为硅通孔的导电填充材料,这种新型材料可用于超小尺寸通孔的填充,且具有高耐热性(>260 ℃)和低温填充能力(<300 ℃),填充效率高[27] 。

4 结束语

在未来先进封装技术中,硅通孔技术是支撑多芯片垂直方向上物理和电气连接的关键技术。该技术顺应了集成电路高密度、快速响应速度、低成本和低功耗的发展趋势,满足未来电子设备更小尺寸封装结构和多功能集成的需求。因此,提高硅通孔技术的可靠性可以推动集成电路行业的高速可靠发展。

本文主要从两方面介绍 TSV 可靠性,热应力可靠性和工艺可靠性。从热应力角度,可以采用TTSV增强散热,利用 STI 技术有效降低 KOZ,同时掌握通孔结构和不同深宽比对 TSV 设计有重要意义。在工艺可靠性方面,采用循环氧化法可明显削弱扇贝纹起伏,提高 TSV 内壁的平滑程度;在电镀液中加入抑制剂和加速剂两种添加剂,可较大程度地改善导电材料在通孔内的填充效果;熔融法填充技术可以实现高效率、无空洞的导电材料填充。如今,虽然高可靠性的硅通孔技术的工艺成本仍较高,但随着工艺技术的不断提高与成熟,TSV 技术会被大量应用于三维封装,推动集成电路朝着更小尺寸、更多功能、更低成本、更高效率、更高可靠度的方向发展。

原文标题:硅通孔技术可靠性技术概述

文章出处:【微信公众号:半导体封装工程师之家】欢迎添加关注!文章转载请注明出处。

-

集成电路

+关注

关注

5464文章

12686浏览量

375742 -

硅通孔

+关注

关注

2文章

31浏览量

12150 -

硅通孔技术

+关注

关注

0文章

3浏览量

3526

发布评论请先 登录

无线通信技术核心定位从 “速度竞赛” 转向超高可靠性

有机硅灌封胶在汽车电子中的可靠性

什么是高可靠性?

灌封技术提高PCB可靠性并延长使用寿命

芯片可靠性(RE)性能测试与失效机理分析

如何测试单片机MCU系统的可靠性

技术拆解:沃虎防水连接器如何实现IP68级可靠性?

单片机应用系统的可靠性设计介绍

可靠性设计的十个重点

硅通孔技术可靠性技术概述

硅通孔技术可靠性技术概述

评论