随着片上系统(SoC)设计领域的不断发展,设计的复杂性与芯片技术的持续进步紧密交织,共同推动着电子设备未来的发展。

为满足自动驾驶和5G网络等先进应用对芯片的高要求,半导体晶圆厂纷纷采用复杂的层叠技术和多重光刻等技术,在越来越多的掩膜上实现更多晶体管的布局。这些大型SoC设计的开发过程在多个阶段都面临着挑战,尤其是在版图物理验证这一关键阶段,由于先进工艺节点(7纳米、5纳米、3纳米等)以及掩模数量的增加使得这一挑战尤为突出。这一验证步骤是芯片设计至关重要的里程碑,是芯片流片路上最重要的环节之一。

版图与原理图一致性检查(Layout-versus-Schematic,LVS)是SoC(系统级芯片)开发流程中的关键环节,其核心是确保芯片上的逻辑表示与物理实现相吻合。但随着SoC设计日趋复杂和芯片技术的不断进步,曾经被认为简单的LVS如今面临着重大挑战。

在审视LVS在芯片开发中作用的变化时,我们将打破一个常规的误解:即认为LVS仅是芯片开发过程中的一项固定步骤。相反,我们将探讨新兴LVS工具如何冲破传统流程的限制,带来创新的方法论。

应对物理验证挑战

现代SoC的开发涉及到多个方面,设计团队需利用各种工具和方法来应对愈加复杂的设计、更短的设计周期和更多的验证要求。借助LVS按时完成物理验证可以有效防止计划延误,避免上市时间延长,从而保障芯片的市场竞争力。

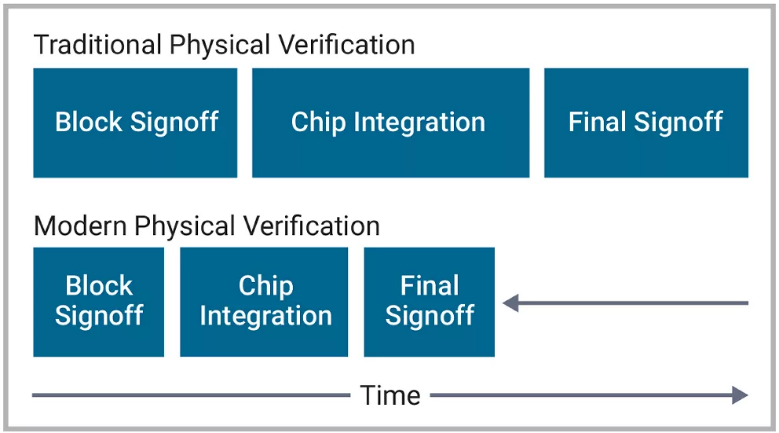

为了将物理验证提前至设计流程的早期阶段,有必要在SoC布线前的多个不同阶段进行验证。一旦SoC的主体部分组装完毕,LVS检查就可以与全芯片装配工作并行启动。现代LVS工具需能够最初在宏观/IP/模块层面上运行,并迅速评估整个芯片设计的状态,提供有价值且可操作的反馈,使开发者能够及时解决问题。

▲加速SoC物理验证签核

在大规模电路设计的背景下,LVS流程耗时数十小时甚至数日都是常有的情况。根据设计的清晰度,通常涉及到多次迭代,包括调试错误、纠正设计以及重复进行LVS的过程。鉴于现代电路设计的复杂性,即使对于经验丰富的开发者来说,管理这一反复的过程也证明是充满挑战且耗时的。

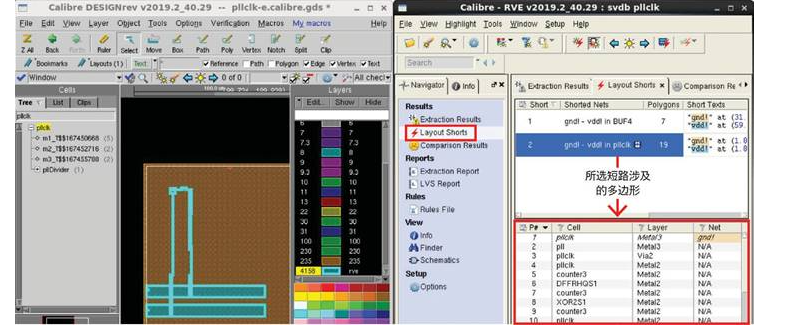

在芯片项目的最后阶段,执行LVS、调试以及迭代的复杂性往往是导致进度延误的主要原因。当LVS首次在整合了所有设计组件的布局上运行时,这一挑战会变得更加严峻,因为这一阶段可能会揭露之前合并过程中未曾显现的众多新问题。这些问题可能包括IP的挑战、接口引脚对齐错误、顶层短路、集成错误等等。

创新型全芯片LVS检查工具:加速验证流程,提升设计效率

面对这些挑战,新思科技推出了搭载Explorer LVS技术的创新型新思科技IC Validator。这款现代LVS工具可以在早期完整芯片LVS运行中快速识别问题的根本原因,为更高效、更可靠的验证流程铺平道路,从而支持数十亿个晶体管的超大型芯片设计。

LVS可以在设计和验证周期的任何阶段使用,但效益最大化的时机是在完成全芯片集成后立即运行它,这时通常可以检查出最意想不到的问题。在第一阶段,工具启动基于文本的短路检测并剔除等效单元。第二阶段进行连通性不匹配和开/短路检测。此外,它还会标定等效单元以便提取,并进行黑盒测试对比。在最后阶段,将进行全面的LVS检查,提取所有层次和数据,执行全方位对比分析。

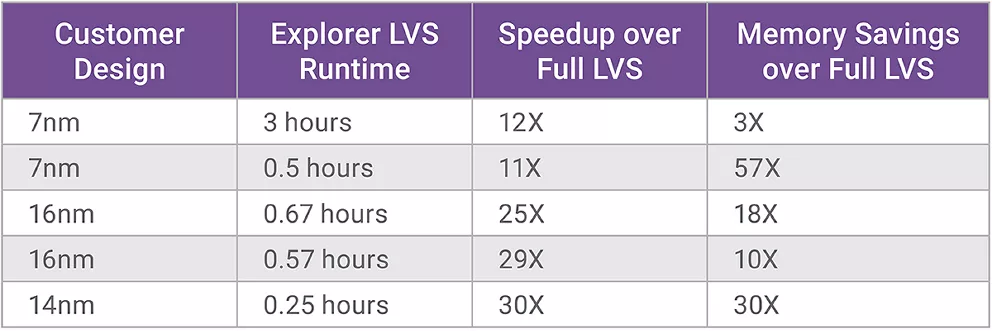

开发者可以利用摘要报告来评估全芯片设计的整体质量,确保设计已经准备好签核,且所有错误已被排除。如果在签核之前出现临时更新,Explorer LVS能够确保设计的完整性不受影响。与传统工具相比,这个工具能帮助客户以多达30倍速度加快运行,减少多达30倍内存用量。

▲Explorer LVS的实际性能表现

用现代化LVS工具,更早更自信地流片

随着芯片技术的不断进步和对更高性能电子设备的不懈追求,理解LVS不断演变的角色,并将其尽可能地向设计流程的前端移动,已成为设计团队的首要任务。尽早对全芯片进行LVS检查,快速自动地定位根本原因,不仅能缩短产品上市时间,还能为创新留出更多空间。借助现代化的LVS工具,SoC开发者能够在确信已经识别并解决了所有LVS问题的情况下,更早地自信地完成流片。

审核编辑:刘清

-

晶体管

+关注

关注

78文章

10434浏览量

148542 -

片上系统

+关注

关注

0文章

205浏览量

27724 -

SoC芯片

+关注

关注

2文章

672浏览量

37272 -

LVS

+关注

关注

1文章

38浏览量

10521 -

自动驾驶

+关注

关注

794文章

14976浏览量

181349

原文标题:你的芯片验证够快够准吗?新一代全芯片LVS,runtime提速30倍

文章出处:【微信号:Synopsys_CN,微信公众号:新思科技】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

关于功能验证、时序验证、形式验证、时序建模的论文

Mentor工具简介Calibre物理验证系列

芯片设计完整流程及工具

芯片设计流程及工具

数字芯片设计流程

用Hercules完成物理验证的详细流程

基于Cadence软件DRACULA工具的LVS检查

国产EDA验证调试工具实现破局 助力芯片设计效率提升

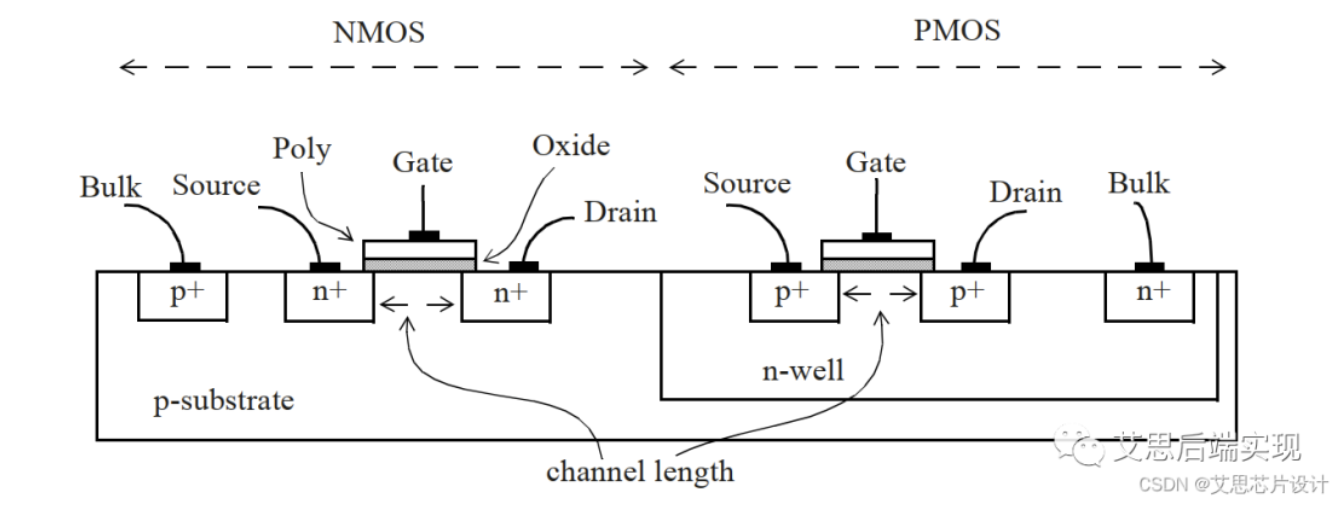

物理验证LVS对bulk(体)的理解和处理技巧

芯华章发布国内首台超百亿门大容量硬件仿真系统 完备数字验证全流程工具平台

英诺达EnCitius® SVS新功能发布,加速芯片验证流程

创新型全芯片LVS检查工具:加速验证流程,提升设计效率

创新型全芯片LVS检查工具:加速验证流程,提升设计效率

评论