一、引出NAND访问问题

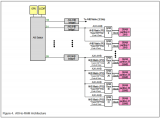

痞子衡最近需要在恩智浦无线系列 SoC(RW612)上调试串行 NAND Flash 驱动,简单理解这颗芯片其实就是 RT600 + 多模无线 SIP 到一起,但是其 MCU 部分对 RT600 做了精简以及魔改。因为痞子衡对 i.MX RT 特别熟,所以自然想到先在 RT500/600 上调通串行 NAND Flash,然后再做简单移植就大功告成了,没想到被这么个想法坑惨了。

痞子衡手里早就有成熟的 RT1050 系列串行 NAND Flash 驱动(并不是基于官方 SDK 底层驱动),单从 FlexSPI 外设角度来看,RT1xxx 和 RTxxx 差异不太大,基本是兼容的,所以痞子衡很快就将代码从 RT1050 移植到了 RT500 上,工程编译几乎是一把过,然而在 RT500 上实测时却连 NAND 的 JEDEC ID 都无法正常读取,IP CMD 获取到的值永远是 0x0。

由于串行 NAND Flash 驱动代码在 RT1050 上得到过验证,所以其本身不存在逻辑问题,大概率问题还是出在 FlexSPI 外设配置上,于是痞子衡经过 RT1050 vs RT500 各种单元对比测试(此处耗费时间较长),最终发现是由 FLEXSPI_MCR0[7:6] 的配置值不同引起的。

二、关于LEXSPI_MCR0寄存器保留位

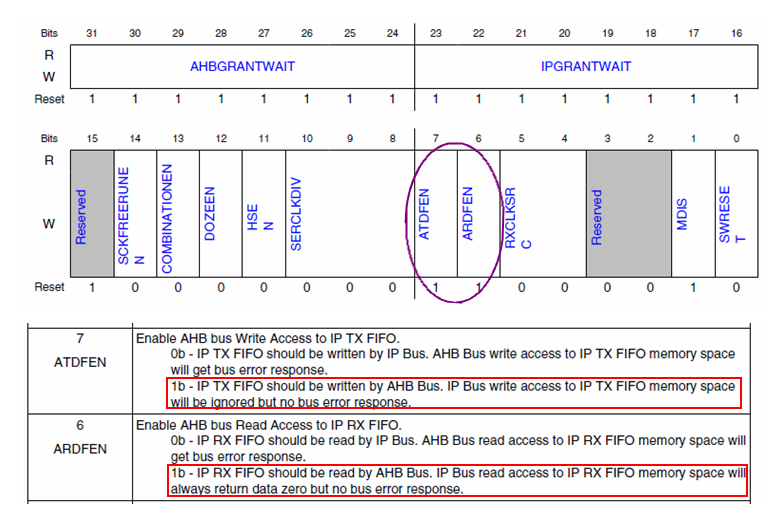

在 RT500 参考手册(Rev.2)以及 RT600 参考手册(Rev1.5)里查看 FlexSPI 模块的 MCR0 寄存器描述,会发现 MCR0[7:6] 是保留位,且复位默认值为 1。

1. RT500 手册描述来看,这两个保留位可读不建议写,且读回值应该是 0 2. RT600 手册对这两个保留位描述是 both bits must be written with ones.

作为对比我们再查看一下 RT 四位数系列(如 RT1050)上相关描述,这两个位并不是保留位,其具体功能是决定访问 IP TX/RX FIFO 数据的方式是 AHB bus 还是 IP bus。默认值 1 表明只能从 AHB bus 访问 IP TX/RX FIFO,这个初始值设置其实稍微有点不合理,毕竟 AHB bus 已经有专用的 AHB TX/RX Buffer 传输数据了。

三、FLEXSPI_MCR0寄存器保留位测试

在 RT500/600 上 FLEXSPI_MCR0[7:6] 是保留位,那这个保留位到底是什么意思?到底是没有这个 ATDFEN/ARDFEN 相应功能,还是单纯不对用户开放而已,这里就需要做一个实验来验证。

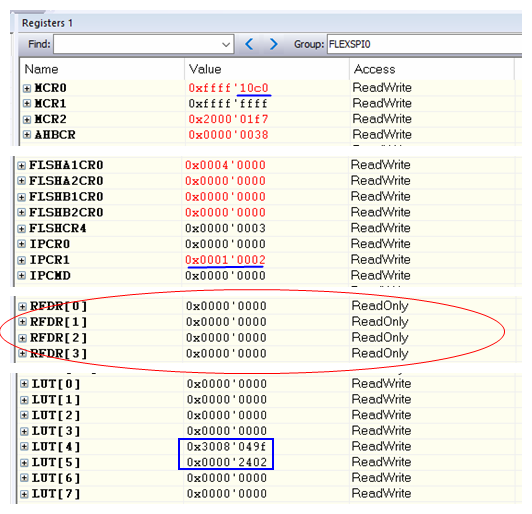

痞子衡在 RT500-EVK 上用连在 FlexSPI PortA 上的那颗四线 NOR 做测试,我们尝试用 IP CMD 发 Read JEDEC ID 命令读取 2byte 数据,在 FLEXSPI_MCR0[7:6] 为默认 2'b11 的情况下,可以看到 FLEXSPI_RFDRx 寄存器全是 0,这意味着 IP bus 根本就没有触发 IP RX FIFO 工作。

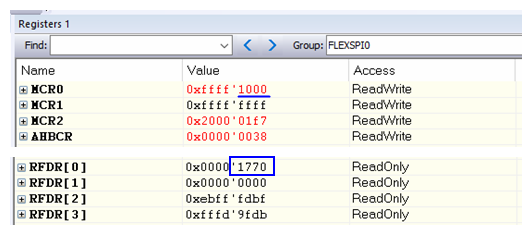

将 FLEXSPI_MCR0[7:6] 设为 2'b00 再测一次,这时可以看到 FLEXSPI_RFDRx 寄存器里开始有数据了,IP bus 触发 IP RX FIFO 干活了。

现在我们知道了,RT500/600 上 FLEXSPI_MCR0[7:6] 虽然是保留位,但是其 ATDFEN/ARDFEN 功能仍然是存在的。

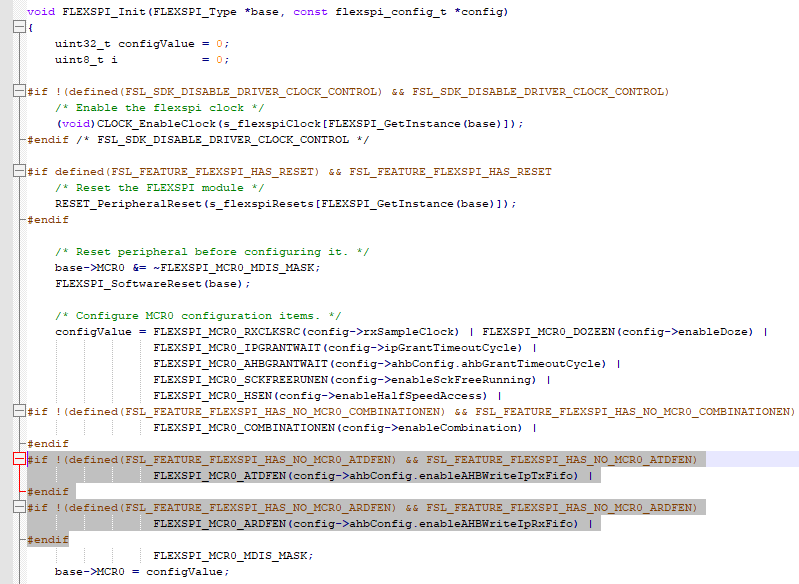

四、SDK驱动处理方法

在官方 SDK 2.14 的 fsl_flexspi 驱动 FLEXSPI_Init() 函数里对于 MCR0 寄存器采取得是忽略初值直接整体赋值的初始化方式,其关于 ATDFEN/ARDFEN 位操作根据特性宏来做条件编译。这样的处理导致 RT500/600 上 FLEXSPI_MCR0[7:6] 永远被重置为 2'b00。例程测试结果上来看似乎没有问题,但是这里存在一定不合理的地方。

1. 在 RTxxx 头文件 FlexSPI 模块寄存器定义里没有 ATDFEN/ARDFEN 位信息,但有如下特性宏定义 #define FSL_FEATURE_FLEXSPI_HAS_NO_MCR0_ARDFEN (1) #define FSL_FEATURE_FLEXSPI_HAS_NO_MCR0_ATDFEN (1) 2. 在 RT1xxx 头文件 FlexSPI 模块寄存器定义里有 ATDFEN/ARDFEN 位信息,无上述特性宏定义

五、经验与教训

回到文章开头,痞子衡推荐的 MCU 外设寄存器谨慎赋值法在这个案例里就完全失效了。我们知道 MCU 外设寄存器有保留位是业界常规做法,但是保留位到底是无功能还是功能不开放,这个要看具体情况。如果应用代码是基于官方 SDK 底层驱动,那么可能不会遇到问题。如果你需要重写底层驱动,想手撕寄存器,那就要特别小心了,关于寄存器保留位的处理是值得深思的。

审核编辑:刘清

-

mcu

+关注

关注

147文章

19121浏览量

403655 -

驱动器

+关注

关注

54文章

9111浏览量

156471 -

寄存器

+关注

关注

31文章

5619浏览量

130400 -

SoC芯片

+关注

关注

2文章

674浏览量

37274 -

Nand flash

+关注

关注

7文章

253浏览量

41691

原文标题:是谁说MCU寄存器一定要谨慎赋值来着?

文章出处:【微信号:pzh_mcu,微信公众号:痞子衡嵌入式】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

芯片I2C通信异常无法读写寄存器破解

i.MXRTxxx系列ROM中灵活的串行NOR Flash启动硬复位引脚选择

32位寄存器,32位寄存器是什么意思

51单片机的寄存器组应该如何设置

C语言位操作在(单片机)寄存器中的应用

痞子衡嵌入式:改动i.MXRT1xxx里IOMUXC_GPR寄存器保留位可能会造成系统异常

CS,IP和PC寄存器

i.MXRTxxx里FLEXSPI_MCR0寄存器保留位会造成IP CMD读写异常?

i.MXRTxxx里FLEXSPI_MCR0寄存器保留位会造成IP CMD读写异常?

评论