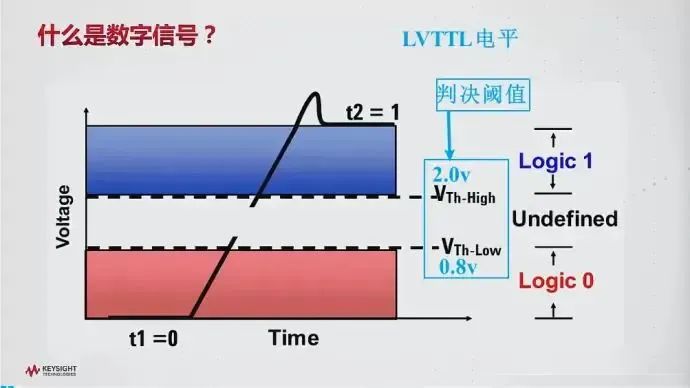

数字信号进入高速状态时,不再是0-1这样方方正正的标准形式。

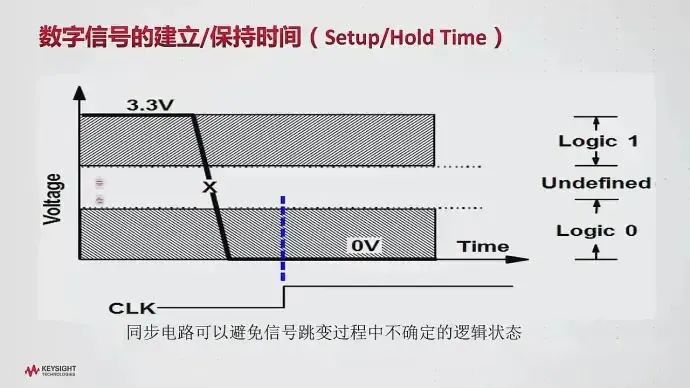

除了电平的影响以外还有时间的影响,采样的时候与数据时序要有一个基本的要求,采样与跳变的时间要有一定的时间间隔,以保证在采样时不采样到跳变。

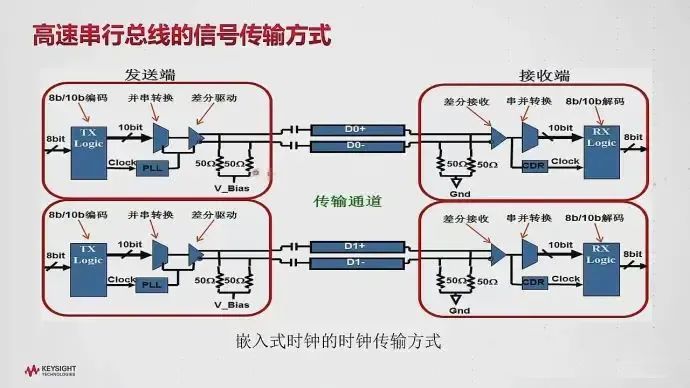

使用串行高速总线,好处:1.省线; 2.不是必要有时钟总线,布线时不需要考虑线长。

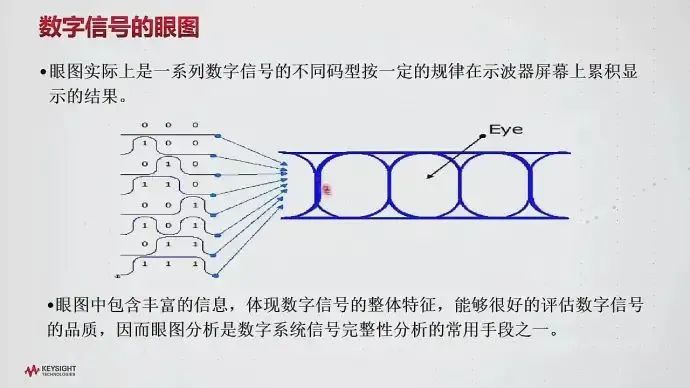

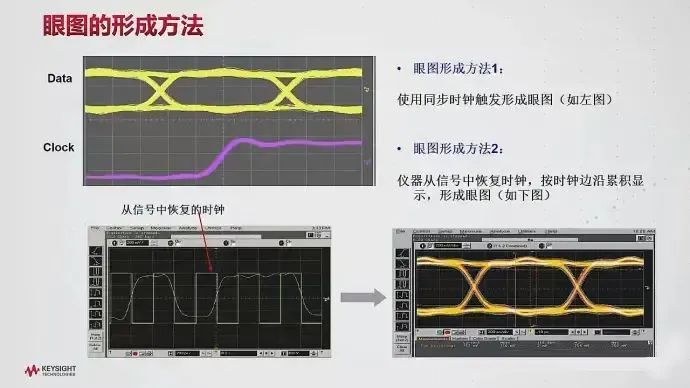

串行总线是通过数据编码,把时钟存在数据流中(眼睛越大越好)。

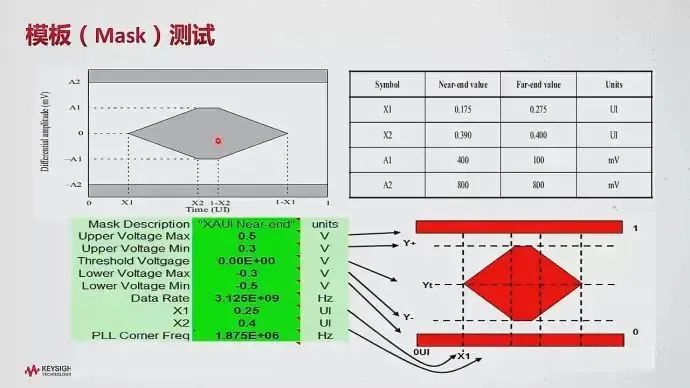

模板测试

眼图压模板表示信号完整性不好

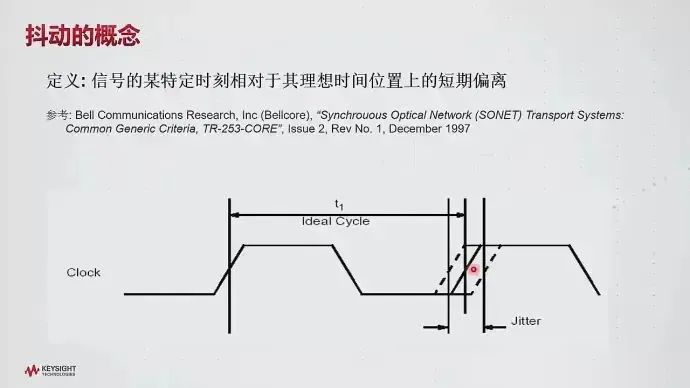

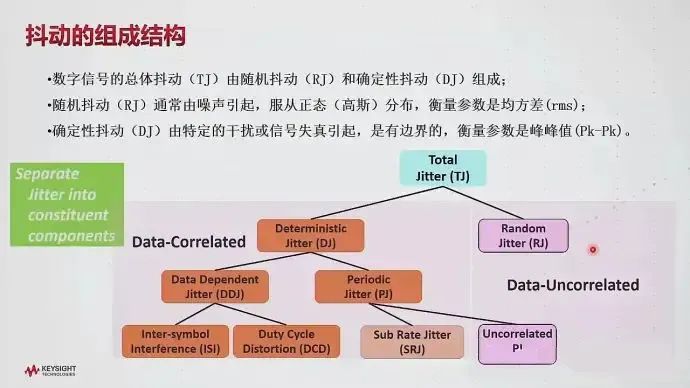

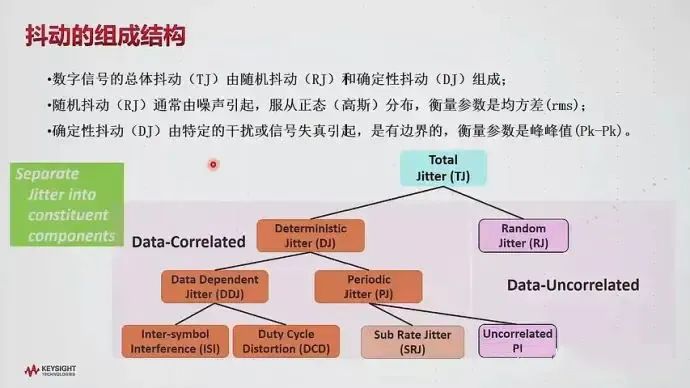

抖动分析模型

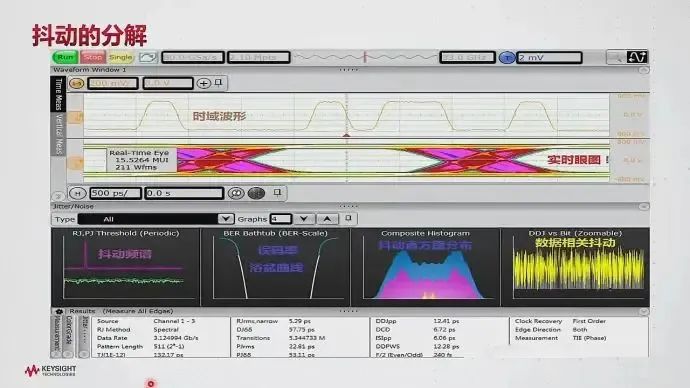

利用示波器上的软件对抖动分解,分析抖动原因。

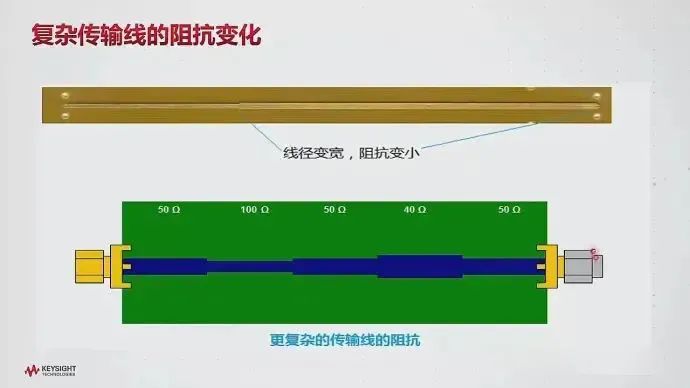

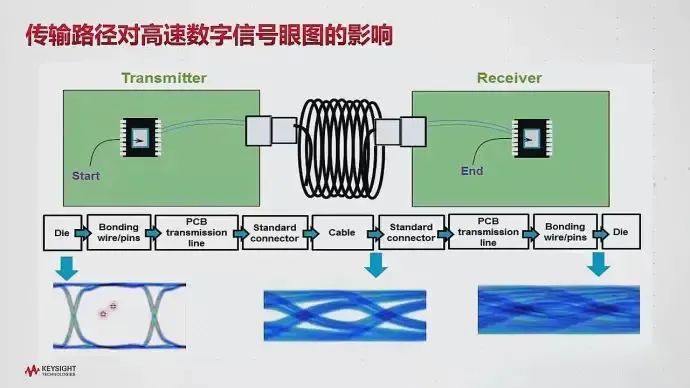

传输线阻抗连续(匹配),可以减少反射。

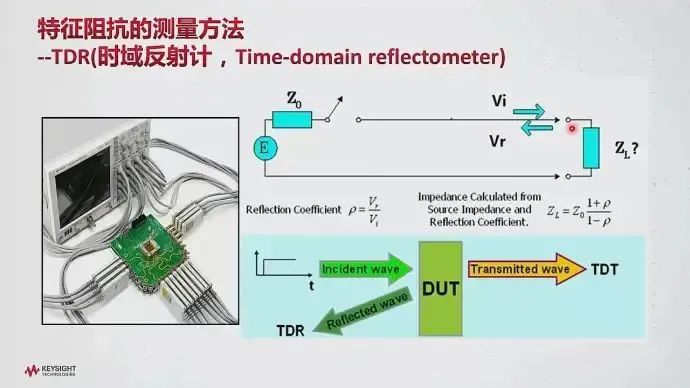

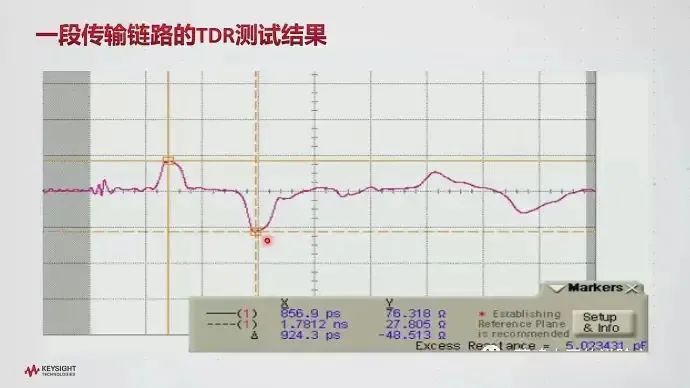

根据反射回来的时间可以判断离我距离,根据反射回来的电压和反射系数可以判断阻抗,一般在峰值点处的的阻抗匹配不好。

阻抗是连续均匀的也不一定最好,要考虑传输损耗,所以除了要控制阻抗,也要控制损耗。

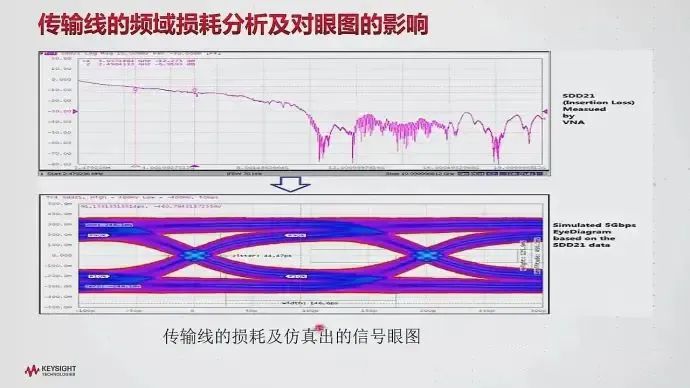

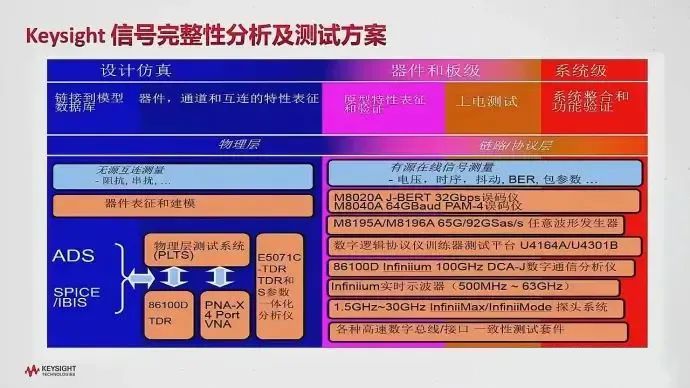

利用多端口矢网分析损耗(S参数曲线)。

随着频率增加损耗增加,根据损耗曲线可以了解传输线的质量,可以根据眼图预知在固定频率的传输效果,或者提前使用信号损耗补偿技术(预加重和补偿)。

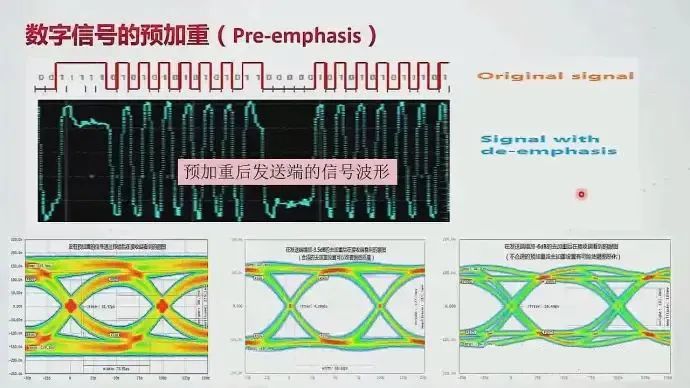

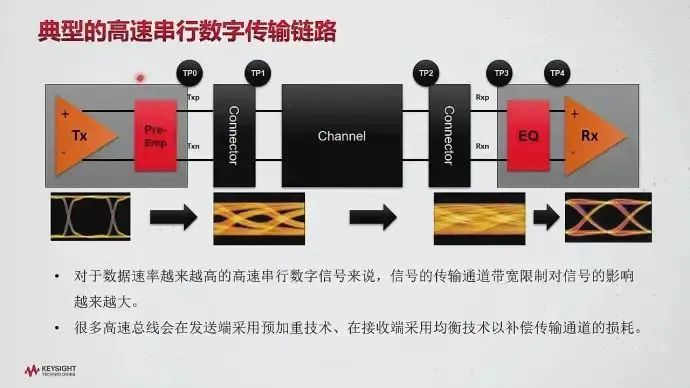

预加重,高频成分更容易损失,所以在发送的时候把高频成分预先加重(幅度加大)(增强),但是预加重的值的设置要和电路相匹配,避免过度补偿,因此目前常常采用多种预加重。

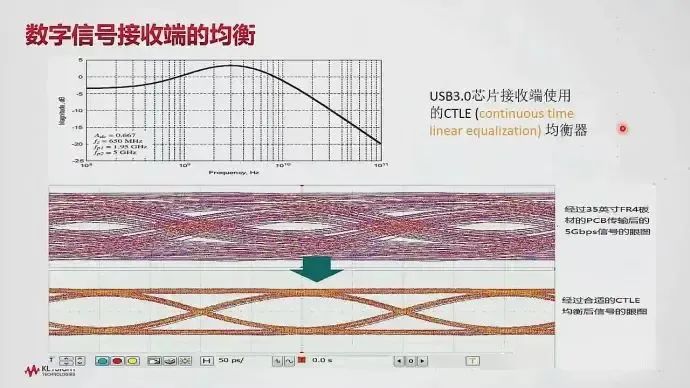

接收端做补偿,叫做均衡(比如CTLE:连续时间线性均衡,还有DFE等均衡方法)。

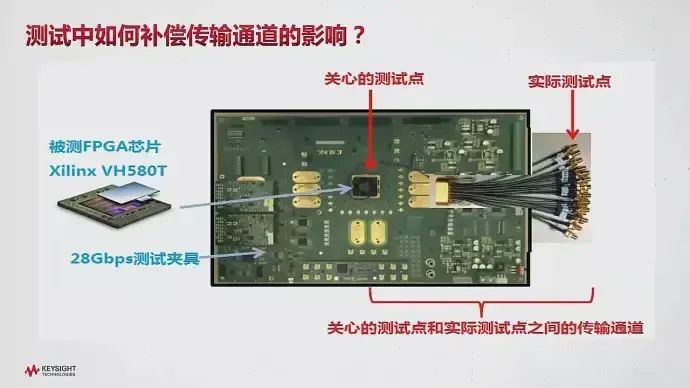

实际测试中,不同管脚由于传输通道,也会有损耗,这时就需要补偿方法(去嵌):实际先把传输通道的S参数求出来,然后在测量中使用软件处理补偿。

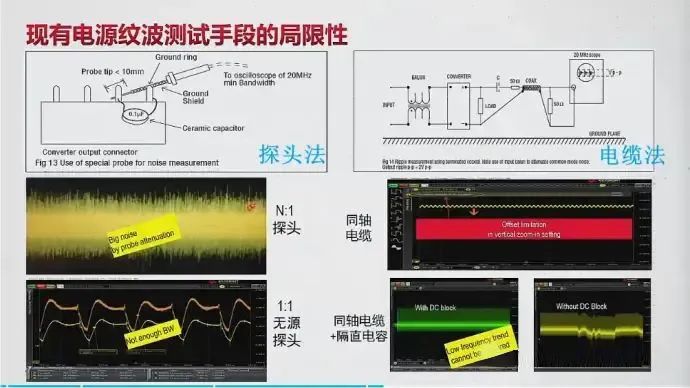

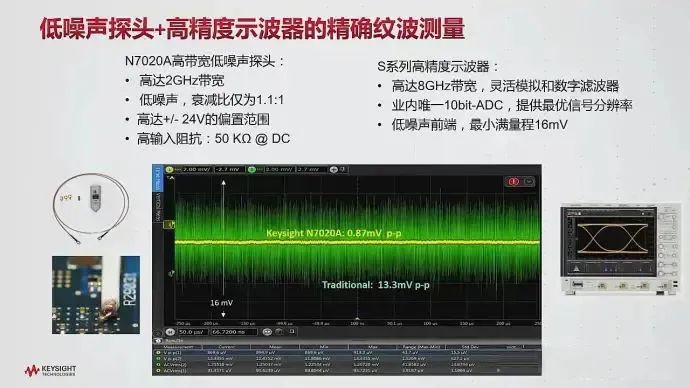

探头一般都是有衰减的,但是示波器知道,示波器显示的时候会放大的,但是这种很难测到很低的噪声(在示波器底噪就很大),用无源的探头不会衰减,但是他的匹配就很难,一种改进方法是使用同轴电缆,一端拧在示波器上,一端剥开,然后点在或者焊在电路上,会得到比较好的测量效果,但是由于要测的电源都是有直流的,如果要测2.5v或者3.3v上面很小的纹波,要把刻度打到很小,但是现在很多示波器的偏置范围在小量程下是不足以把信号拉回来的,可以加隔直电容,但是频率特性就不能很好的说出来了。

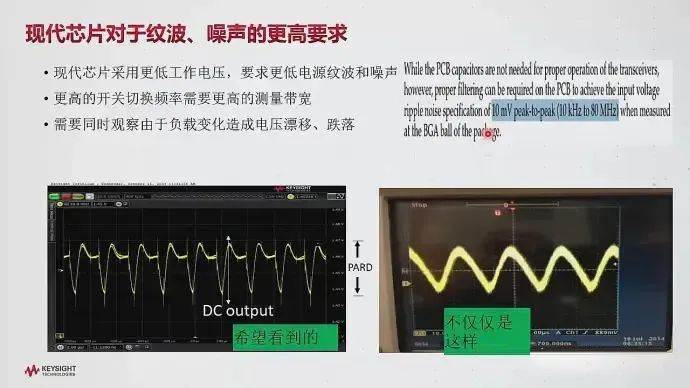

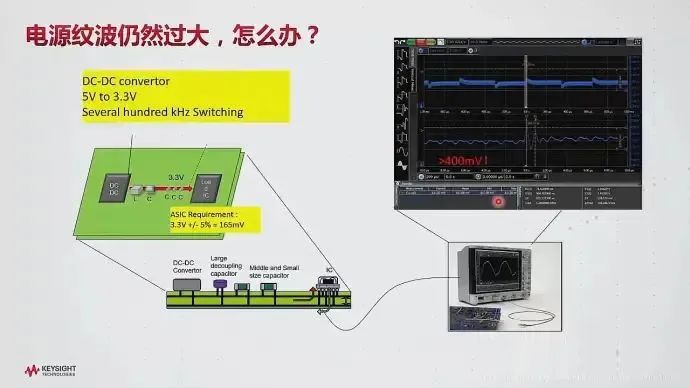

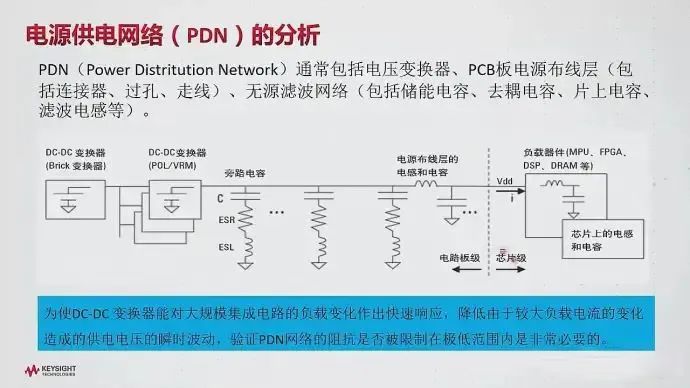

DCDC有几百KHz的开关频率,就有几百KHz的纹波,峰值有400多mV,芯片本身有100多mV。

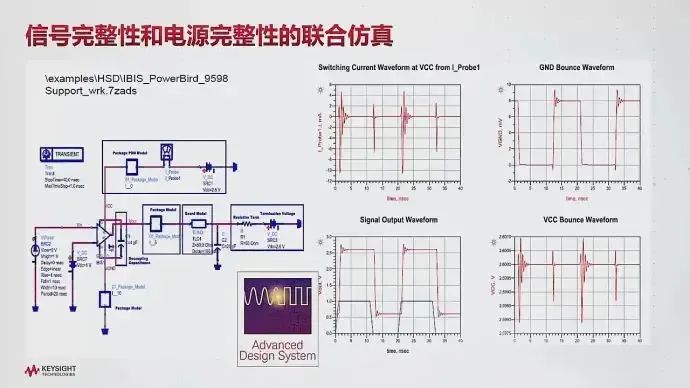

以前的电路芯片模型不支持联合仿真,只支持信号完整性仿真或电源,不能同时仿真,目前支持电源网络(低阻抗)的S参数的联合仿真,通过这种方式尽可能改善电源和信号之间的互相影响。

网络不能把DCDC产生的纹波给充分的滤掉,可能滤波电容不够大,或者滤了低频没滤高频,电容有寄生电阻和寄生电感,在低频的情况下,跟一个电感差不多,没有滤波的效果,所以要优化滤波的网络。

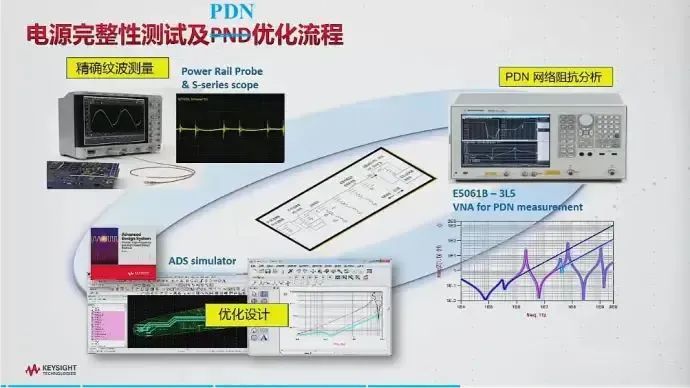

Chrent电源完整性测试和PDN优化流程

1.先用示波器对电源纹波进行测试,如果满足要求最好,不满足就进行上面的改进方法,比如换没有衰减的探头,用同轴电缆测量等等。

2.还不行就PDN网络进行分析,使用矢网在不同频率下测量PDN网络的阻抗,如果在不同频率下的阻抗都很低,说明他的滤波效果很好,如果在低频情况下阻抗很低,但是高频情况下阻抗很高,那么滤波效果不好,需要在某些频点进行一些改善。

一般的网络分析仪的起始频点都是从几百K或者几十M开始,而对于电源分析感兴趣的频点通常都在几Hz到几十K有的时候到几百M,在优化过程中,把现有的PDN网络导进去,然后设置一个目标,比如几K赫兹到1M的频率范围内,我们的阻抗都要小于0.5Ω,让仿真软件自动优化,在哪些位置放电容更有效,节省器件成本和空间。

Chrent答 疑

1.平行布线怎么解决串扰问题?

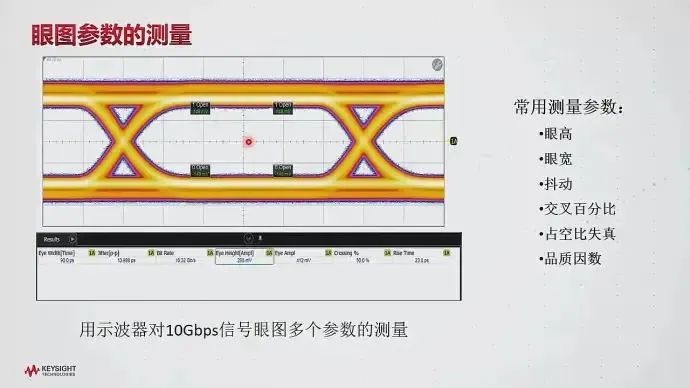

很多高速的走线在传输过程中都会产生EMI辐射,因此平行走线会带来串扰,因此是高速信号研究要解决的一个重要的问题;1. 屏蔽:放在不同的层里,然后用地线隔开;2. 线之间的距离尽量远一点,从测量的角度来看,可以使用示波器的串扰分析软件,分析串扰对眼图的影响(眼高和眼宽)。

2.抖动都是示波器根据自己的算法分析出来的吗?是不是不同的示波器会有不同的结果?

是的,目前业内多采用双狄拉克模型的方法对信号的抖动进行分析和分解,确实可能会存在不同的示波器厂家采用的分析和分解的算法有所差异,不同的示波器的底噪声也是不一样的,在某些长河可以通过一些手段来提高抖动测量的精度,比如信号中发重复性的码型,可以对信号进行反复的平均,这样对码间干扰的测量和分解精度就会更高。

3.眼图很好的话是不是说数字信号没有问题?

眼图本身是一个定性的分析工具,因此还会进行模板工具进行定量的测试,还会对抖动进行分析和分解,因为产品规范里面除了会定义眼图模板的测试以外,还会定义信号里面随机抖动、确定抖动、码间干扰不能超过多少,因此眼图可以作为一个快速的定性的判断手段,但是眼图并不是唯一的手段。

4.如果无法进行模板测试,还有什么手段可以判断信号的完整和信号的正确性?

对于一些低速的数字信号,只需要对一些波形的参数,比如幅度、上升沿、下降时间、周期的测量,但是对于一些高速的总线对信号的质量的判断一般都是对眼图,模板,抖动,进行判断和测试的,如果是并行总线根据时钟一定是能做出时钟的,如果是串行的话,可能有些示波器没有时钟恢复的选件,但是也可以用信号自身出发简单看一下,但是最好是测试一下。

5.测量高频信号的时候怎么避免测量造成的干扰,比如探头衰减的干扰,探头线长的干扰,用普通无源探头会有多大影响?

这个实际是是在问怎么选择合适的探头,要关注探头的带宽,探头的等效的电阻和电容,以及前端电感长度的电感的影响,以及如何弥补电感的影响,对于探头前端的选择可以看现代示波器高级应用。

6.一致性要怎么配合示波器和软件?

一致性测试专门指某些总线的一致性测试,USB、PCIe、PXI总线,这些通常分为发送端和接收端的测试,发送端的测试主要是示波器,接收端的测试主要是误码仪,

示波器(四个)的带宽,不同的总线的要求不一样,比如USB3.0要12.5G带宽,PCIe3.0也要12.5G带宽,PCIe4.0需要20G以上(或者25G)的带宽等等,一致性测试软件(示波器自带的),探头或者电缆,连接和测试夹具,每一种总线都有不同的配置。

7.眼图太差了,如何判断是哪些问题呢?

首先确定测试方法是正确的,比如使用正确的时钟进行恢复,对信号叠加的,如果仍然很差,检查一下发送端到接收端的阻抗是不是连续的,传输通道是不是损耗太大了,比如对不同频点的损耗到底有多大,优化PCB布线或者阻抗等等。

8.预加重对信号的补偿和均衡只能通过眼图来判断是否合适吗?

预加重与均衡和测量没有关系,是在信号里面使用的,示波器是参考均衡器,和规范对比来观察眼图,我们是为了看发送端传输到接收端之后在经过均衡的波形。

9.关于测试点,由于高速信号中作为测试点的过孔和焊盘会导致阻抗不连续,以及等效电容的问题,该怎么处理?

需要仿真软件做仿真,同时和PCB流片厂家沟通。

10.LVDS信号的测试(速率200M)

根据信号的上升沿实际上升时间计算,如果上升沿特别的陡,可能需要8G或10几G的带宽示波器才能测得准,如果上升沿比较缓,可能1G带宽就够了,另外由于LVDS信号是差分的,可能需要差分的探头进行测试,同时要注意LVDS信号在接收端通过需要100Ω端接一下,同时LVDS有专门的时钟,用时钟来进行触发,看信号的眼图。

11.串行通信信号时钟恢复有什么需要注意的?

环路带宽的选择,一般用示波器软件的PRL,她可以跟踪一定频率范围内的信号抖动,如果PRL的环路带宽是一阶的还是二阶的,他的环路带宽是1M的还是2M的还是10M,设置的不对,看到的眼图和抖动就不一样了,所以在设置环路带宽的时候应该参考规范。

12.用同轴电缆测量纹波,示波器内部用AC耦合方式测量,这种方式有什么缺点吗?

如果示波器使用AC耦合,示波器输入阻抗通常是1M欧姆,因为有些示波器比如1GHz的可以在1M欧姆和50欧姆之间进行切换的,通常AC耦合时是在1M欧姆情况下的,50欧姆一般是DC耦合,把示波器打到AC耦合时,1M欧姆的阻抗和电缆50欧姆的阻抗不太匹配,如果做低频纹波的测试影响不大,但是高频下噪声可能测不准,1M欧姆的底噪也是比50欧姆要高一些,AC耦合的情况下看不到直流的变化,比如电压的漂移是看不到的。

13.在纹波测试时,要注意探头的地环路尽可能的小,一般不要用鳄鱼夹那种

它在空间上有很大辐射(相当于天线有很高的电磁干扰),用探头或者小环路的金属探针,避免空间的电磁辐射,噪声(热噪声=KTB(K是玻尔兹曼常数,T是温度,B是带宽))是和带宽成正比的一个量,所以全带宽的底噪声一定是要设置成相对应的(有标准,没有特殊说明可以打20M带宽),也可通过数字滤波来实现。

14.在测试过程中,可能因为带宽不够可能产生虚假的信号?

有可能探头前面的引线太长了,造成了信号的震荡或者不正确的过充,也可能是示波器带宽不够引起不正确过充,有可能引起信号的抖动或者上升沿的哆嗦(高频分量混到低频了),上升时间是不是合适判断一下,更好的方式是用更高的带宽来测试对比一下,直接就判断出来了。

-

电源

+关注

关注

185文章

18716浏览量

261463 -

信号完整性

+关注

关注

68文章

1473浏览量

97776 -

数字信号

+关注

关注

2文章

1055浏览量

48968

发布评论请先 登录

了解信号完整性的基本原理

Samtec虎家大咖说 | 浅谈信号完整性以及电源完整性

普源示波器在信号完整性分析中的应用研究

是德示波器在电源完整性分析中的应用

听懂什么是信号完整性

高速信号完整性与电源完整性(内含答疑)

高速信号完整性与电源完整性(内含答疑)

评论