1、PCIe debug环境说明

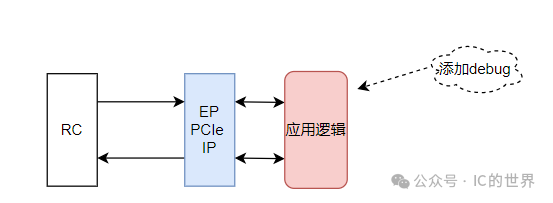

本文将以PCIe EP用户逻辑举例,描述PCIe可以添加哪些定位手段。

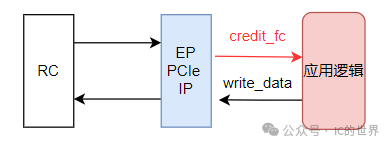

如图所示,PCIe IP作为endpoint与RC对接,用户实现了应用逻辑,与PCIe IP进行交互,交互信号中data格式为TLP报文格式,且交互信号包含相应的控制信号,例如PCIe配置空间和IP相干的配置信号。

常见的Debug设计可以通常有:中断、锁存状态、统计计数和实时状态。

添加Debug设计的目的通常是定位功能故障和性能故障。

功能故障通常有链路不通,出现错包,PCIe部分 function无法访问等等。

性能故障通常速率协商未到最高速率、传输速率不及预期等等。

添加debug手段可以在芯片调试时有效提高定位效率,快速发现并解决问题。

2.用户需要添加的debug手段

2.1.最常见的统计计数

常见的统计技术有,发起的请求数量和收到的请求响应数量、正确的数量和错误的数量、单个function的统计以及所有function的统计。

已发起的dma read请求、已返回的dma read 响应。

已发起的dma write请求、已返回的dma write 响应。

已收到的memory space 访问以及返回的memory space 响应。

2.2.ltssm 状态机

记录ltssm 协商过程,锁存ltssm最近的若干次数值,便于分析ltssm协商过程。

ltssm 实时状态可读 统计ltssm进入L0状态的次数和退出L0状态的次数

2.3.PCIe 关键使能信号

PCIe IP关键信号包含vf/pf_bus_master_en、vf/pf_function_level_reset、hot reset、金手指复位perst,如下表格才采用英文简写描述。

如上的关键信号只有0和1两种状态,都需要记录实时状态、统计0-->1跳变次数、统计1-->0跳变次数

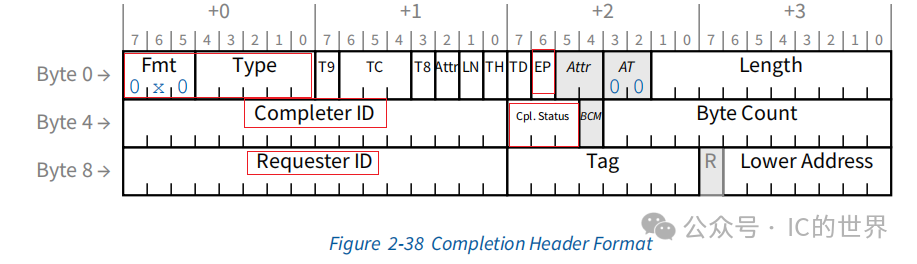

2.4.异常完成报文锁存若干cpld/cpld 报文头信息

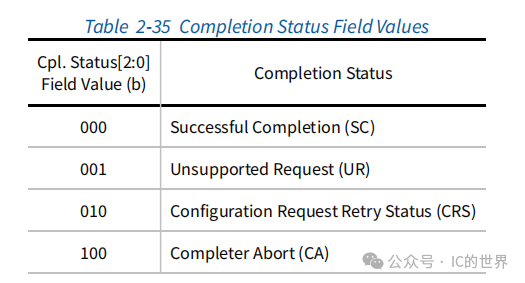

采用ram或者寄存器锁存收到的cpl/cpld报文头信息,可以根据需要选择锁存的字段,如下所示,强烈推荐锁存Completion Status 、EP、Completer ID、Requester ID等信息方便问题定位。

2.5.异常请求debug

发现异常请求时记录异常信息。 场景1:无效function的请求,例如当前PCIe只有128个VF,即VF0~VF127,结果收到了VF128的请求。此时需要锁存请求类型、VF number以及产生错误中断,方便问题定位。

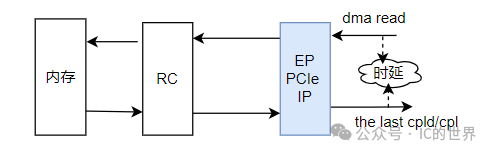

2.6.记录cpld时延信息

为了便于计算性能,EP发起的memory 读请求(俗称dma read),需要统计时延,即从发起dma read请求开始到收到最后一个CPLD/CPL时消耗的时间,并且期望debug设计能够记录不同时延段位的dma read请求数量。debug设计可配置延时上限,一旦超时延时上限,则锁存dma read请求信息,方便调试者定位。

2.7.统计流控信号

当应用逻辑写数据速率过大或者RC端数据处理能力较弱时,RC反馈给EP的credit更新跟不上应用逻辑写数据的速率,会导致EP对应用逻辑产生反压,即credit_fc置1。此时将影响应用逻辑dma write的速率,通过观察credit_fc的统计计数可以初步判断影响性能的因素。

3.结束语

出现问题的原因可能是代码bug,可能是配置的寄存器数值错误,也可能是配置顺序流程不正确,添加debug设计就是为了能够高效定位问题。本文仅仅简单描述了部分需要添加的debug手段,欢迎大家留言补充。

审核编辑:刘清

-

寄存器

+关注

关注

31文章

5588浏览量

129035 -

锁存器

+关注

关注

8文章

952浏览量

43826 -

PCIe

+关注

关注

16文章

1420浏览量

87527 -

TLP

+关注

关注

0文章

37浏览量

16381 -

CPLD芯片

+关注

关注

0文章

18浏览量

12210

原文标题:PCIE定位:PCIe需要的debug设计

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

FPGA的PCIE接口应用需要注意哪些问题

PCIe可以添加哪些定位手段?PCIe需要的debug设计

PCIe可以添加哪些定位手段?PCIe需要的debug设计

评论