本文通过分析低侧栅极驱动器的等效电路来计算如何合理的选取RGATE电阻的阻值,既要保持MOS管的良好开关性能,还要有效抑制振铃的产生。通过计算后的理论值来模拟实验,能够最大化的选取合理的RGATE阻值。另外针对栅极驱动回路中,导通和关断回路进行了不同的结构形态的计算,来研究有无串联二极管带来的影响,同时针对三种结构的电路进行功耗计算,最后文章中给出低侧栅极驱动器Layout中的注意事项,还有不同品牌厂家的芯片驱动峰值电流值不同带来的替换差异。本文可以帮助客户快速理解低侧栅极驱动器的相关计算。

1、RGATE电阻计算

1.1、驱动电阻的构成

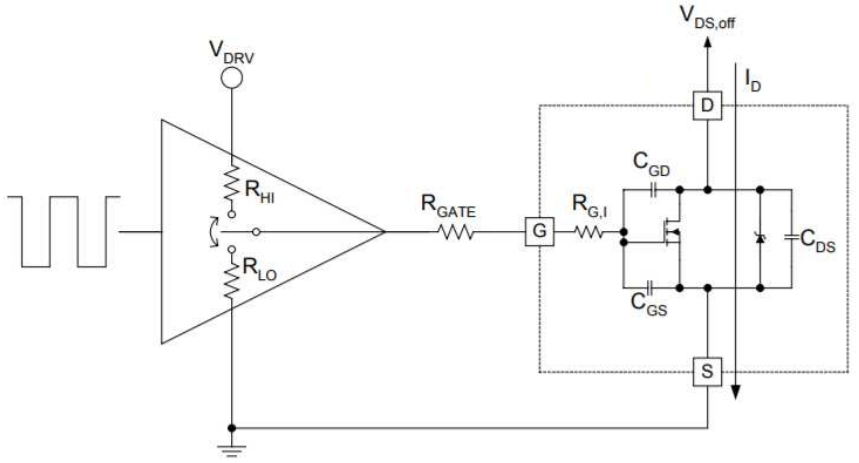

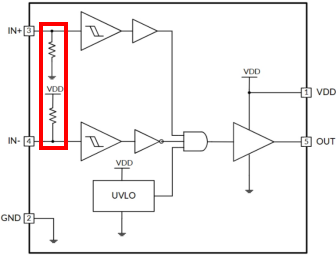

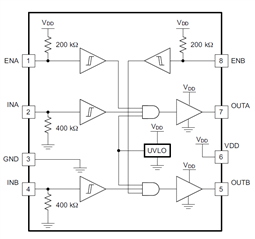

图1-1-1

图1-1-1展示了栅极驱动路径中的串联电阻RG的组成部分:

RHI:驱动芯片输出上拉电阻

RLO:驱动芯片输出下拉电阻

RGATE:外部栅极电阻

RG,I:开关管内部栅极电阻

所以:

以上参数中,RLO可以通过查阅datasheet直接得到,由于驱动芯片内部是NMOS和PMOS并联混合上拉结构,所以在计算中RHI≈RLO *1.5;MOSFET内部的RG,I可以通过查阅datasheet得到,如果规格书内未注明RG,I可使用LCR电桥在GS两端施加1MHz的测试信号,测得Rs值即为RG,I。

1.2、根据实际电路调试 RGATE电阻

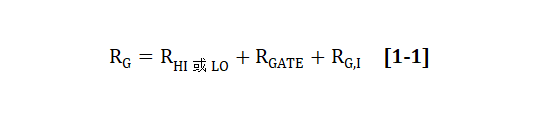

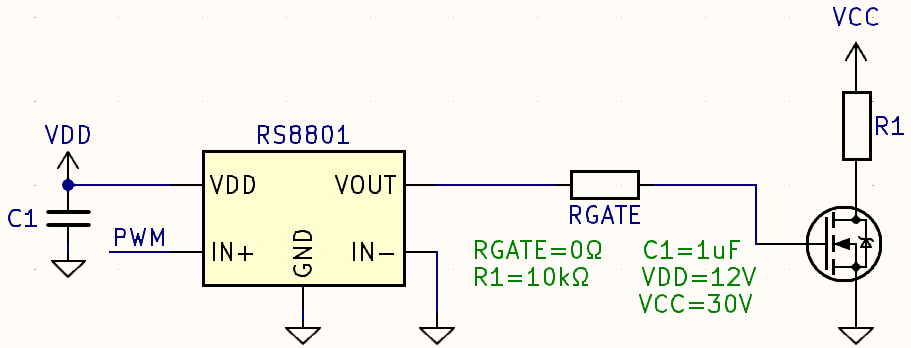

图1-1

图1-1展示了实际电路中的谐振回路,寄生电感LS和输入电容GISS产生高频谐振,而RG则是起到衰减谐振的作用,Q为阻尼系数,一般取0.5。

上述计算是一个逐渐迭代的过程,需要先获得初步数据再进行计算调试。

实例:

图1-2

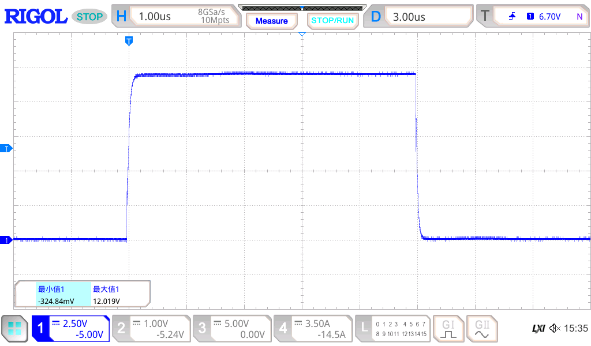

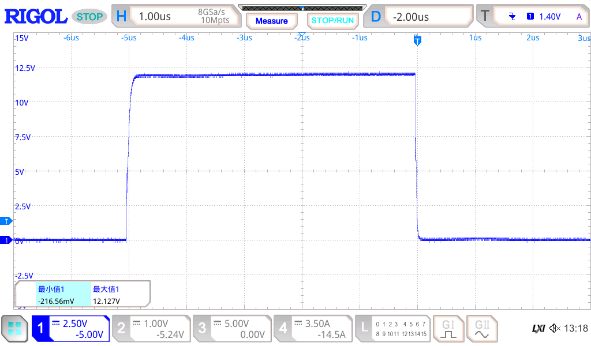

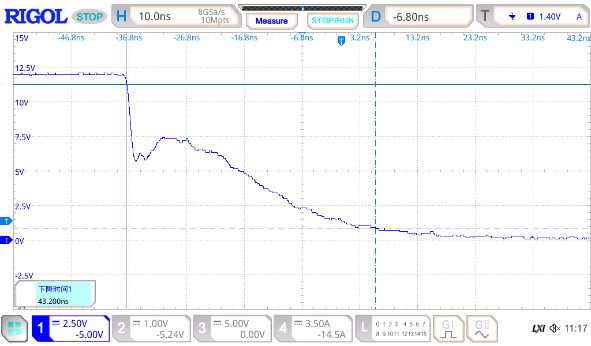

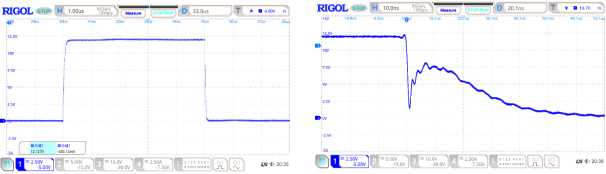

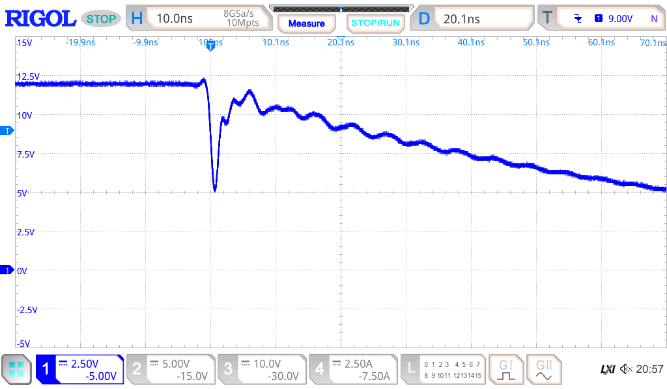

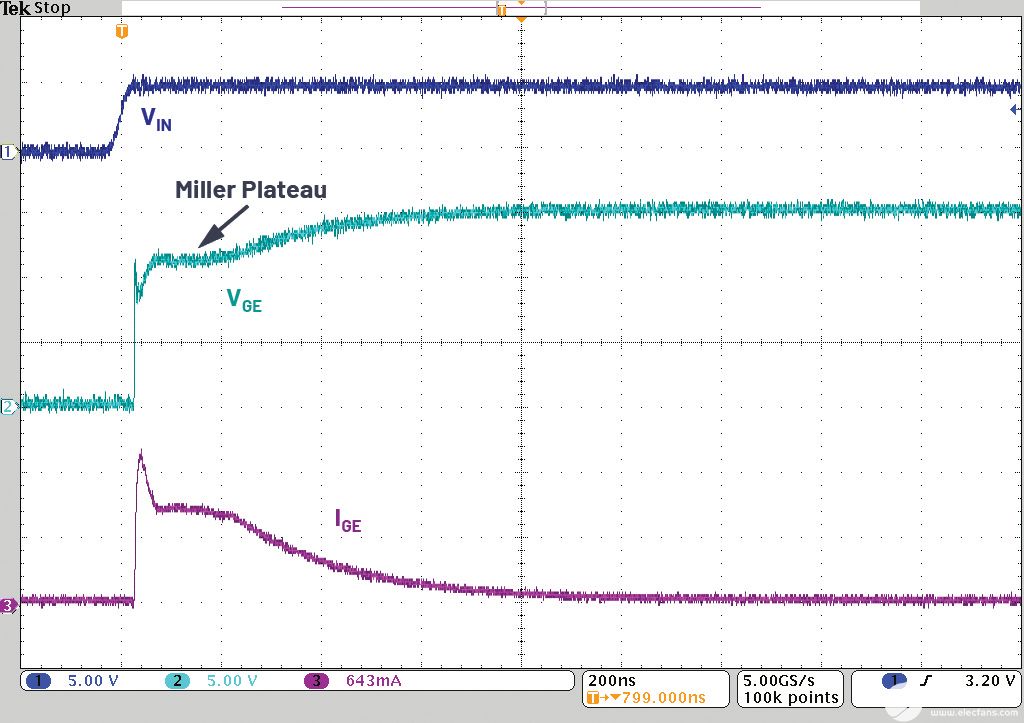

使用RS8801驱动MOS-IRFB3607,外部栅极电阻RGATE取0Ω进行初步实验,使用探头x10档、接地弹簧得到以下波形:

图1-3

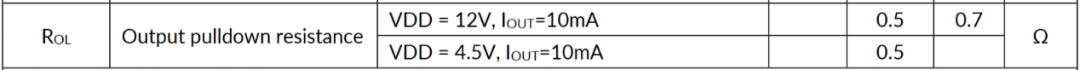

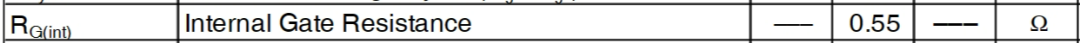

查阅IRFB3607、RS8801手册

图1-4

根据图1-3测量的结果可得:

fR=16.66MHz;GISS=3100pF;计算可得RG=6.16Ω,又因为RLO=0.5Ω;RG,I=0.55Ω,所以RGATE=5.11Ω,取5.1Ω。

图1-5

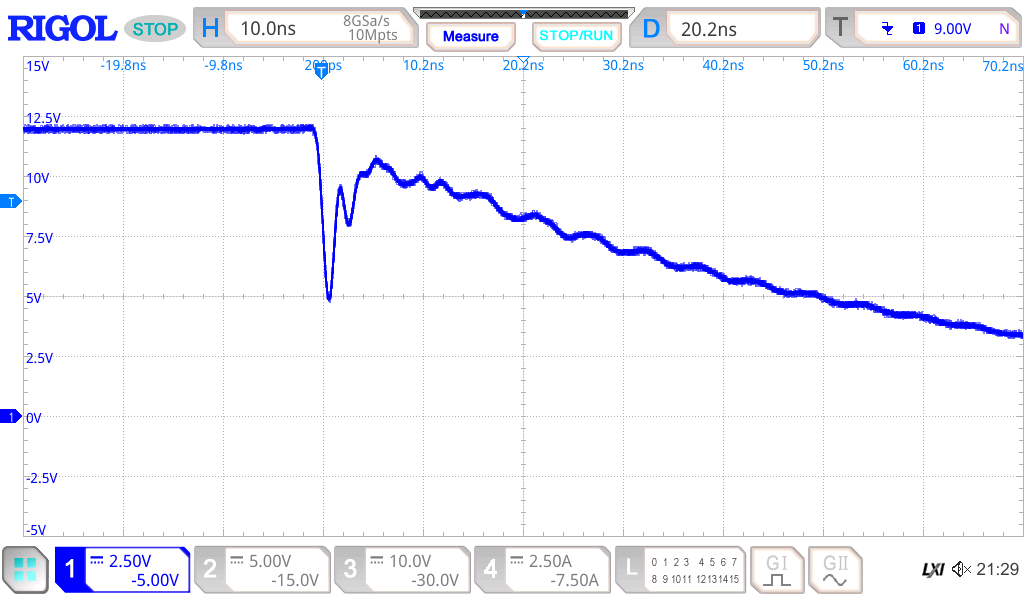

调整RGATE后的波形如下:

图1-6

可以看到上升沿的过冲已从12.77V降为12V,波形改善明显。

2、外围电路

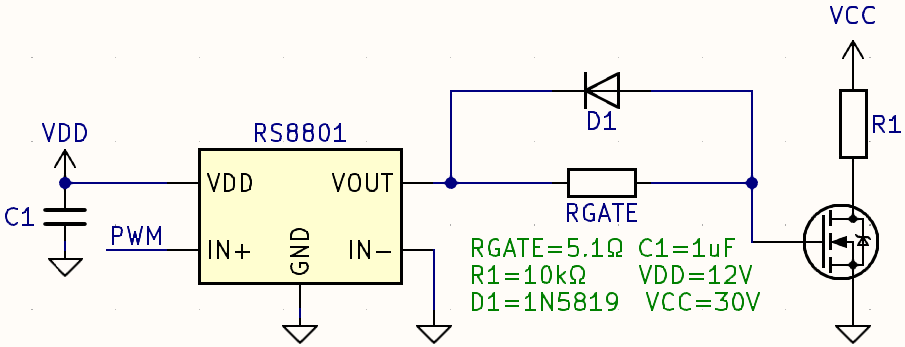

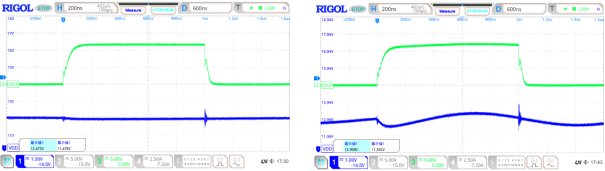

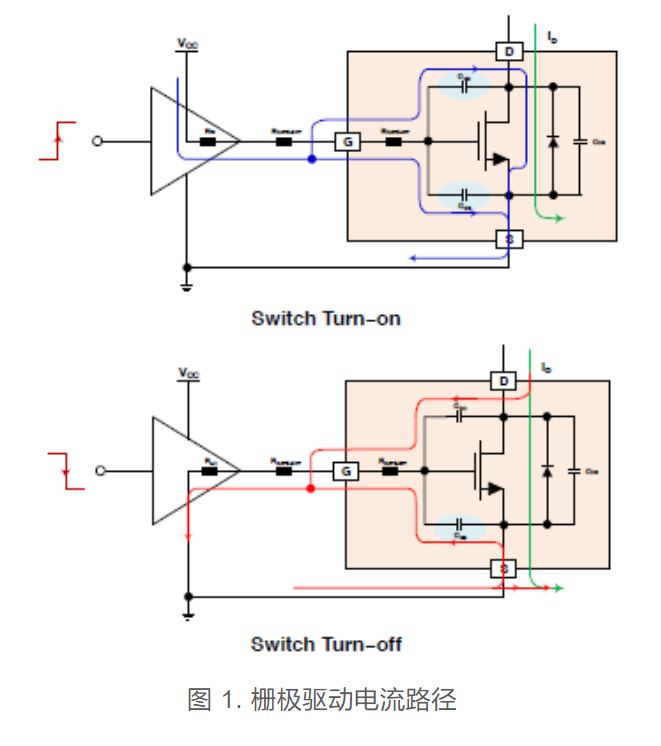

2.1、Sink/Source电流路径分离

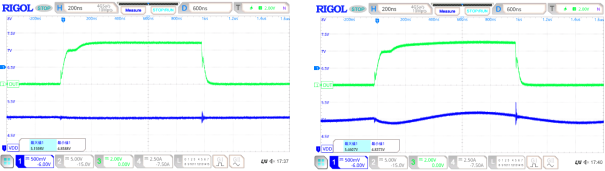

驱动MOS需要遵守 “慢开快关“的原则 ,慢开是指MOS管开通时不能因驱动波形振荡而引起EMI问题,快关则是指MOS管关断要尽可能的快,一方面可以减小关断损耗,另一方面在半桥驱动的场合保证死区时间,防止炸管。但是前文中RGATE阻值已经确定,如何才能做到不改变RGATE的情况下快速关断MOS呢?见下图2-1

图2-1

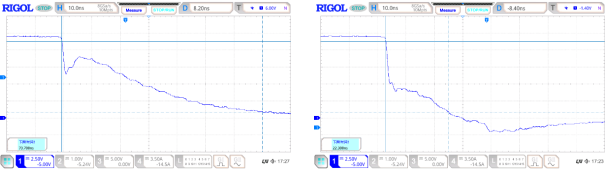

图2-2

左图是没有D1的关断波形,下降沿大约70nS,右图是加了快速关断二极管D1的关断波形,下降沿约为22nS,可以看到D1的效果十分明显。

D1的选型需要关注Trr(反向恢复时间)、开关频率这两个参数,为了不影响开通时的电流路径我们希望Trr越小越好,同时二极管最大开关频率也要匹配开关管的工作频率,所以低Trr、高开关频率的肖特基二极管(Trr一般在10nS左右,频率可以上GHz)十分适用于此应用场合。

但是这又引入了一个新的问题:关断时的电流直接通过二极管而不经过电阻进入驱动器,相较于不加二极管的电路,会让芯片关断时功耗增加,从而提高整个开关周期内的功耗。

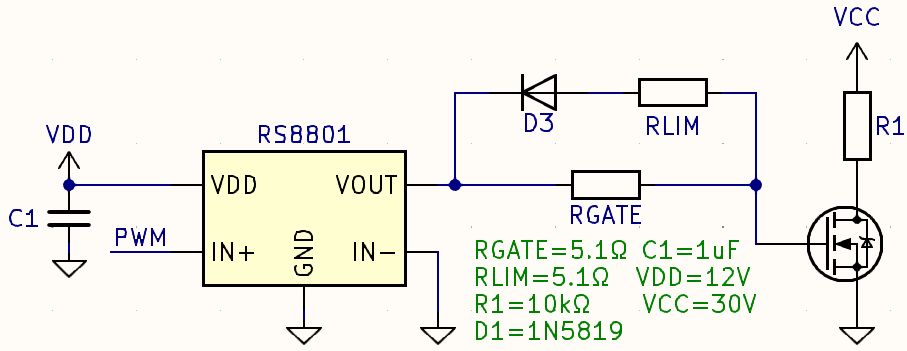

为了保证快速关断二极管优势的同时降低芯片功耗,于是有了以下图2-3电路。

图2-3

图2-3的电路在二极管端增加了一个5.1Ω限流电阻,这样可以减小关断期间驱动器的功耗,从而降低驱动器整体功耗,但是在降低功耗的同时也降低了关断速度(见下图),如果想加快关断速度,可以将限流电阻继续减小。

图2-4

2.2、VDD电容

栅极驱动芯片工作时产生的高速脉冲需要从VDD电容汲取能量,规格书中推荐电容取值1uF,考虑到很多客户可能会习惯性的取100nF作为滤波电容,故以图2-5电路做以下实验(PWM=300kHz):

(a)12V-1uF 和(b)12V-100nF

(c)4.5V-1uF 和 (d)4.5V-100nF

从绿色的OUT波形来看,两种容值效果接近,但从是蓝色波形可以看到使用100nF时,VDD电压波动较大,考虑到芯片的UVLO-OFF阈值电压约为4V,在供电较低的应用中需要关注VDD电压的波动不能触及UVLO-OFF阈值电压。

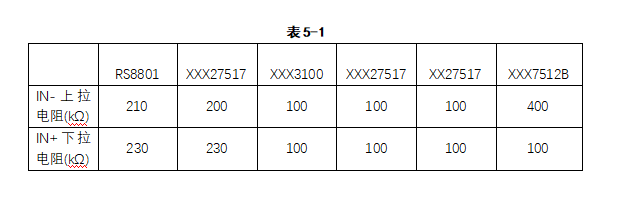

2.3、IN端上下拉电阻

许多工程师喜欢在上下拉的引脚中串联一个电阻后接到电源或地,但是对于RS8801却不建议这么做,原因是芯片内部上下拉电阻为200kΩ,如果在外部串接电阻会使得引脚上产生分压,可能引起电路工作异常。

图2-6

实例:

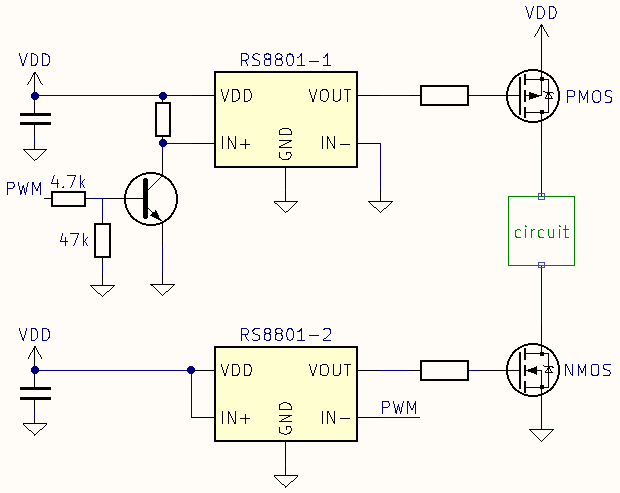

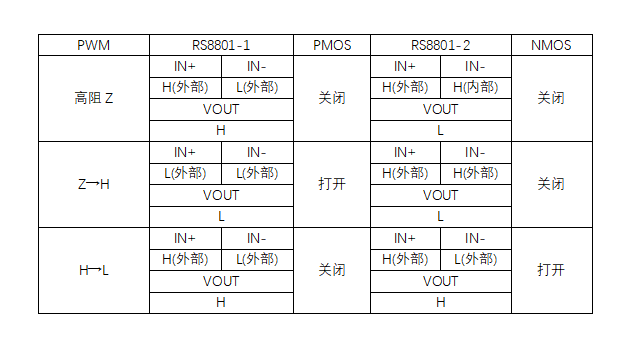

图2-7

上述电路的目的是为了关闭上管供电的同时瞬间打开下管,真值表如下:

表2-1

从真值表来看电路原理没有问题,但上电后发现不给PWM信号的情况下PMOS一直保持打开状态,经排查发现三极管基极始终有2V以上电压,原因是三极管的47k下拉电阻和RS8801-2的IN-引脚内部200k上拉对VDD进行了分压,遂将47k电阻改小,问题得以解决。

从这个案例可以看到一旦外置上下拉电阻取值不合理,就会引起整个电路工作异常,因此建议上下拉的时候不要串联电阻。但是当使用一个信号控制多片RS8801时,三极管(或MOS管)的下拉电阻是必须的,所以遇到这种应用更要重点检查阻值选取是否合理。

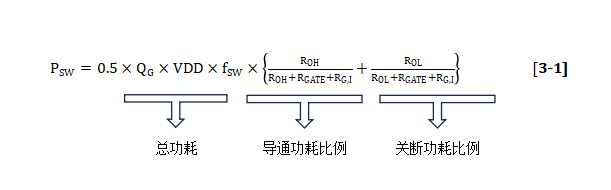

3、功耗计算

栅极驱动器的工作原理是给开关管的输入电容充、放电,所以的芯片功耗只和开关频率有关,而和导通时间、占空比等无关。

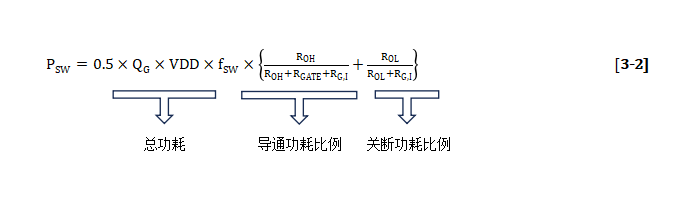

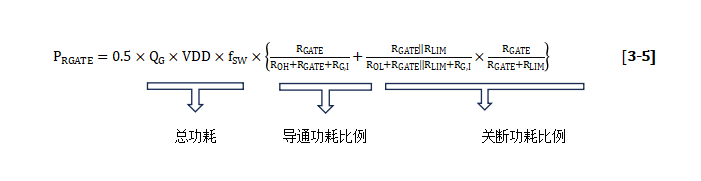

3.1、外围电路无加速二极管

如果芯片外围无加速关断二极管,则按以下公式计算:

以图1-2的电路为例:ROL=0.5Ω 、ROH=1.5*ROL=0.75Ω 、RGATE=5.1Ω 、RG,I=0.55Ω、VDD=12V、QG≈70nC;假设fsw=300kHz。

则芯片功耗为0.025W,随后计算RGATE功耗的时候只需要将两项功耗比例的分子改为RGATE的阻值,可得RGATE功耗为0.2W,此时芯片功耗较低,但是RGATE功耗很大,至少要选取1206封装,如果想减小RGATE封装,可适当增大其阻值。

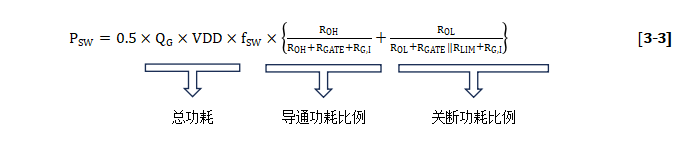

3.2、外围电路有加速二极管

以图2-1的电路为例:ROL=0.5Ω 、ROH=1.5*ROL=0.75Ω 、RGATE=5.1Ω 、RG,I=0.55Ω、VDD=12V、QG≈70nC;假设fsw=300kHz。

则芯片功耗为0.075W,计算RGATE功耗时只需要考虑导通功耗,可得RGATE功耗为0.1W。

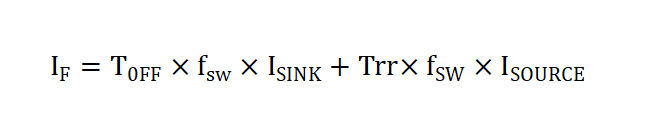

计算D1功耗时公式如下:

IF:二极管连续电流

TOFF:驱动波形下降沿时间

Trr:二极管反向恢复时间

TOFF此处取40nS,Trr取10nS,ISINK和ISOURCE按最大5A计算,可得IF为0.075A,

P =VF x IF

VF:二极管正向导通电压

VF取0.7V,可得二极管功耗为0.052W,使用SOD-123封装即可满足此功耗。

从计算结果来看,此种外围电路几个组件功耗分布相对合理,在实际电路中也是应用相当广泛。

PS:关断阶段RGATE也会流过电流,大小为VF/RGATE,因为其值比流过二极管的电流小很多,故计算时忽略。

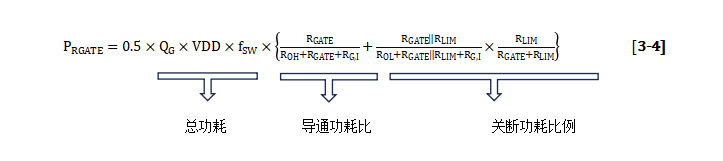

3.3、外围电路有加速二极管和限流电阻

如果芯片外围有加速关断二极管和二极管限流电阻,则按以下公式计算:

以图2-3的电路为例:ROL=0.5Ω 、ROH=1.5*ROL=0.75Ω、RGATE=5.1Ω 、RG,I=0.55Ω、RLIM=5.1Ω、VDD=12V、QG≈70nC;假设fsw=300kHz。

则芯片功耗为0.032W,

计算RGATE功耗时公式如下

则RGATE功耗为0.145W。

计算RLIM功耗时公式如下:

则RLIM功耗为0.044W。

这种外围电路外部组件较为灵活,可以满足各种场合的需求,所以在实际电用中应用最广泛,也是最推荐的一种外围。

4、Layout对性能的影响

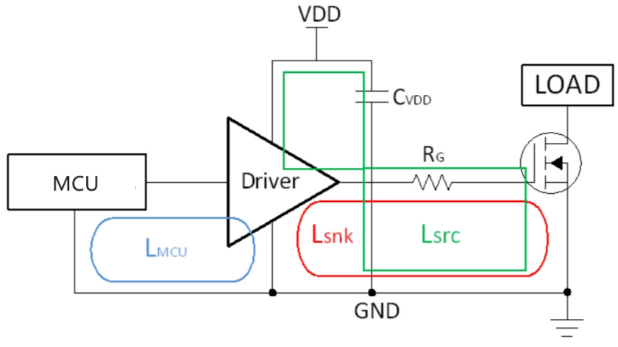

图4-1

栅极驱动器工作的时候有三大环路:绿色的Source环路、红色的Sink环路、蓝色的控制环路

4.1、Source环路

从图4-1可以看到,Source电流路径:

VDD电容正端驱动器上管RGATE开关管输入电容VDD电容负端

为了减小整个环路的寄生电感,需要在布局的时候让VDD电容尽可能的靠近驱动器引脚,同时驱动器输出引脚到开关管的距离也要尽可能短,布线的时候尽可能的拓宽走线。

4.2、Sink环路

Sink电流路径:

开关管输入电容下端驱动器下管RGATE开关管输入电容上端

输入电容下端即开关管的地,驱动器下管即驱动器的地,这两个地之间的寄生电感会引起驱动器OUT端产生负压,从而引起驱动器失效,所以Layout的时候不光要关注输出线,回流地线也是十分重要。

5、替代料的关注点

5.1、不同芯片峰值电流差异对Rg的影响

使用图2-3外围电路,更换其他品牌厂家驱动芯片:

更换第一个国产品牌的驱动芯片-XXX27517

a b

图5-1

输出下降沿有一个因米勒平台引起的回勾,最低电压已经到2V以下,这会让MOS管关闭后再导通,这种异常的关断-导通过程会增加MOS管的损耗,使其急剧发热。

改善方法:拆除D1和RLIM,将RGATE增加至15Ω,波形如下:

图5-2

改善后的波形回勾最低电压为5V,不会让MOS管关闭。

将外围电路恢复成图2-3,再次更换芯片:

更换另外一个品牌的驱动芯片。

图5-3

改善方法:拆除D1和RLIM,将RGATE增加至10Ω,改善后的波形如下:

图5-4

从上述两个品牌芯片调试案例来看,增大RGATE似乎是最简单有效的,但为了稳定波形去掉了加速关断二极管,使整个关断周期超过150nS,这增加了关断损耗,所以说增大RGATE是一把双刃剑。

5.2、IN端内置上下拉电阻的差异

对处于新设计阶段的客户,建议在外部上下拉的电路中不要串联电阻,因为各个品牌芯片的内置上下拉电阻阻值各不相同,可能会出现替代后无法正常工作的情况。

审核编辑:刘清

-

上拉电阻

+关注

关注

5文章

351浏览量

30378 -

PMOS

+关注

关注

4文章

235浏览量

29064 -

LCR

+关注

关注

0文章

126浏览量

20446 -

栅极驱动器

+关注

关注

8文章

686浏览量

38796 -

VDD

+关注

关注

1文章

310浏览量

32189

原文标题:【芯知识】低侧栅极驱动器的应用指南

文章出处:【微信号:run-ic,微信公众号:江苏润石】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

为什么要在汽车PTC模块中用低侧驱动器IC替换分立式栅极驱动器?

TI推出低侧栅极驱动器LM5114

德州仪器(TI)推出单通道低侧栅极驱动器UCC27511与UCC27517

为什么要在汽车PTC模块中用低侧驱动器IC替换分立式栅极驱动器

强鲁棒性低侧栅极驱动电路设计指南

低侧栅极驱动器的应用设计指南

低侧栅极驱动器的应用设计指南

评论