一、什么是 PCB 阻抗?

PCB 阻抗是高频工作时电路的电容和电感的组合,虽然也是以Ω为单位测量,但是与作为直流特性的电阻有些不同,阻抗是一种交流特性,意味着与频率有关,而电阻则不是。

二、阻抗对 PCB的意义

PCB 要实现高速数据传输,阻抗匹配是必须的事情。

以手机USB接口为例,可以实现2个方向同步传输数据、速度快,成本低。常见的2种类型是A型、B型和C型。

USB协议中定义(D+、D-)、(TX+、TX-)、(Rx+、RX-)差分信号线传输数字信号。为了保证传输信号的稳定性,PCB设计差分线必须严格按照差分信号的走线规则。

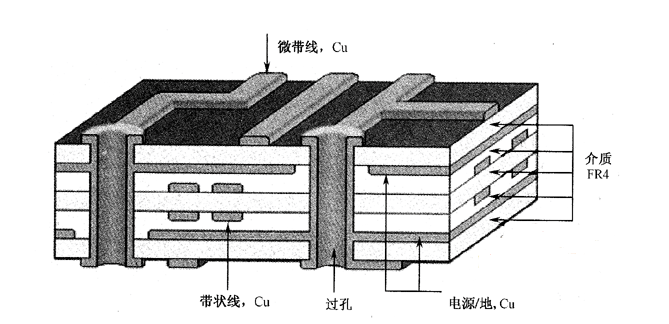

三、多层PCB阻抗走线的一些注意事项

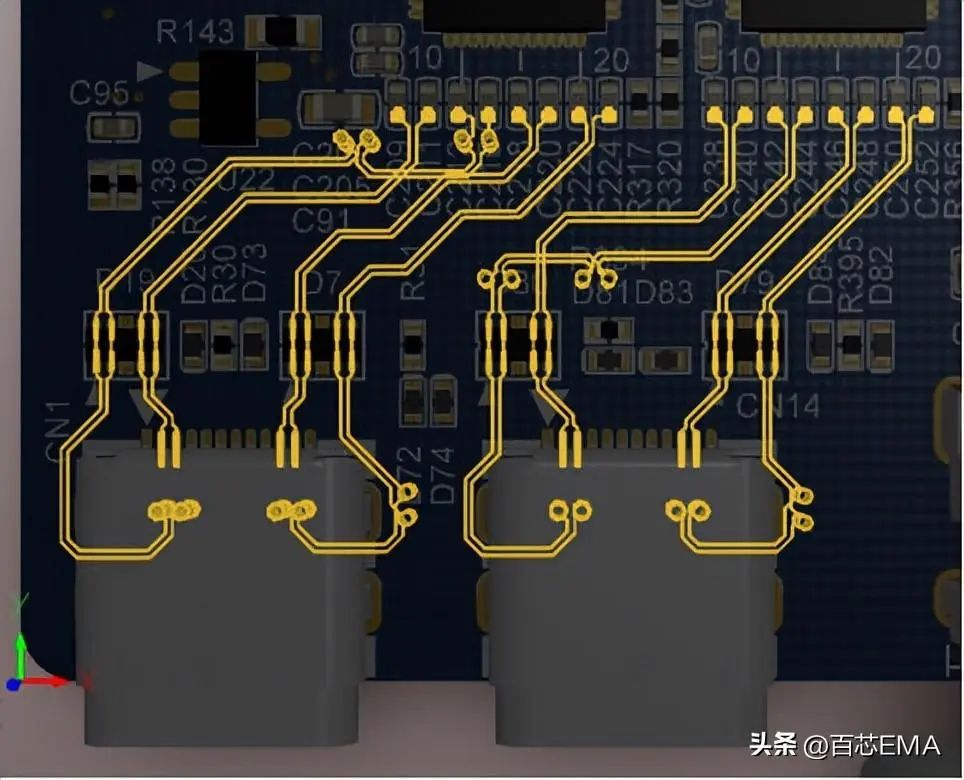

1、元件PAD尽量靠近排列,缩短PADS之间的距离,使差分线尽可能短,过孔尽可能少。

元件PAD尽量靠近排列

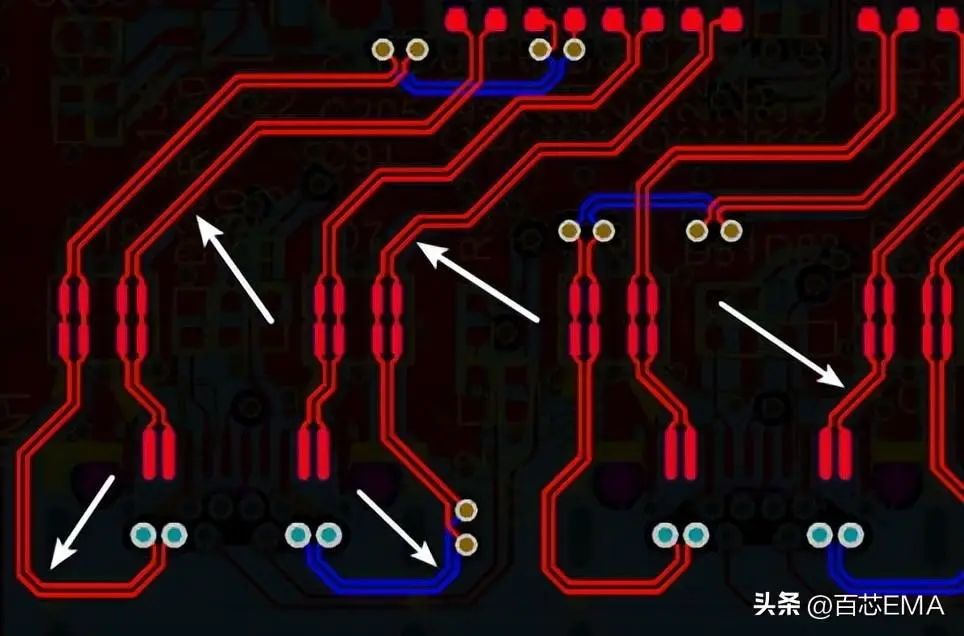

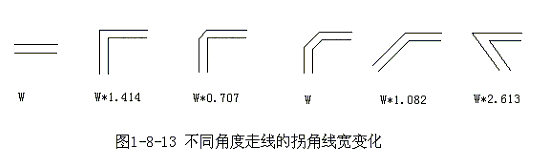

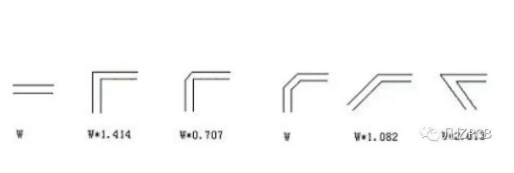

2、路线应平行,对称,不允许走90°角线,应走45°或圆弧走线。线间距控制在4mil以内。

走45°或圆弧走线

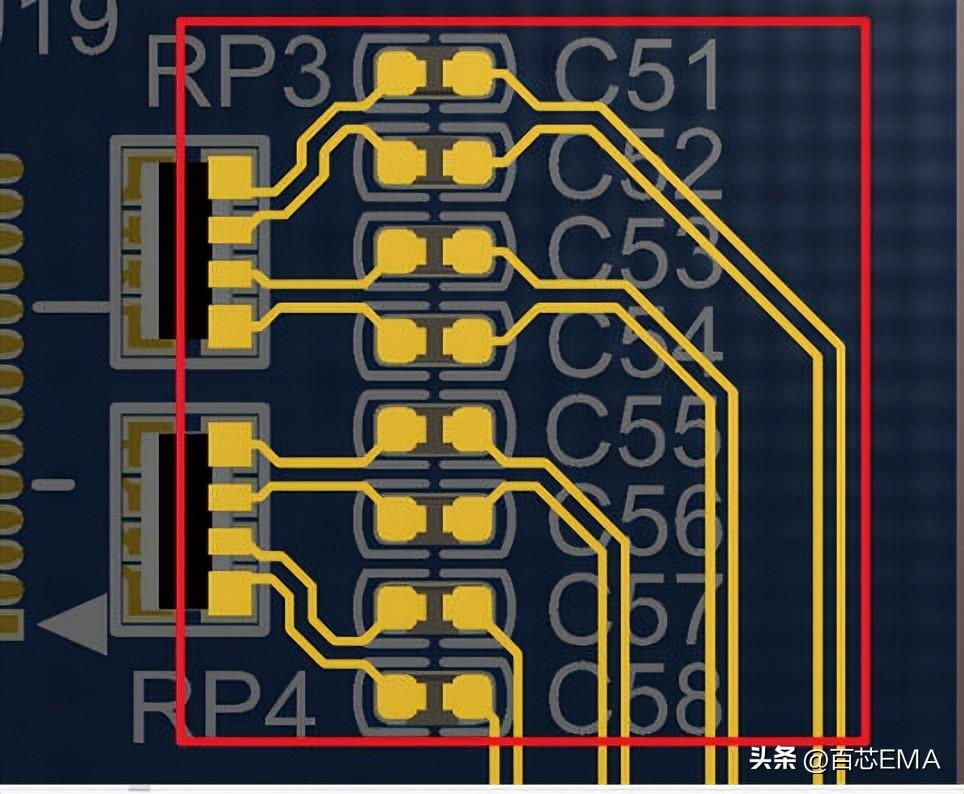

3、串联电阻、电容时,应上下或左右对齐。

上下或左右对齐

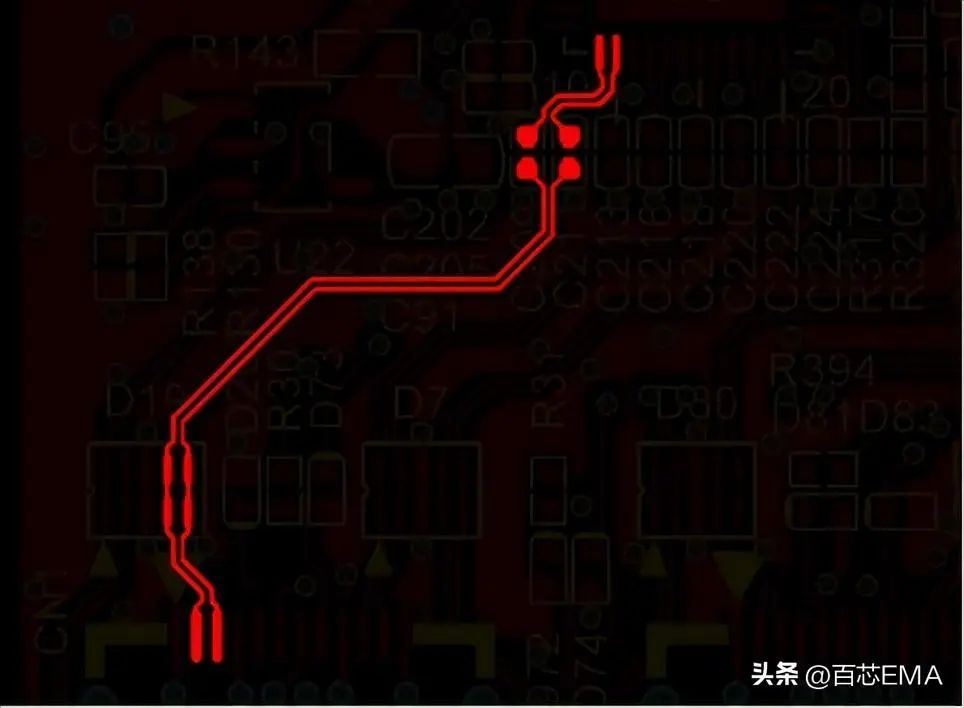

4、差分阻抗线尽量等距、等距,避免时序偏差和共模干扰。

差分阻抗线尽量等距、等距

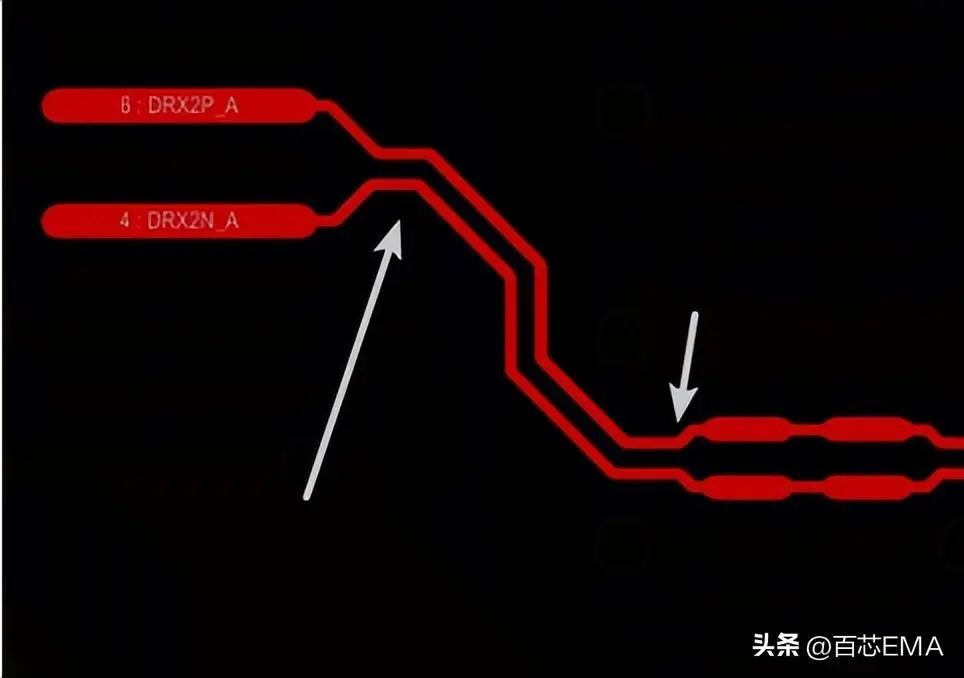

5、由于引脚分布、过孔、走线空间等因素,差分阻抗线长容易不匹配。一旦线路长度不匹配,时序就会发生偏移,从而降低信号质量。因此,需要对差分对的不匹配进行相应的补偿,使线路长度匹配。长度差通常控制在5MIL以内,补偿原则是对出现长度差的部位进行补偿。

对差分对的不匹配进行相应的补偿,使线路长度匹配

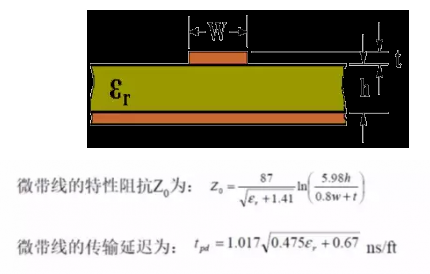

这里举个例子,参数如下:

H1:介质厚度(阻抗线与参考层之间的厚度)

ER1:极板介电常数 4.2-4.6(PP 按 4.2 计算,磁芯按 4.5 计算)

W1:设计线宽

W2:上部线宽 = 设计线宽减去0.5mil

S1:两线之间的距离

T1:铜厚,一般按1oz(1.4mil)计算

C1:C1:基板表面绿油厚度

C2:铜箔表面绿油厚度

C3:绿油厚度基材表面

CER:绿油介电常数3.5

使用阻抗计算器计算,可以得到阻抗约为 100。

原文链接:https://wellerpcb.com/pcb-impedance-line/

审核编辑:刘清

-

串联电阻

+关注

关注

1文章

235浏览量

15613 -

USB接口

+关注

关注

9文章

716浏览量

59223 -

PADS

+关注

关注

83文章

821浏览量

111775 -

PCB走线

+关注

关注

4文章

135浏览量

14588 -

PCB阻抗

+关注

关注

0文章

63浏览量

2769

原文标题:PCB阻抗线怎么走线?看这一文!

文章出处:【微信号:fcsde-sh,微信公众号:fcsde-sh】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

高速PCB设计中优化走线的策略阐述

PCB设计中直角走线的布线方法

什么是PCB线路板走线阻抗

PCB的走线结构

PCB阻抗线怎么走线?多层PCB阻抗线走线技巧分享

PCB阻抗线怎么走线?多层PCB阻抗线走线技巧分享

评论