noise shaping(NS) SAR ADC最近两年的发展趋势,对不同paper中的实现方式进行了分析并对其优缺点进行概括。虽然noise shaping SAR ADC这一结构是在2012年才被提出来,但经历这近十年的发展,其在论文中的实现方式也在不断进步,受到了广泛地研究,因此,下文着重介绍分析ISSCC 2020 和 ISSCC 2021发表的关于NS SAR ADC的paper。

首先,在具体谈paper之前,先说说目前noise shaping SAR ADC的类型。按照NS的方式,即如何extract quantization noise和实现quantization noise的filtering,NS可分为CIFF(cascaded noise feedforward),EF(error feedback)以及两者的hybrid。CIFF和EF的具体区别,这里就不做具体解释了,有兴趣的可以去看看'[1]J. Fredenburg and M. Flynn, “A 90MS/s 11MHz Bandwidth 62dB SNDR Noise-Shaping SAR ADC,” ISSCC, pp. 468–470, Feb. 2012.' 和 ‘[1]A S. Li, B. Qiao, M. Gandara, D.Z. Pan, N. Sun, A 13-ENOB second-order noise-shaping SAR ADC realizing optimized NTF zeros using the error-feedback structure. IEEE J. Solid-State Circuits 53(12), 3484–3496 (2018)’这两篇paper,分别解释了CIFF和EF的工作原理。而hybrid EF-CIFF的工作原理在我上一篇的日志里面也有分析。

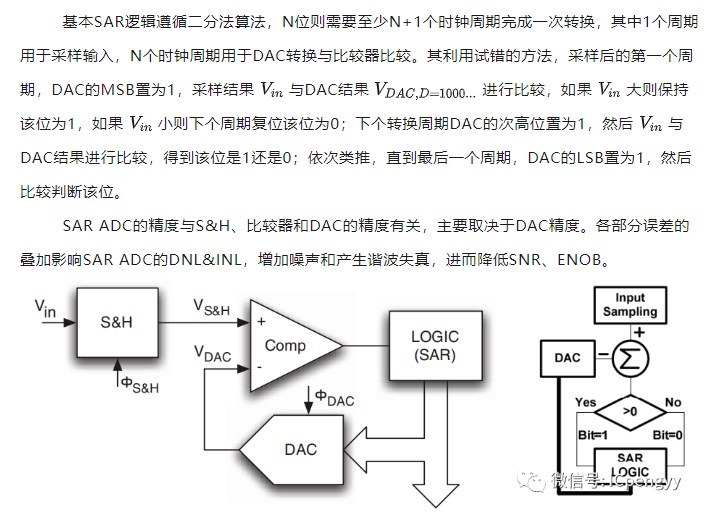

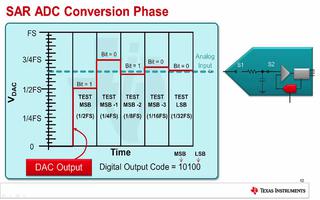

现在开始说一说从NS SAR ADC被提出以来遇到的主要问题以及如何发展的。NS SAR的主要优势在于其能够在传统SAR ADC的结构内部实现Delta-sigma的操作,这无论从能量和面积上讲都是非常高效的。在[1]提出NS SAR的理论基础过后,其首先面对的问题有三点:1. 用于sample residue voltage的capacitor处引入额外的KT/C noise;2. 使用高功耗的static integrator,与低功耗的传统SAR ADC的特点相矛盾。 3. 使用Multi-input-pair comparator,使得比较器的噪声进一步增加。首先针对第一点,有些文章开始使用buffer来消除额外的KT/C noise限制,但引入buffer会带来一定的限制,如果使用static buffer,那么静态功耗则会增加;而如果使用dynamic buffer,则其会受到variation和low intrinsic gain的限制。针对第二点,为了避免引入功耗大的static integrator,有些文章开始采用fully passive noise shaping,即只使用switches和capacitors来实现filter,从而大大降低filter的功耗 ;这一方案同样也有一定限制,具体体现为由于在charge sharing过程中的charge loss,导致无法实现agressive noise transfer function,大大减小了NS对ADC精度的提升;有文章利用comparator输入尺寸的比例来实现对residue voltage的gain,但实际上更多comparator input-pair的引入导致了更为严重的comparator noise,有可能成为设计的瓶颈。 针对最后一点,这两年的文章大多都采用了summation capacitor的来实现加法,这种方式允许只是用传统的一对input pair的comparator。

目前有很多文章都采用了带gain的buffer来补偿filter的charge loss从而实现agressive noise transfer function,具体我会在后面论文分的分析里面提到。

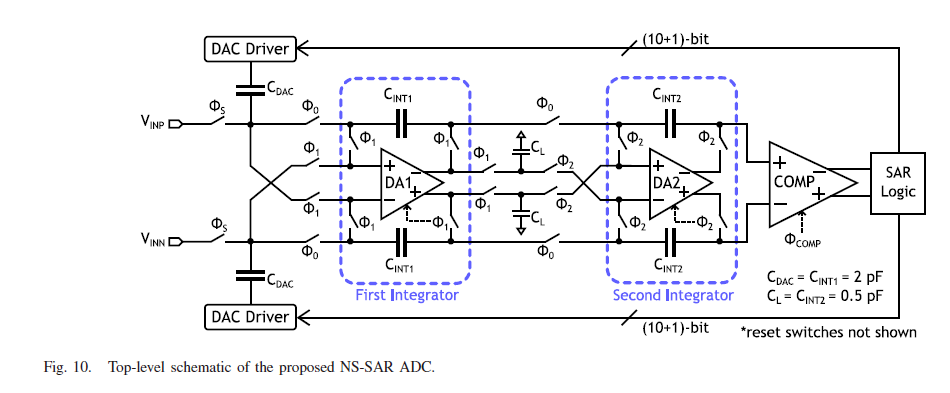

paper 1:'[3]X.Y. Tang, X.X. Yang, A 13.5-ENOB, 107-μW Noise-Shaping SAR ADC With PVT-Robust Closed-Loop Dynamic Amplifier, in IEEE Journal of Solid-State Circuits ( Volume: 55, Issue: 12, Dec. 2020), pp. 3248 - 3259'

这篇文章在我印象里是第一篇采用fully dynamic并且同时实现PVT robust aggressive NTF的。这篇文章的主要意图是解决传统的dynamic amplifier low gain以及无法保证PVT robustness的问题。因此,文章提出使用closed-loop floating inverter amplifier,其同样作为dynamic amplifier,由于其current reuse以及较稳定的输出共模电平,使之具有high gain和PVT robust的特点。文章巧妙的使用CDAC和summation capacitor作为input capacitor和feedback capacitor,同时summation capacitor也作为integrator的输出,这样大大减少了area overhead。文章实现了PVT robust的2nd order CIFF NS,虽然阶数并没有太高,但仍达到了接近84dB的SNDR以及181.5dB的FoM。

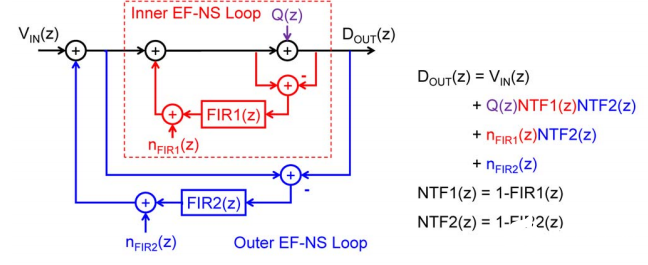

paper 2: '[4]J. Liu, B.Y. Zheng, A 4th-Order Cascaded-Noise-Shaping SAR ADC with 88dB SNDR Over 100kHz Bandwidth, in 2020 IEEE International Solid- State Circuits Conference - (ISSCC)'

这篇文章提出的cascaded NS方法非常巧妙。在这之前,如果要实现高阶的NS,大多数采用switch和capacitor filter的文章都会面临filter capacitor mismatch的问题,大大降低NS的有效性。这一篇文章提出了另一种方法,即cascade两个二阶的FIR filter,这样实现的NTF成为了两个二阶high pass filter的乘积,有效减小了capacitor mismatch的影响。除此之外,这种方法也简化了filter switch的control signal,更易于实现。从filter noise的角度来讲,第一个FIR filter的noise会被第二个FIR filter shape,这使得第一个filter使用的capacitor的值可以减小同时不会引入过多的noise。但文章采用了open-loop static buffer,导致其性能在功耗上和PVT robustness方面并没有达到最优。

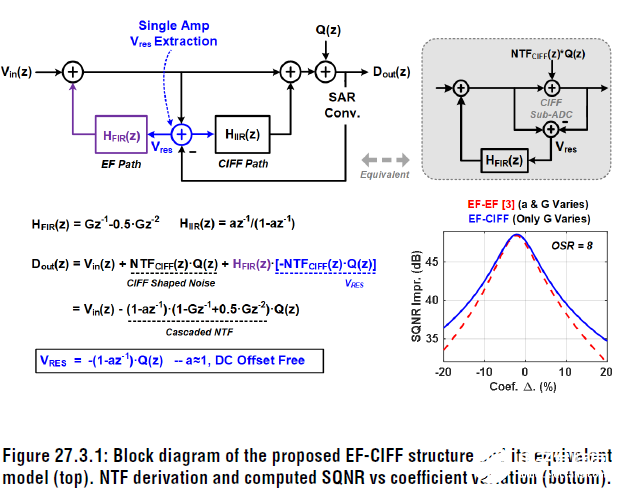

paper 3: ‘[5]TH. Wang, R. Wu, A 13.8-ENOB 0.4pF-CIN 3rd-Order Noise-Shaping SAR in a Single-Amplifier EF-CIFF Structure with Fully Dynamic Hardware-Reusing kT/C Noise Cancelation,in 2021 IEEE International Solid- State Circuits Conference - (ISSCC)’

这篇文章在NS工作原理部分就不展开了,可以参考上一篇日志。这篇文章提出的另一个比较重要的点在于其将sampling noise cancellation(SNC)使用到了NS SAR当中,大大降低了SAR ADC前级driver以及reference buffer的设计难度。关于sampling noise cancellation method,感兴趣的话可以参考这篇文章引用到的文章,从实际应用角度是非常有意义的。

审核编辑:黄飞

-

SAR

+关注

关注

3文章

448浏览量

48056 -

adc

+关注

关注

100文章

7946浏览量

556867 -

比较器

+关注

关注

14文章

1936浏览量

112077

发布评论请先 登录

SAR型ADC的结构及采样过程

请教关于SAR ADC的噪声谱计算

SAR型ADC应用

SAR ADC输入注意事项

一种18位SAR ADC的设计实现

SAR型ADC原理简析

SAR ADC的采样过程和模拟输入结构

关于NS SAR ADC的paper结构介绍

关于NS SAR ADC的paper结构介绍

评论