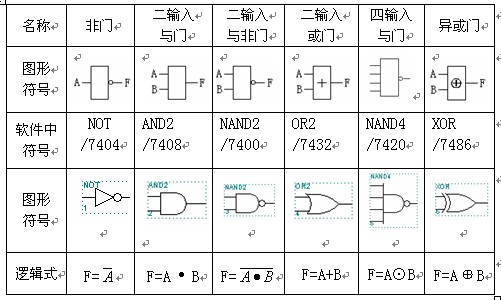

同或门

同或门(XNOR gate或equivalence gate)也称为异或非门,是一种逻辑门电路。同或门的特点是当两个输入信号相同时,输出为低电平;当两个输入信号不同时,输出为高电平。在实际应用中,同或门常常用于实现两个信号的相同性检测,例如比较两个数字是否相等。在数字逻辑电路中,同或门可以由异或门和与门组合而成。

同或门的符号为“⊕”,表示两个输入的异或运算。同或门在逻辑学里又称为“双条件”,或称为“当且仅当”(if and only if)。所有输入信号都相同时才输出真,只要有一个以上不相同时就输出假,也就是异或门的反面。

同或门在电路设计中常常用于实现两个信号的相同性检测,例如比较两个数字是否相等。在实际应用中,同或门可以用于实现数据校验和差错检测。在通信领域中,同或门可以用于实现数据校验和差错检测;在计算机领域中,异或门可以用于实现数据的位操作和加密解密等算法。

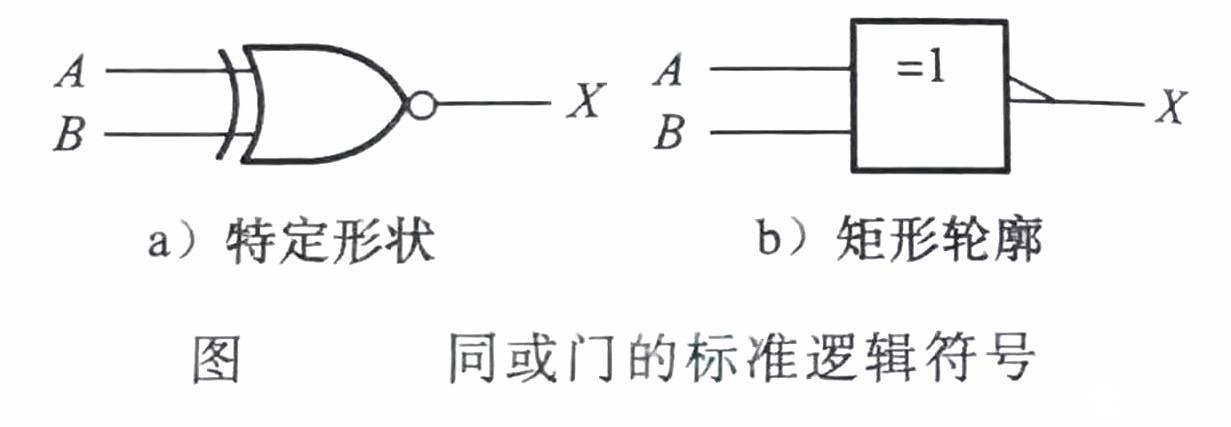

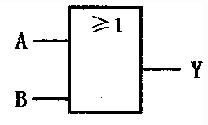

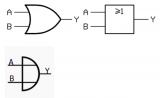

图中给出了同或门(XNOR)的标准逻辑符号。

与异或门一样,也只有两个输入端,同或门输出端的小圆圈说明输出结果跟异或门输出相反,当输入的两个电平为相反电平时,同或门输出低电平。A, B是输入变量,x是输出变量,同或运算可以描述如下:

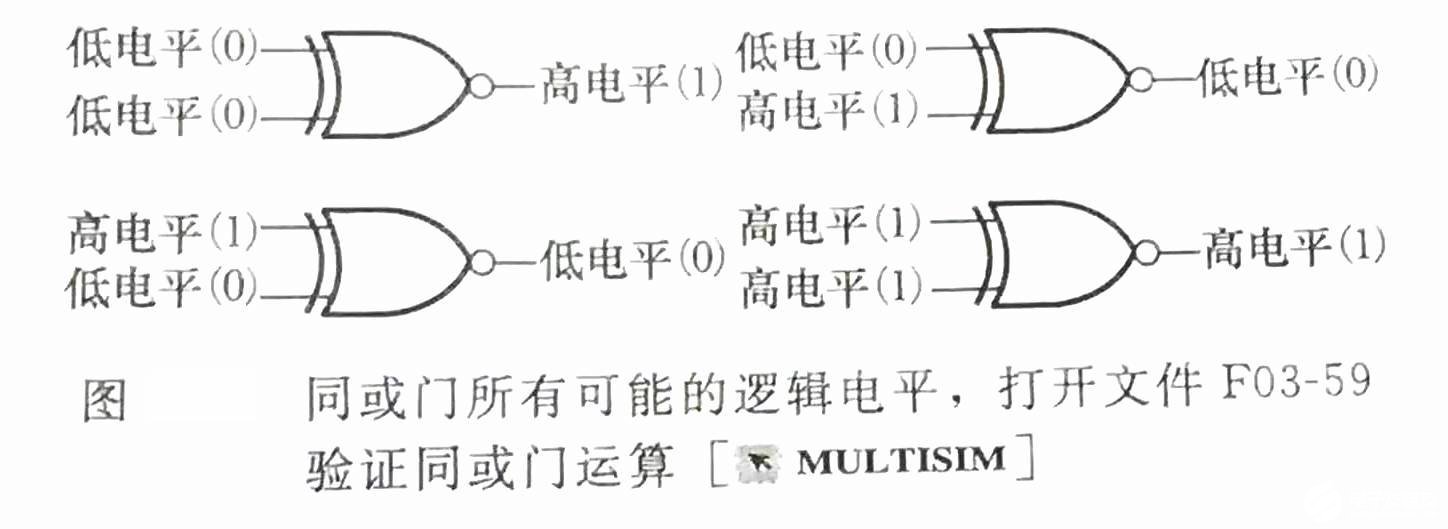

对于同或门而言,当输入A为低电平,输入B为高电平,或者输入A为高电平,输入B为低电平时,输出为低电平;当输入A和B同为低电平或者同为高电平时,输出为高电平。

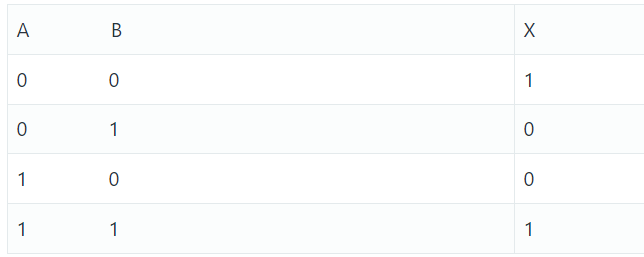

图中给出了同或门四个可能输入组合及其对应的输出结果。表中总结了同或门的运算。注意同或门的输入电平相同时,输出才为高电平。

异或门的布尔表达式为:X=A+B

同或门的逻辑表达式为: X=(A+B)’

异或和同或的逻辑表达式也可以用与,或及反相运算表示:

对于异或门有:X=AB’+A’B

对于同或门有:X=(AB)’+AB

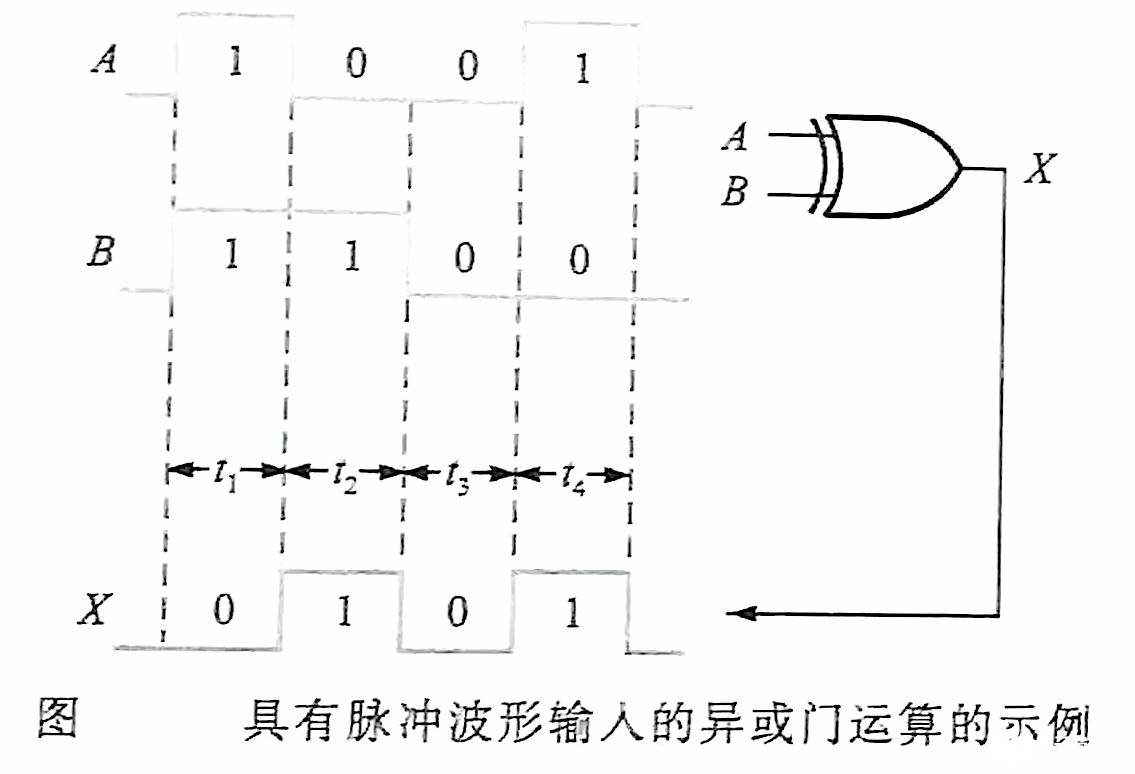

正如对其他门所做的一样,观察具有脉冲波形输入的异或门和同或门运算,跟以前一样,我们在脉冲波形输入的每个不同的时间间隔上应用真值表,图中给出了异或门的情况,可以看到在时间段t2和t4上,输入A与B是不同的电平,因此,在这个时间间隔上,输出为高电平。在t1和t3上,输入A和B为相同的电平,故输出为低电平。

异或门还可以做2位模2加法器。回忆之前所学的进制基本运算规则如下: 0+0=0,0+1=1,1+0=1和1+1=10。仔细观察异或门的真值表,可以发现异或门的输出是两个输入位的二进制和,如果输入都为1,则输出为0,舍弃进位1。后面将会学习异或门是如何组合起来形成复杂的加法电路。

审核编辑:黄飞

-

加法器

+关注

关注

6文章

183浏览量

31236 -

异或门

+关注

关注

1文章

42浏览量

18245 -

逻辑门电路

+关注

关注

2文章

68浏览量

12442 -

脉冲波形

+关注

关注

0文章

25浏览量

10088

发布评论请先 登录

同或门标准逻辑符号

同或门标准逻辑符号

评论