来源:《半导体芯科技》杂志

VistaX Pro LayerScan是Comet Yxlon开发的计算机层析技术,是先进封装领域最有效的检测方法。

就在不久前,半导体行业还认为X射线技术准确度太差、速度过慢、成本太高,而现在,微型计算机断层扫描(micro-CT)、精密轨迹和智能算法领域的新发展正在提供一种无损检测方法,可以帮助制造商实现其零缺陷战略,从而将他们的生产率和盈利能力提升到一个新的水平。

早在2005年,摩尔在一次纪念“摩尔定律”诞生40周年的访谈中就指出,这种集成电路微缩化很快就会达到其极限,很可能在21世纪20年代中期的某个时候变得根本不可行,或者实在是过于昂贵让人望而却步:“......材料是由原子构成的这一事实是最根本的限制,而我们距离这个限制已经不远了......我们正在触及一些非常基本的极限,所以总有一天,我们将不得不停下集成电路微缩化的脚步。”而另一方面,虽然时光已经进入了21世纪20年代,不过我们仍未走到摩尔定律的尽头。

目前,先进封装技术在电子结构方面早已进入纳米级范围。人类头发的平均直径为0.06毫米,即60,000纳米,相比之下,微芯片的尺寸仅为几平方毫米,其内部晶体管的作用就像微型电气开关一样,可以接通和关断电源。如今,每颗芯片所内含的晶体管数量都达到数十亿之多!

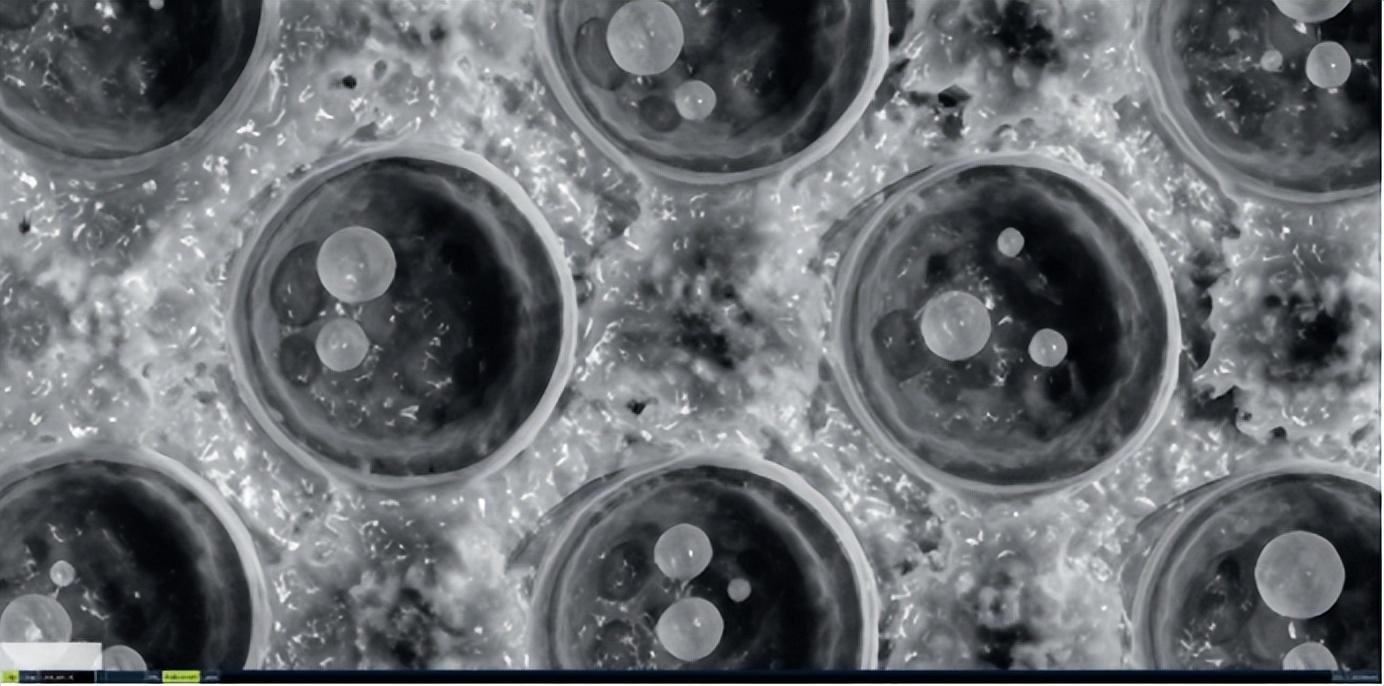

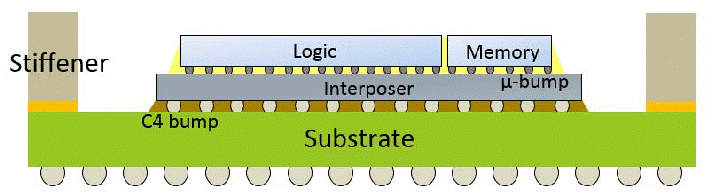

各个封装内部数量越来越多的芯片通过庞大的金属印制线网络连接起来。在经过微调的电路里,更多的子组件通过数千个直径为5~100μm的焊点进行桥接。这些焊点(焊球、C4或微凸块)以及TSV(硅通孔)对产品质量构成风险,通常是由生产工艺变化引起的。

△图1:60μm微凸块的3D视图(已焊接,未封)。

对当今的集成电路来说,其结构越紧凑、功能越强大、生产越复杂,其(从一个生产步骤到下一个生产步骤的)价值也就越高。对于制造厂家来说,所有必需分类清理的有缺陷的微芯片都意味着高额的经济损失。试想一下,由于在早期阶段没有发现工艺错误,导致一系列封装完毕的集成电路无法使用,将会造成多大的经济损失!半导体行业的制造商需要以严格控制公差的零缺陷生产为目标。因此,可靠的质量检查在研发阶段就已经开始了,并且伴随着整个制造过程,以降低非质量生产流程的成本。

破坏性测试方法,无论多么精确和详细,都已不再是解决方案,因为这需要承受较长的周转时间和较高的成本。在可能的检测技术中,光学检测只能检测出一小部分关键缺陷。在半导体领域,X射线技术作为一种检测方法极少受到关注。虽然它是唯一能够观察产品内部的技术,但是简单的荧光透视无法分辨当今复杂的三维封装中的重叠层。三维计算机断层扫描(computed tomography, CT)可以对物体的空间视图进行成像,但长期以来一直被认为速度太慢、成本太高。

三维计算机层析成像(computed laminography, CL)如今改变了游戏规则。与CT不同,CL不要求测试部件360°旋转。通过一种特殊的方式,对组件进行逐层扫描,以达到检测关键互连所需的分辨率和图像质量。可以对各层实施单独分析,也可将其重建为三维体。反过来,可以在任何感兴趣的区域对三维体进行切割,并进行详细检查。在此过程中,计算机层析成像比FIB-SEM(聚焦离子束扫描电子显微镜)等技术的速度要快得多,而且足够详细,能够检测到所有关键缺陷。当今的CT/CL检测系统能够确保一致的图像质量和稳定、可重复的结果,即使在批量检测过程中经过数小时的操作之后也是如此。

△图2:焊点的典型缺陷。

此外,通过应用自动化检测流程和自动缺陷识别(ADR)技术,在半导体行业中,X射线检测变得更加高效。Comet Yxlon的高分辨率微聚焦X射线系统具有同类最佳的成像水平和最新的软件功能,结合Dragonfly用于自动分割和图像评估的精细深度学习模型,可以根据用户的个性化需求量身定制,并且不受人为偏倚的影响。加快了投产进程,从而显著缩短了产品上市时间。

但是等等,X射线不会损坏、甚至毁坏敏感产品吗?如果采用创新的Comet Yxlon检测系统,上述情况就不复存在了。用于敏感组件的低剂量检测器模式,具报警和停止功能的剂量监测,以及额外的剂量减低套件,可以防止可能的辐射损伤,并保证X射线检查的安全性。除了经过验证的Cheetah EVO、Cougar EVO和FF20 CT微聚焦系统外,Comet Yxlon还提供了作为SEMI版本的FF35 CT,该X射线系统符合SEMI®的严苛标准(包括SEMI®S2-0818和SEMI®S8-0218危险和安全标准),并通过了相应的认证。而且,相关的开发继续全速推进。

△图3:焊接凸点中空洞的3D视图。

审核编辑 黄宇

-

芯片

+关注

关注

447文章

47838浏览量

409406 -

检测

+关注

关注

5文章

4087浏览量

90755 -

X射线

+关注

关注

4文章

190浏览量

50726 -

先进封装

+关注

关注

0文章

271浏览量

90

发布评论请先 登录

相关推荐

HRP晶圆级先进封装替代传统封装技术研究(HRP晶圆级先进封装芯片)

什么是先进封装?先进封装技术包括哪些技术

什么是先进封装?先进封装和传统封装区别 先进封装工艺流程

一文解析Chiplet中的先进封装技术

盘点先进封装基本术语

算力时代,进击的先进封装

先进封装Chiplet的优缺点与应用场景

先进封装之芯片热压键合技术

用于先进封装检测的先进X射线技术

用于先进封装检测的先进X射线技术

评论