为什么晶振下方不能走信号线?

晶振作为数字电路中常见的一个元件,用于产生稳定的时钟信号,是整个电路的重要组成部分。在设计电路布局时,有一个重要的原则是尽量避免信号线靠近晶振,尤其是在晶振下方布线。下面,我将详细解释为什么晶振下方不能走信号线。

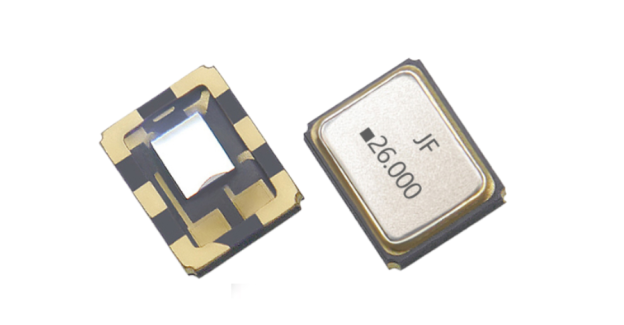

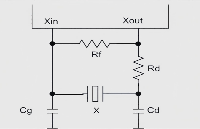

首先,我们需要了解晶振的工作原理和特性。晶振是通过电子振荡产生稳定频率的元件,其内部结构通常由谐振器、放大器和输出缓冲驱动器组成。当电源施加在晶振上时,谐振器产生共振,输出的振荡信号通过放大器进行放大,然后由输出缓冲驱动器提供给其他电路使用。

晶振的工作过程中会产生较大的干扰电压和电流。这些干扰源主要有两个方面:一个是晶体谐振器对外界的干扰,即晶体谐振器与外界环境的电磁波相互干扰;另一个是晶振自身对电路的干扰,即晶振产生的振荡信号对电路其他部分的电压和电流造成干扰。

首先,晶振的谐振器与外界环境的干扰是一个主要问题。晶体谐振器具有较高的灵敏度,其频率特性与外界环境的电磁波存在较强的耦合关系。如果布线在晶振下方,尤其是在晶体谐振器的位置上,信号线和谐振器之间存在较近的物理距离,会导致信号线上的电磁波对谐振器产生较大的干扰。这些干扰会引起晶体谐振器的频率偏移或失调,导致时钟信号的稳定性下降,进而影响整个电路的工作。

其次,晶振本身也会对电路其他部分造成干扰。晶振作为集成电路中的振荡源,其产生的振荡信号会在电路中传播并通过信号线传递给其他电路。如果信号线与晶振的物理距离较近,振荡信号会通过信号线的电场和磁场与信号线上的电压和电流相互耦合,从而引起信号线上的干扰。这些干扰信号会对其他电路产生抗干扰能力较弱的影响,导致电路的性能下降,甚至引起电路的误操作。

此外,晶振下方布线还可能引发信号反射问题。当信号线较长或者线路中存在电阻或电容等元件时,信号在传输中会存在反射现象。而晶振下方布线会导致信号线与晶振之间存在较近的物理距离,信号反射对振荡信号的稳定性产生负面影响。信号反射会导致信号的失真和延迟,进而引起电路的时序问题,严重时可能导致电路的不可预测性。

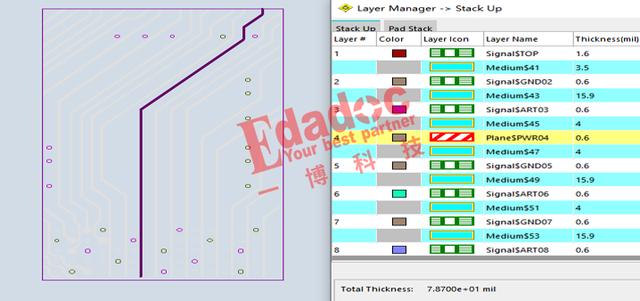

因此,为了保证电路的性能和稳定性,我们需要遵守尽量避免信号线靠近晶振的布线原则。在实际布线中,我们可以将信号线远离晶振,尽量保持足够的距离,以减少晶振及信号线之间的相互干扰。在布线过程中,我们还可以采取一些措施来进一步降低干扰的影响,比如采用屏蔽罩保护晶振等。

综上所述,晶振下方不能走信号线是为了避免晶振与信号线之间的相互干扰。这主要包括晶体谐振器受外界环境干扰导致时钟信号稳定性下降以及晶振本身对其他电路的干扰引起整个电路的性能下降。在电路设计中,合理布线是确保电路可靠工作的重要环节,遵循这一原则对电路的稳定性和性能具有重要意义。

-

晶振

+关注

关注

35文章

3442浏览量

72638 -

时钟信号

+关注

关注

4文章

495浏览量

29695

发布评论请先 登录

高扇出信号线优化技巧(下)

高扇出信号线优化技巧(上)

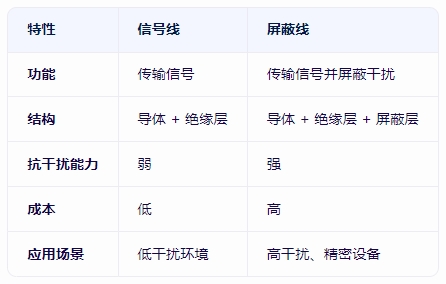

信号线和屏蔽线有什么区别

信号线和光纤线的区别是什么

高速信号线走线规则有哪些

高速信号走线越短越好吗为什么

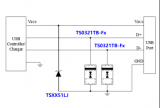

晶扬电子高速信号线专用浪涌保护器件TS0321TB-Fx解析

为什么晶振下方不能走信号线?

为什么晶振下方不能走信号线?

评论