晶振下方不能走信号线的主要原因是为了防止信号的干扰和保证晶振的稳定性。晶振是一种基于晶体振荡的元件,它的性能对于整个系统的稳定性和时序非常关键。以下是一些防止在晶振下方走信号线的主要原因:

电磁干扰(EMI): 晶振产生的振荡信号很弱,容易受到外部电磁干扰的影响。如果在晶振下方走信号线,信号线可能会作为天线,引入额外的电磁噪声,影响晶振的性能。

信号完整性: 晶振信号是一个非常精确的时钟信号,对于整个系统的时序要求非常高。如果在晶振下方走信号线,可能会导致信号的失真、时钟抖动等问题,从而影响系统的稳定性和性能。

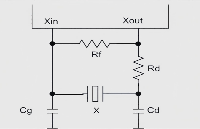

互电容和互感: 在信号线之间存在互电容和互感,如果在晶振下方走信号线,可能会引入不同信号线之间的电容和电感效应,从而影响信号的传输和时序。

电气性能: 晶振通常要求非常稳定的电气环境,以确保其振荡频率的准确性。信号线的存在可能引入不稳定性,从而影响晶振的性能。

为了最大程度地确保晶振的性能和系统的稳定性,通常建议将晶振周围的区域保持清晰,不要设计信号线穿越晶振的底部。这可以通过合理的布局规划和地线设计来实现,确保晶振周围的电磁环境尽可能干净,有助于提高系统的可靠性和性能。

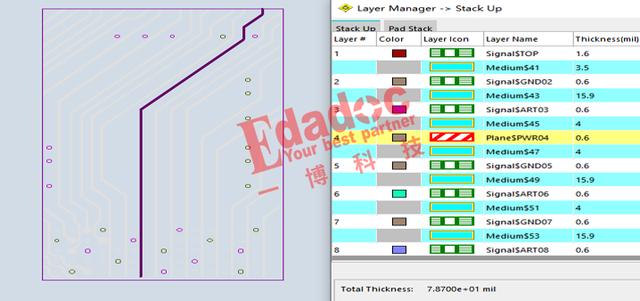

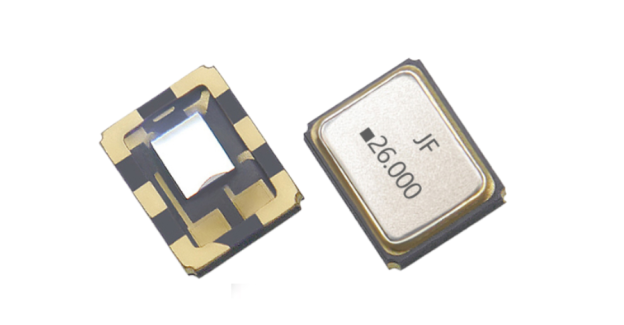

由于晶振为干扰源,本体下方所有层原则上不准许走线,特别是关键信号线,要保证晶振周围的没有其他元件,防止器件之间的互相干扰,影响时钟和其他信号的质量。若滤波器器件放在晶振下方,且滤波电容与匹配电阻未按照信号流向排布,会使滤波器的滤波效果变差。

-

晶振

+关注

关注

35文章

3442浏览量

72660 -

晶体振荡器

+关注

关注

9文章

733浏览量

32847 -

信号线

+关注

关注

2文章

185浏览量

22160 -

晶体振荡

+关注

关注

1文章

13浏览量

10241

发布评论请先 登录

高扇出信号线优化技巧(下)

高扇出信号线优化技巧(上)

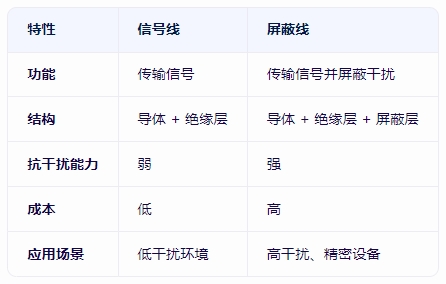

信号线和屏蔽线有什么区别

信号线和光纤线的区别是什么

高速信号线走线规则有哪些

高速信号走线越短越好吗为什么

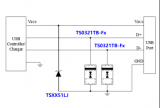

晶扬电子高速信号线专用浪涌保护器件TS0321TB-Fx解析

为什么晶振下方不能走信号线?

为什么晶振下方不能走信号线?

评论