一、分频

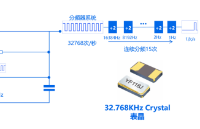

分频的过程涉及到将一个高频信号转换成频率更低的信号。例如,如果原始信号的频率是F,经过2分频后,新信号的频率将是F/2。在这个过程中,原始信号每经过两个周期,新信号才跳变一次,因此新信号的周期是原信号周期的两倍。分频常用于需要降低时钟频率的电路中,如在某些数字电路设计中生成不同频率的时钟信号。

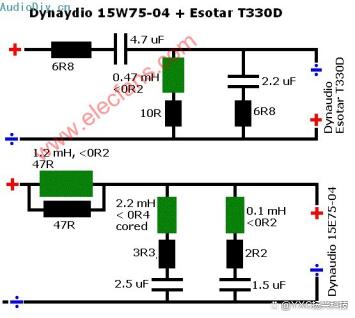

在RC电路中,电阻和电容的值可以决定一个振荡器的频率。通过改变电阻或电容的值,可以将振荡器的频率分成不同的频率。而在数字分频器中,输入信号被分成不同的频率分量,然后通过数字逻辑电路进行分频处理。

二、倍频

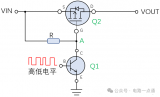

倍频则是将信号的频率增加至原来的N倍。这意味着,如果原始信号频率为F,那么经过2倍频后,新信号的频率将是2F。在实际应用中,倍频器可以用于无线通信系统,以产生更高频率的信号进行传输。

在LC振荡器中,电感和电容的值可以决定一个振荡器的频率。通过改变电感或电容的值,可以将振荡器的频率乘以不同的倍数。而在数字倍频器中,输入信号被分成不同的频率分量,然后通过数字逻辑电路进行倍频处理。

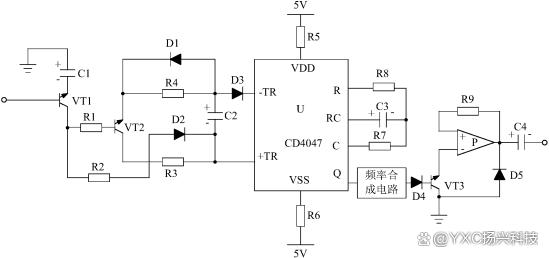

三、锁相环PLL电路

锁相环(PLL)电路是一种反馈控制系统,它利用外部输入的参考信号来控制内部振荡信号的频率和相位。

锁相环(PLL)电路存在于各种高频应用中,从简单的时钟净化电路到用于高性能无线电通信链路的本振(LO),以及矢量网络分析仪(VNA)中的超快开关频率合成器。

锁相环是一种反馈系统,其中电压控制振荡器和相位比较器相互连接,使得振荡器频率(相位)可以准确跟踪施加的频率或相位调制信号的频率。锁相环可用来从固定的低频信号生成稳定的输出频率信号。

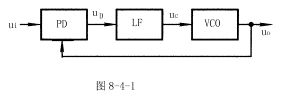

锁相环通常由鉴相器(PD,Phase Detector)、环路滤波器(LF,Loop Filter)和压控振荡器(VCO,Voltage Controlled Oscillator)三部分组成,锁相环组成的原理框图如图8-4-1所示。

-

锁相环

+关注

关注

36文章

633浏览量

90819 -

鉴相器

+关注

关注

1文章

62浏览量

23803 -

环路滤波器

+关注

关注

3文章

38浏览量

13407 -

PLL电路

+关注

关注

0文章

94浏览量

7023 -

反馈控制系统

+关注

关注

0文章

12浏览量

2707

发布评论请先 登录

CDC5801A低抖动时钟倍频/分频器技术文档总结

IGBT驱动与保护电路设计及 应用电路实例

无线应用射频微波电路设计

Analog Devices Inc. ADF4382x小数N分频锁相环 (PLL)数据手册

集成整数 N 分频 PLL 和 VCO 的 350-5000 MHz 宽带接收混频器 skyworksinc

AG32 MCU中CPLD使用基础(一)

STM32F407VGT6使用PLL倍频后芯片会反复重启怎么解决?

数字电路设计中:前端与后端的差异解析

噪声在RF电路设计中会带来哪些影响

32.768Khz在电路中的作用

分频、倍频与PLL电路在电路设计中的应用

分频、倍频与PLL电路在电路设计中的应用

评论