PCI Express (PCIe) 是一种高性能通用 I/O 互连协议,广泛用于各种计算产品和通信产品。由于时延低、带宽明显要更高,因此业界正在融合到 PCIe,作为高速串行总线标准。PCIe在NVM Express SSD应用中尤其流行。

PCIe 既有串行通信接口,又有存储接口,这 一点与 SAS 和 SATA 不同,因此实现了额外的行业扩充能力。PCIe 在跟复合 (系统/主机) 与端点 (插件) 之间基于点到点总线拓扑,支持全双工通信。这些规范是由 PCI-SIG 开发和维护的,这是一家由 900 多家公司组成的协会。

PCIe 物理层包括

差分低压100MHz基准时钟

可以扩充通路宽度:x1, x2, x4, x8, x12, x16, x32

可以扩充速度:2.5GT/s(Gen1), 5GT/s(Gen2), 8GT/s(Gen3), 16GT/s (Gen4)

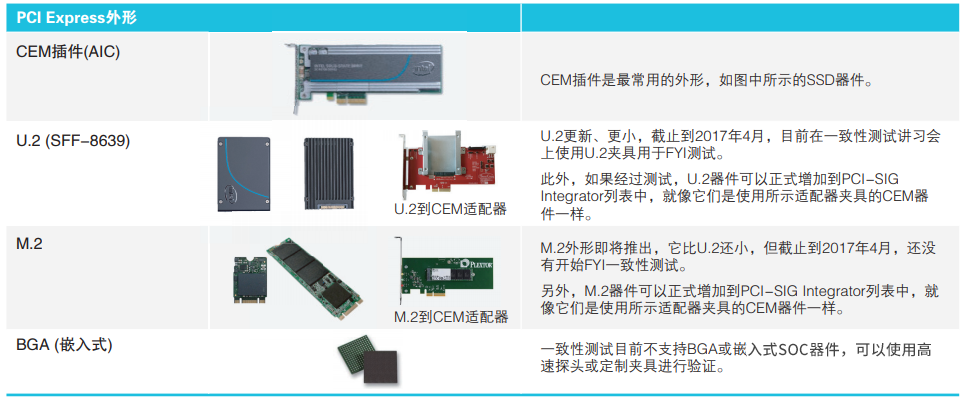

在一致性测试中使用不同的连接器,如CEM、U.2(SFF-8639)、M.2或直接焊接到PCB

ChrentPCI Express 它用在哪里?

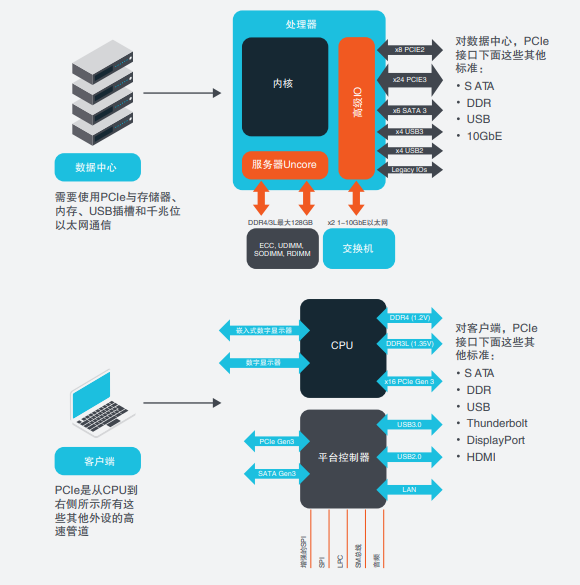

PCIe 是数据中心和客户端应用中使用的主要的新兴高性能存储和串行总线。PCIe 在外设之间实现了数据通信。

数据中心应用和客户端应用都有一个核心处理器, 为主机系统上的架构提供原始处理能力。这两种应用还必须接口各种外设器件,如 SATA 驱动器、 USB 设备等。在跟复合主机与端点器件之间,通常有许多路长损耗通道和连接器,带来了噪声、串扰、 定时不规则特点和其他损伤。因此,客户端和数据中心侧的 PCIe 器件必须能够可靠地演示 PCI 规定的一致性,补偿损伤,与 PCIe 器件互操作。

ChrentPCIe Gen4 最新进展

由于业界需要提高数据吞吐量和带宽吞吐量,因此 PCIe 数据速率必须提高,以跟上需求发展步伐。所以 Gen4 中最大的变化之一,是数据速率提高了 2 倍,从 Gen3 的 8GT/s 提高到 Gen4 的 16GT/s。

下面列明了最新Gen4标准的主要增强功能

16GT/s, 使用加扰 , 与 8GT/s 相同 , 编码与Gen3相比无变化 (128b/130b)

对加压的Rx眼图参数,RJ (随机性抖动) 从3ps (PCIe3)下降到~1ps (PCIe4)

Gen4连接器向下兼容Gen1/2/3

与行为Rx EQ数据速率有关

限定通道:对更长的通道和/或第二个连接器,要求使用中继器 (再驱动器和再定时器)

测试通道大约长12”,总损耗-28dB

在同一个器件上同时测试Gen3和Gen4时,被测试的各个预置值数量将翻一倍, 总 计22个。Gen3 有11个预置值(P0~P10),Gen4有11个预置值 (P0~P10)

新的SRIS独立RefClk模式-SRNS-单独的独立RefClk, 没有SSC结构-SRIS-单独的独立RefClk,采用SSC结构

新的Rx通路裕量功能测量通道最后的眼高 (EH)/ 眼宽 (EW) 裕量

Gen4的最小眼高已经下降到15mVpp

Gen4 CEM规范发布了rev 0.5

ChrentPCIe Refclk 结构

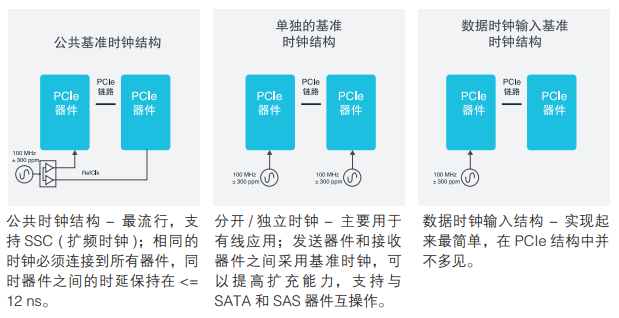

为了方便发射器件和接收器件可靠地传输数据,PCI-SIG 对基准时钟提出了非常严格的要求。标准规定使用 100 MHz 时钟 (Refclk),发 射器件和接收器件上的频率稳定性大于 ±300 ppm,并支持三种不同的时钟结构,同时协调根复合芯片和端点芯片。

在传统上,PCIe 一直采用公共时钟结构,跟复合和芯片可以偏离相同的时钟配置,而不是以不同的间隔运行,后者测试起来更具有挑战性。公共时钟是 一种更加精确的结构,但整合到系统中的灵活性较差。通过采用 Gen4 标准,系统可望更多地采用分开 / 独立的时钟结构。时钟稳定性必不可少,以支持三种不同的时钟输入结构。

ChrentPCI Express 外形

为了方便发射器件和接收器件可靠地传输数据,PCI-SIG 对基准时钟提出了非常严格的要求。标准规定使用 100 MHz 时钟 (Refclk),发射器件和接收器件上的频率稳定性大于 ±300 ppm,并支持三种不同的时钟结构,同时协调根复合芯片和端点芯片。

Chrent一致性测试预置值

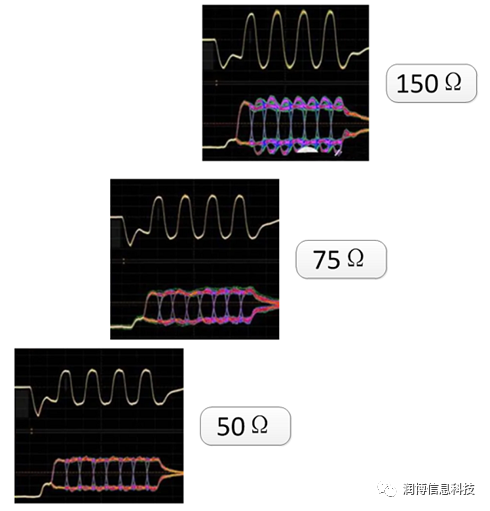

为通过一致性测试,实现互操作,每台器件都要求进行 PCI-SIG 认证,它基于一个预置值或发射机均衡设置列表,从每秒 2.5 Gb/s 的低 数据速率直到最新的 16 Gb/s 的高数据速率。这些预置值用来均衡通道损耗,优化链路上的信号完整性。每个预置值都是主机应用到端 点的下冲和去加重的具体组合。

下表详细列出了 Gen3 和 Gen4 的 11 种预置值。DUT 必须支持所有预置值。为降低测试时间,提高自动化速度,建议使用 100MHz 时钟突发,作为一致性测试夹具的输入,在这些预置值之间快速切换。如果您可以使用 100MHz 脉冲拨码开关自动执行预置测试,那么您可以节约宝贵的测试时间,因为您可以自动采集和分析各个指标,如抖动、电压和定时。

下面预置值同时适用发射机测试和接收机测试。

Chrent发射机 (Tx) 测试基础知识

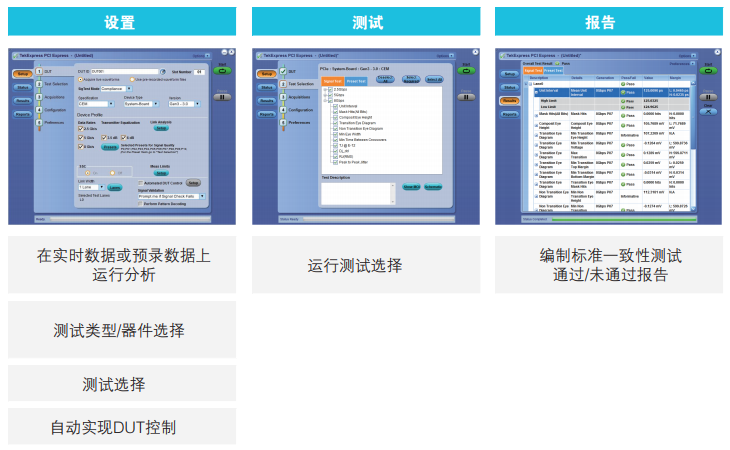

下面列明了对 PCIe 发射机自动进行一致性测试的各个步骤。自动软件至关重要,因为它可以使用 100 MHz 基准时钟自动切换预置测试模式,与手动按钮进行拨码切换相比,可以把测试时间缩短两倍。

许多 PCI-SIG 测试早期实现者更愿意使用泰克 DPOJET 和 SDLA 软件之类的工具,来完成早期 Gen4 表征和调试。

Chrent基本规范发射机 (Tx) 测试

在芯片器件的基本发射机测试中,直接规定了发射机引脚上的测量项目。由于有时不可能接入引脚,因此应在尽可能靠近这个基准点的位置执行测量。

在芯片级可通过多种方式完成这一测试

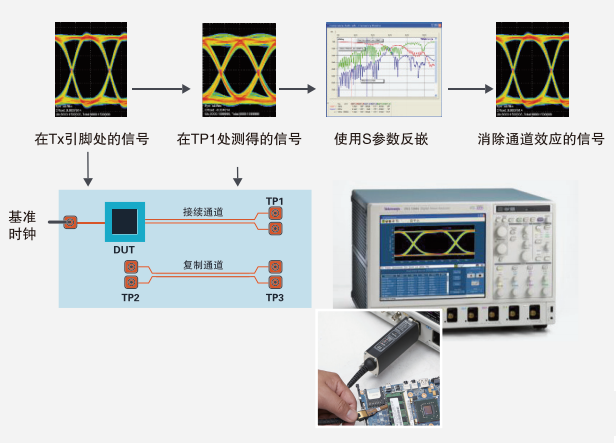

如果您深入了解类似的复制通道的S参数,那么可以反嵌接续通道的损耗。您可以看到发射机引脚上的信号是什么样的,而没有增加通道影响。

在示波器上使用均衡或CTLE,均衡消除通道损耗。

使用高带宽探头,探测位置应尽可能靠近发射机引脚 。

示波器可以使用 SDLA、Seasim 和 SigTest 之类 的软件工具,执行嵌入 / 反嵌、均衡和眼图分析。这种软件级分析允许设计人员在试产前优化和调试芯片性能,节约时间、资金及全面调试。确保采用的测量系统足够灵活,能够测试和调试被测器件的特定功能。

ChrentCEM 和 U.2 规范发射机 (Tx) 测试

在芯片器件的基本发射机测试中,直接规定了发射机引脚上的测量项目。由于有时不可能接入引脚,应在尽可能靠近此基准点的位置执行测量。

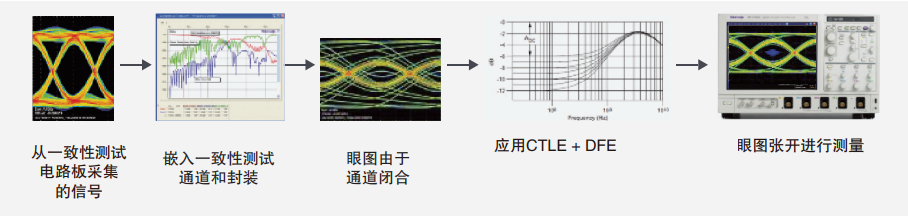

系统和插件在CEM级发射机测试中,会像接收机分片器看到的那样测量发射机的信号完整性,但由于外形及测试过程中使用的夹具,不可能直接接入信号。为保证测量精度,应实现下面介绍了两个重要组件。

1. 把一致性测试通道的性能特点向回嵌入到正在测量的信号中。这要求深入了解通道的插入损耗和S参数。由于这个原因,PCI-SIG为CEM测试提供了一致性测试夹具及已知的S参数。

2. 使用软件工具应用通道均衡,测量和分析通道末端张开的眼图。PCI-SIG提供了一个软件工具,称为SIG-Test,应用与PCI-SIG特性有关的行为均衡器,提供测试通过/未通过结果。定制示波器软件,如泰克DPOJET和SDLA,可以从闭上的眼图到张开的眼图,全面表征和调试均衡的信号。

Chrent接收机 (Rx) 测试基础知识

ChrentPCIe 测试和调试设置中的关键考虑因素

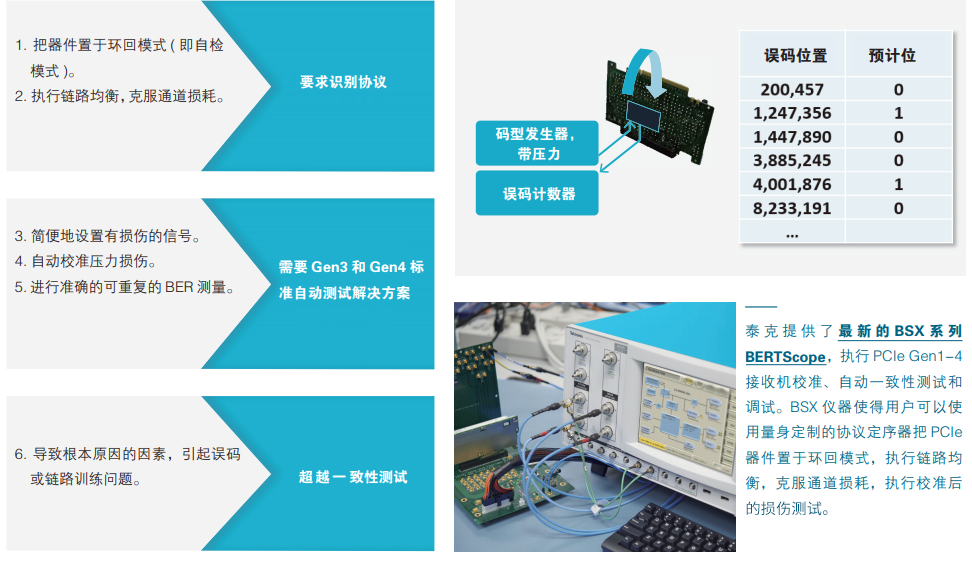

由于Gen 4标准的出现,PCIe的速度和复杂度正不断提高,工程师面临着新的设计挑战、更短的产品开发周期,同时需要了解新的标准规范及新的一致性测试要求。

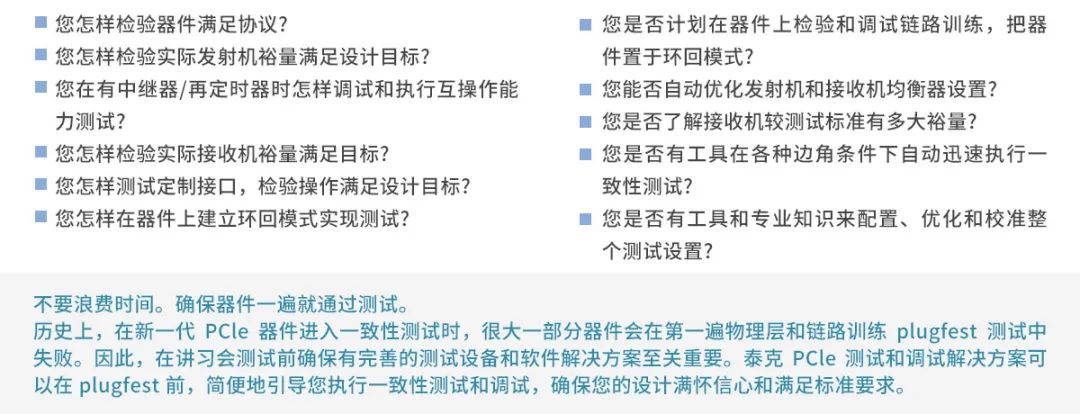

在您处理Gen3或Gen4 PCIe器件测试和调试前,要问以下几个关键问题:

-

测试

+关注

关注

9文章

6429浏览量

131691 -

PCIe

+关注

关注

16文章

1483浏览量

88946 -

串行通信接口

+关注

关注

0文章

19浏览量

9739

发布评论请先 登录

信号完整性与电源完整性的仿真分析与设计

高速串行信号的信号完整性和物理层测量与分析

PCIe物理层的基本概念

pcb信号完整性详解

ADP7000系列示波器特色功能:以太网物理层一致性测试,让网络物理层问题无所遁形

PCIe Tx/Rx 物理层信号完整性测试方法详解

PCIe Tx/Rx 物理层信号完整性测试方法详解

评论