计算公式

理论带宽 = 内存核心频率 * 内存总线位数 * 倍增系数

理论带宽 = 数据传输率 * 内存总线位数

引出:

核心频率:等价于芯片上的时钟针脚的频率,是DDR的工作频率

时钟频率:可通过倍频技术升级的核心频率。时钟频率可以理解为IO Buffer的实际工作频率,DDR2中时钟频率为核心频率的2倍,DDR3 DDR4中时钟频率为核心频率的4倍。

数据传输率:指数据被传输的频率,DDR是双沿传输,因此可以认为数据传输率是时钟频率的2倍,为核心频率乘以倍增系数(预期系数)。

近年来内存的频率虽然在成倍增长,可实际上真正存储单元的频率一直在133MHz-200MHz之间徘徊,这是因为电容的刷新频率受制于制造工艺而很难取得突破。

倍增系数

倍增系数可以认为是perfetch,也可以认为是数据传输率/核心频率

内存总线位数

内存总线位数 = Rank个数 * 一个Rank内的chip个数 * 每个chip内的IO位宽

预取 prefetch

在一个时钟周期内,同时将相邻列地址的数据一起取出来

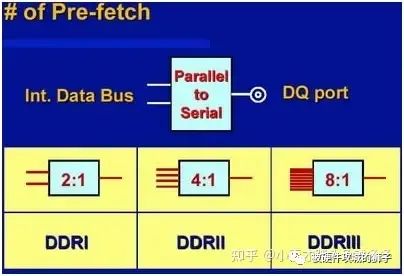

DDR的传输速度越来越快,由两部分协同实现。一是通过prefetch技术使得每次从存储颗粒中传输数据到IO Buffer的数据量变大(DDR:2 / DDR2:4 / DDR3:8 / DDR4:8 / DDR5:16);二是通过倍频和双沿触发来使得IO Buffer的传输能力达到提升。

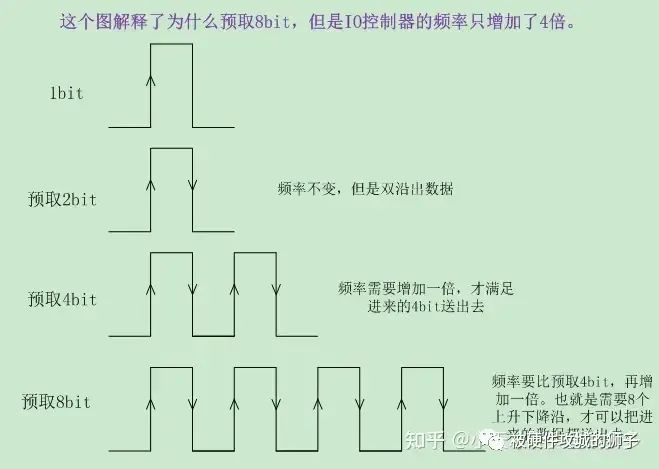

那么,内存IO频率为什么能达到数倍于核心频率呢?

相信很多人都知道,DDR1/2/3内存最关键的技术就是分别采用了2/4/8bit数据预取技术(Prefetch),由此得以将带宽翻倍,与此同时I/O控制器也必须做相应的改进。

● DDR1/2/3数据预取技术原理:

预取,顾名思义就是预先/提前存取数据,也就是说在I/O控制器发出请求之前,存储单元已经事先准备好了2/4/8bit数据。简单来说这就是把并行传输的数据转换为串行数据流,我们可以把它认为是存储单元内部的Raid/多通道技术,可以说是以电容矩阵为单位的。

内存数据预取技术示意图:并行转串行

这种存储阵列内部的实际位宽较大,但是数据输出位宽却比较小的设计,就是所谓的数据预取技术,它可以让内存的数据传输频率倍增。试想如果我们把一条细水管安装在粗水管之上,那么水流的喷射速度就会翻几倍。

明白了数据预取技术的原理之后,再来看看DDR1/2/3内存的定义,以及三种频率之间的关系,就豁然开朗了:

● SDRAM(Synchronous DRAM):同步动态随机存储器

之所以被称为“同步”,因为SDR内存的存储单元频率、I/O频率及数据传输率都是相同的,比如经典的PC133,三种频率都是133MHz。

SDR在一个时钟周期内只能读/写一次,只在时钟上升期读/写数据,当同时需要读取和写入时,就得等待其中一个动作完成之后才能继续进行下一个动作。

● DDR(Double Date Rate SDRAM):双倍速率同步动态随机存储器

双倍是指在一个时钟周期内传输两次数据,在时钟的上升期和下降期各传输一次数据(通过差分时钟技术实现),在存储阵列频率不变的情况下,数据传输率达到了SDR的两倍,此时就需要I/O从存储阵列中预取2bit数据,因此I/O的工作频率是存储阵列频率的两倍。

注:因为在出口处的流量增大了,所以入口的流量也要相应的增大。所以有了2bit预取技术。

DQ频率和I/O频率是相同的,因为DQ在时钟上升和下降研能传输两次数据,也是两倍于存储阵列的频率。

● DDR2(DDR 2 SDRAM):第二代双倍速率同步动态随机存储器

DDR2在DDR1的基础上,数据预取位数从2bit扩充至4bit,此时上下行同时传输数据(双倍)已经满足不了4bit预取的要求,因此I/O控制器频率必须加倍。

注:因为入口处的流量增大了,所以出口处也要相应的增大流量。增大出口处流量的方法就是增大IO控制器的频率。

至此,在存储单元频率保持133-200MHz不变的情况下,DDR2的实际频率达到了266-400MHz,而(等效)数据传输率达到了533-800MHz。

● DDR3(DDR 3 SDRAM):第三代双倍速率同步动态随机存储器

DDR3就更容易理解了,数据预取位数再次翻倍到8bit,同理I/O控制器频率也加倍。此时,在存储单元频率保持133-200MHz不变的情况下,DDR3的实际频率达到了533-800MHz,而(等效)数据传输率高达1066-1600MHz。

综上可以看出,DDR1/2/3的发展是围绕着数据预取而进行的,同时也给I/O控制器造成了不小的压力,虽然存储单元的工作频率保持不变,但I/O频率以级数增长,我们可以看到DDR3的I/O频率已逼近1GHz大关,此时I/O频率成为了新的瓶颈,如果继续推出DDR4(注意不是GDDR4,两者完全不是同一概念,后文会有详细解释)的话,将会受到很多未知因素的制约,必须等待更先进的工艺或者新解决方案的出现才有可能延续DDR的生命。

审核编辑:汤梓红

-

DDR3

+关注

关注

2文章

290浏览量

44277 -

带宽

+关注

关注

3文章

1050浏览量

43572 -

内存

+关注

关注

9文章

3234浏览量

76518 -

总线

+关注

关注

10文章

3060浏览量

91868

原文标题:DDR理论带宽计算

文章出处:【微信号:被硬件攻城的狮子,微信公众号:被硬件攻城的狮子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

【小知识分享】SDR/DDR1/DDR2/DDR3的接口区别

【小知识分享】SDR/DDR1/DDR2/DDR3的接口区别

DM8168,仅使用DDR0通道连接 4片8bit的ddr3,而DDR1通道不接ddr3,请问SD卡启动的时候需要有特殊配置吗?

请问如何理解C6678中对预取数据的描述?

SDRAM,DDR3,DDR2,DDR4,DDR1的区别对比及其特点分析

面向系统的程序基本块指令预取技术

基于DDR3内存的PCB仿真设计

DDR3价格飞涨 预上涨40%-50%

15V、双通道 3A 单片同步降压型稳压器为 DDR1、DDR2 或 DDR3 存储器供电

2048M位DDR1 SDRAM VD1D2G32xS86xx2T7B英文手册

DDR1/2/3数据预取技术原理详解

DDR1/2/3数据预取技术原理详解

评论