芯片简介

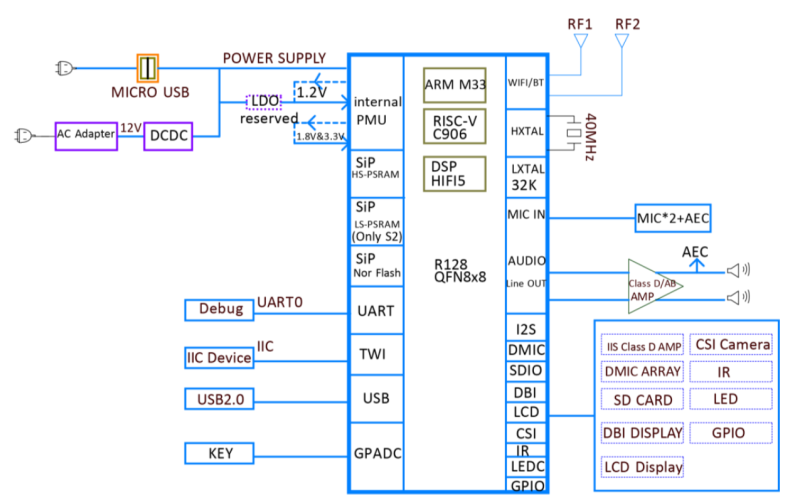

R128是一颗专为“音视频解码”而打造的全新高集成度 SoC,主要应用于智能物联和专用语音交互处理解决方案。

单片集成 MCU+RISCV+DSP+CODEC+WIFI/BT+PMU,提供生态配套成熟、完善的用于系统、应用和网络连接开发的高效算力;

集成 8MB/16MB/32MB PSRAM,为音视频解码、大容量存储、扫码以及网络连接提供充裕的高容量、高带宽的内存支持;

拥有丰富的音频接口 IIS/PCM、OWA、DMIC、LINEOUT、MICIN 以及通用通讯接口 IIC、UART、SDIO、 SPI、ISO7816卡接口;同时支持 U 盘、SD卡、IR-TX/RX;

内置 LDO、GPADC、LEDC,简化系统方案设计,降低 BOM成本。

芯片应用场景

芯片实物图

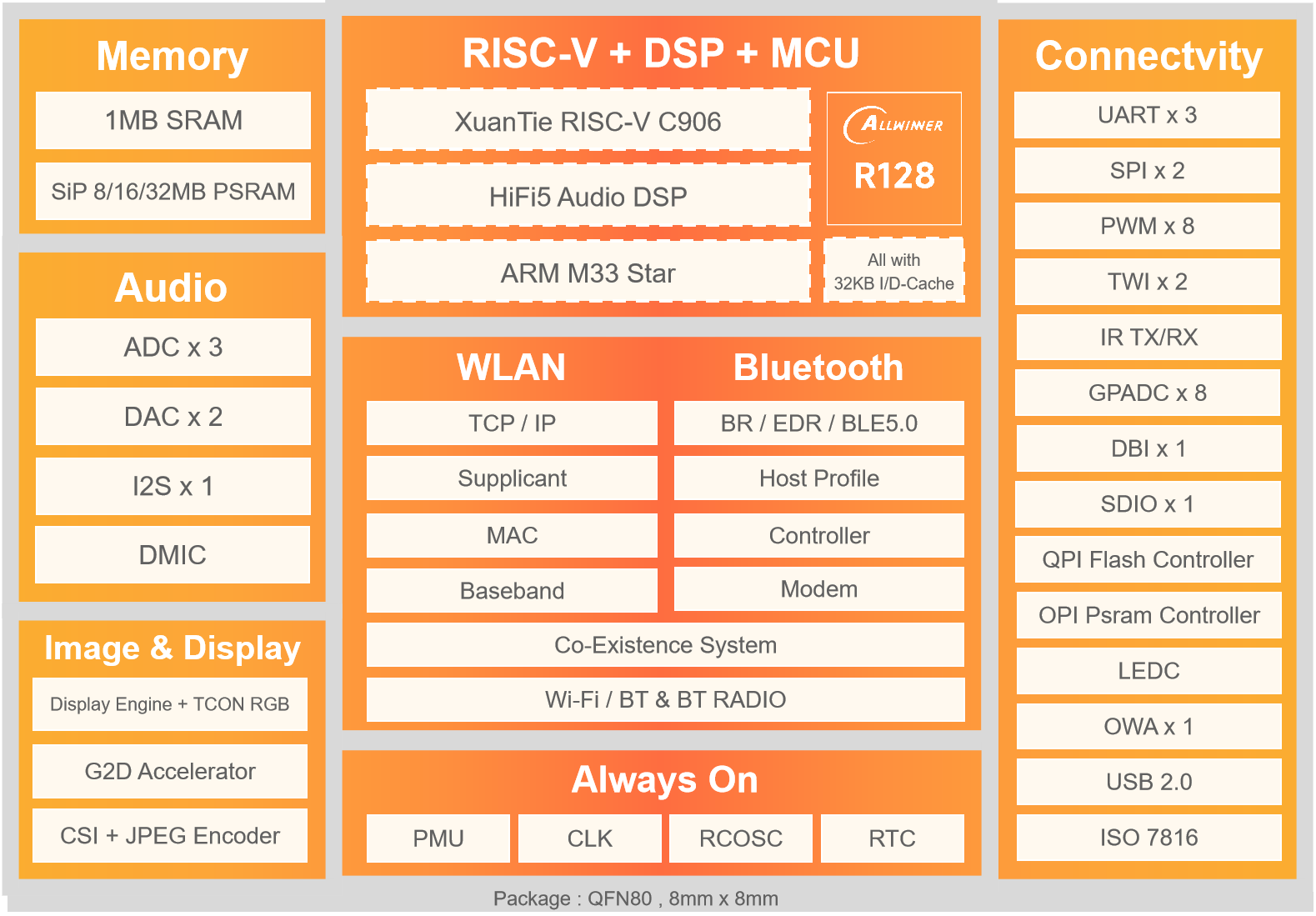

芯片框图

芯片特性简介

- XuanTie 64 bit RISC V C 906 CPU , up to 480 MHz - HiFi5 Audio DSP up to 400 MHz - Arm M33 Star MCU , up to 192 MHz - Memories - 1MB SRAM - SiP 8 MB/16 MB Flash - 8 MB H S PSRAM in R128 S 1 - 8 MB LS PSRAM & 8 MB HS PSRAM in R128 S2 - 32 MB HS PSRAM in R128 S3 - 2048 bit efuse - Image and Graphics - Supports Graphic 2D accelerator with rotate, mixer, and 4 layers - Supports RGB output interface, up to 1024 x 768 @60 fps - Supports display engine - Video Input - 8 bit parallel CSI interface - Supports both online and offline mode for JPEG encoder - Supports JPEG encoder, 1920 x 108 8 - Analog Audio Codec - 2 DAC channels 24 bit audio codec for R128 S1 and R128 S2 - 1 DAC channel 24 bit for R128 S3 - 3 ADC channels - Supports USB audio playback - Up to 119 dB SNR during DAC playback path (signal through DAC and lineout with A weighted filter) - Up to 98 dB SNR during ADC record path (signal through PGA and ADC with A weighted filter) - One I2S/TDM/PCM external inte rface (I2S0 - Security Engine - Symmetrical algorithm: AES, DES, 3DES - Hash algorithm: MD5, SHA1, SHA224, SHA256, SHA384, SHA512, HMAC - Asymmetrical algorithm: RSA512/1024/2048bit - S upports TRNG - External Peripherals - One USB 2.0 DRD - Up to 3 UART controllers (UART 0, UART1, UART2) - Up to 2 SPI controllers (SPI0, SPI1) - Up to 2 TWIs - One CIR RX and one CIR TX - Up to 8 PWM channels (PWM[ 7 0 - Up to 7 GPADC input channels (R128 S1 & R128 S2)/8 channels (R128 S3) - One LEDC used to control the external intelligent control LED lamp - Package - QFN80, 0.35 mm pitch, 8 mm x 8 mm body

不同版本芯片的区别

R128 共有R128-S1、R128-S2 和R128-S3 三个型号,各型号具体配置差异如下表:

| Contents | R128-S1 | R128-S2 | R128-S3 |

| CPU | M33 + C906 | M33 + C906 | M33 + C906 |

| DSP | HiFi5 | HiFi5 | HiFi5 |

| PSRAM | 8MB HS-PSRAM | 8MB HS-PSRAM + 8MB LS-PSRAM | 32MB HS-PSRAM |

| FLASH | 8MB | 16MB | / |

| DAC |

2 Audio DAC LINEOUTLP/N LINEOUTRP/N |

2 Audio DAC LINEOUTLP/N LINEOUTRP/N |

1 Audio DAC LINEOUTLP/N |

| GPADC Channels | 7 | 7 | 8 |

| Package | QFN80 8*8mm 0.35pitch | QFN80 8*8mm 0.35pitch | QFN80 8*8mm 0.35pitch |

请注意,R128-S1、R128-S2引脚封装是相同的,而 R128-S3 与R128-S1、R128-S2是不同的。具体请参照芯片参数章节

审核编辑:汤梓红

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

芯片

+关注

关注

463文章

54440浏览量

469405 -

mcu

+关注

关注

147文章

19134浏览量

404037 -

soc

+关注

关注

40文章

4626浏览量

230207 -

硬件开发

+关注

关注

3文章

194浏览量

25217

发布评论请先 登录

相关推荐

热点推荐

DshanMCU-R128s2-DEVKIT应用开发案例

本文章为DshanMCU-R128s2-DEVKIT应用开发案例,本文案例(点亮一颗 LED 灯)代码可以到全志在线-在线文档或者复制链接前往下载。

DshanMCU-R128s2芯片参数

MB LS PSRAM R128 S2)/8 channels (R128 S3) - One LEDC used to control the external intellige

DshanMCU-R128s2芯片手册与资料

: Xplorer Software (SDK) Download Xtensa Xplorer 授权申请: Cadence Tensilica Offerings Xtensa Xplorer 试用申请: request an evaluation license 其余手册将在R128

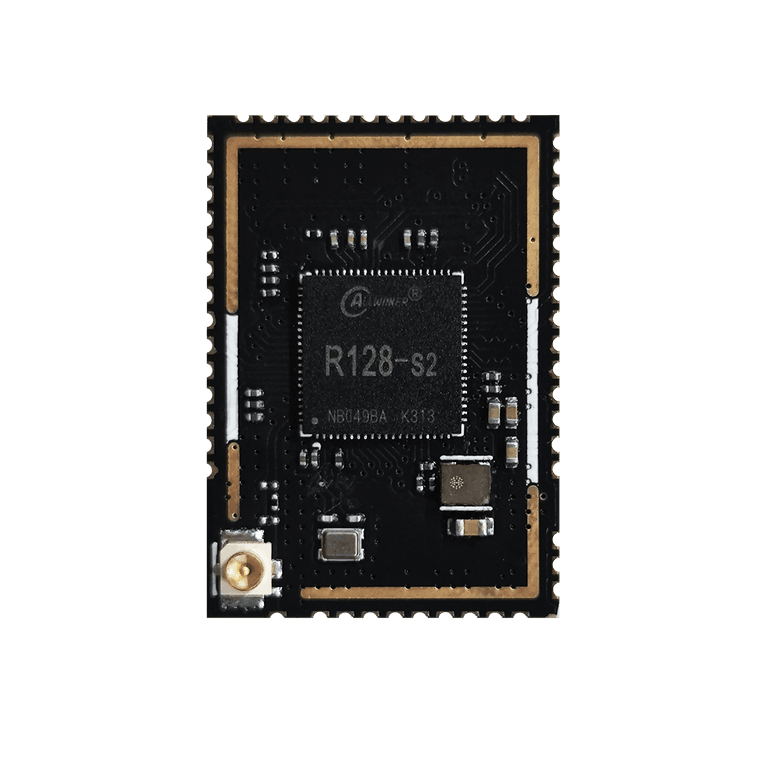

DshanMCU-R128s2 R128 模组

R128-S2-N16R16 R128-S2 Arm Cortex-M33 C906 RISC-V HIFI5 DSP 1MByte 8Mbyte 8Mbyte 16M NOR Flash 2 Audio

DshanMCU-R128s2 R128 DevKit 开发板

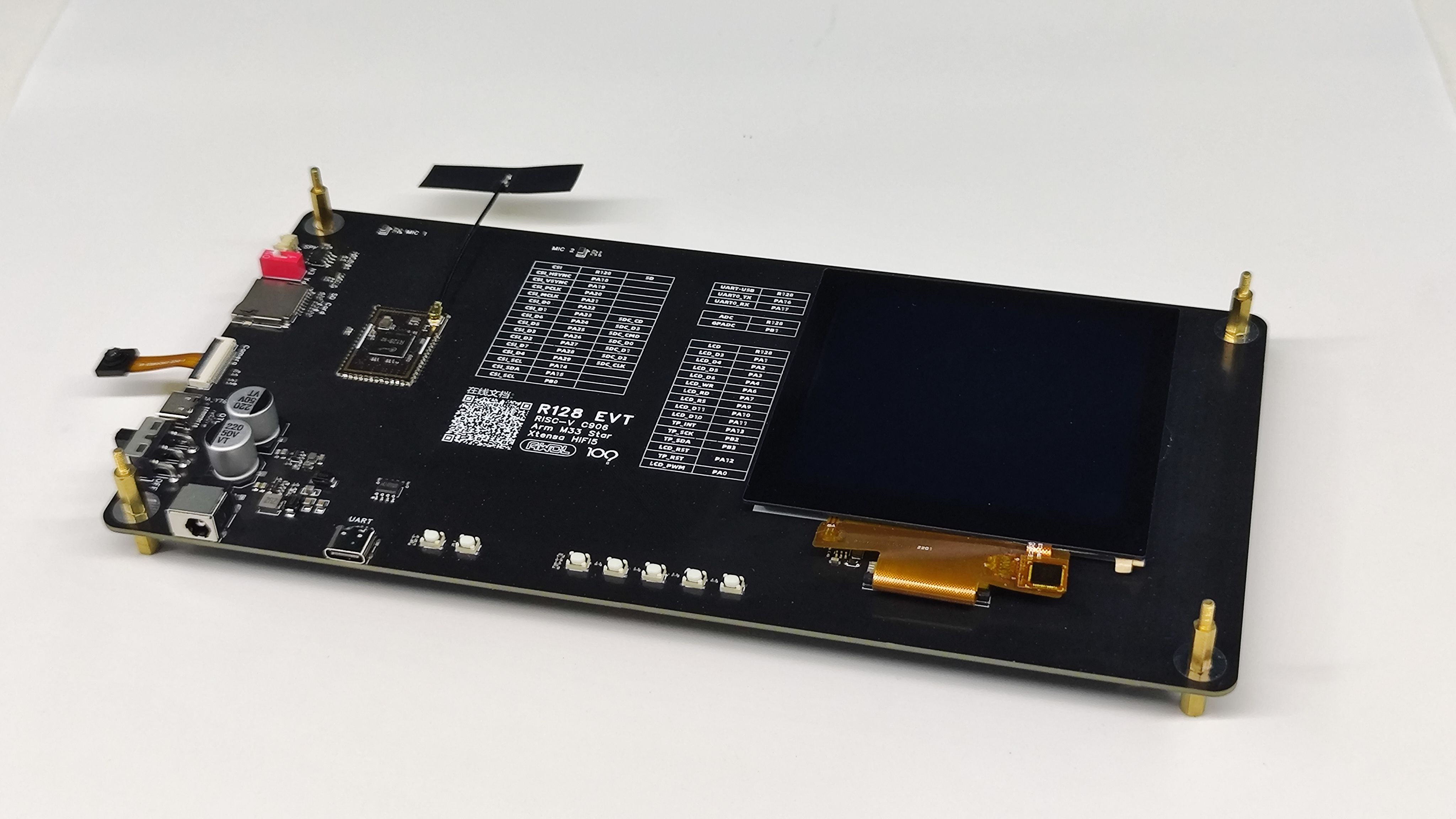

针对 R128 模组,百问科技推出了 R128 DevKit 开发板作为快速开发评估工具。 特性: 板载 R128-S2-N16R16 模组 板载 2.4G RF 陶瓷天线 板载 USB Type

DshanMCU-R128s2 SDK 架构与目录结构

R128 S2 是全志提供的一款 M33(ARM)+C906(RISCV-64)+HIFI5(Xtensa) 三核异构 SoC,同时芯片内部 SIP 有 1M SRAM、8M LSPSRAM、8M

DshanMCU-R128s2 Hello World!

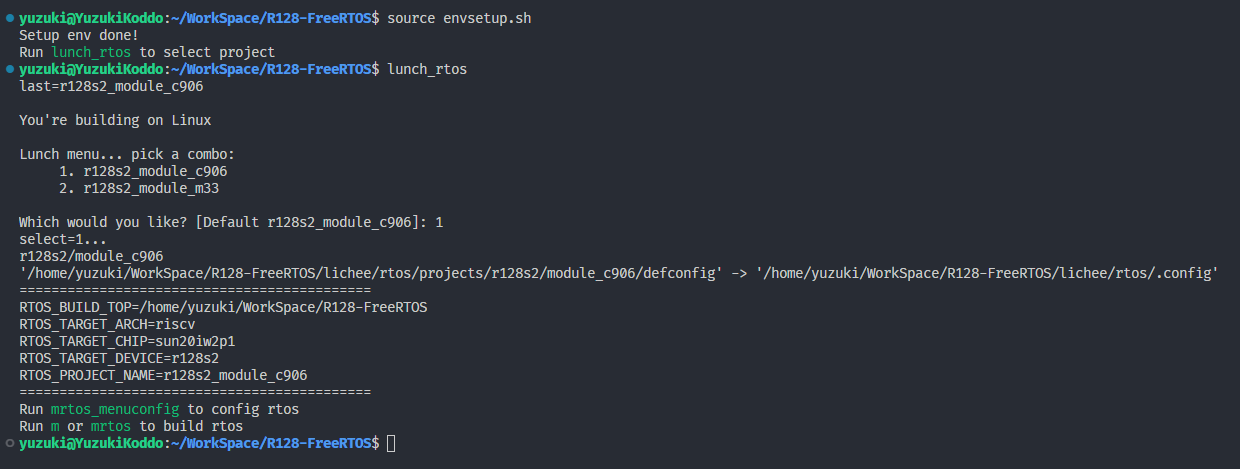

载入方案选择 r128s2_module_c906 $ source envsetup.sh $ lunch_rtos 1 编辑程序 打开你喜欢的编辑器,修改文件: lichee/rtos

DshanMCU-R128s2 配置引脚复用

解析 sys_config.fex 的驱动配置位于 licheertos-componentsawsys_config_script 中。 对于配置引脚复用,只需要修改 boardr128s2{PROJECT}configsys_config.fex 文件即可。 GPIO描述

DshanMCU-R128s2启动与资源划分

下面简单介绍一下 R128 方案的资源划分与启动流程。 资源划分 CPU 资源划分 这只是默认配置方案,CPU 资源划分可以按照需求任意修改 CPU 功能说明 M33 控制核。运行 WI-FI/BT

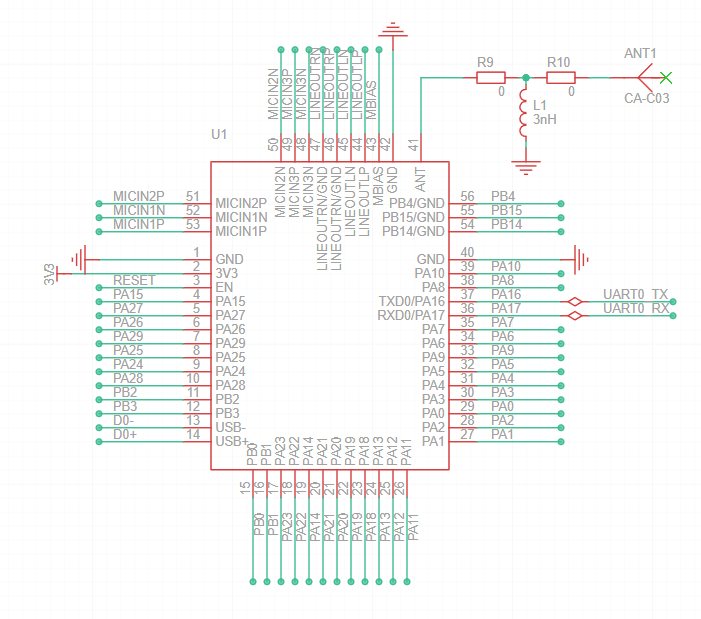

DshanMCU-R128s2硬件设计指南

原理图设计 硬件系统框图 R128是一颗专为“音视频解码”而打造的全新高集成度 SoC,主要应用于智能物联和专用语音交互处理解决方案。 单片集成 MCU+RISCV+DSP+CODEC+WIFI

DshanMCU-R128s2硬件设计参考

R128 DevKit 开发板 硬件工程开源地址:https://oshwhub.com/gloomyghost/r128-module 电路图

DshanMCU-R128s2术语表

M33+C906+HIFI5 处理器的 SoC 平台 AudioCodec 芯片内置音频接口 I2S/PCM 外置数字音频接口,常用于外接codec 模块。 AHUB 音频集线器,内部集成I2S 接口及DAM 混音器,可实现多

DshanMCU-R128s2芯片简介

DshanMCU-R128s2芯片简介

评论