ERC全称为electrical rule checking,翻译为电气规则检查。检测的是GDS版图中是否存在电学连接问题,属于PV(physical verification)的一个项目。这也算是一个后端signoff的基本概念,今天就给大家简单介绍一下ERC。

什么叫电气规则呢?其实它的种类也不多,主要包括:1. MOS的gate不能直接连supply。2. cell input永远不能floating。3. 一个cell的driver最多一个,或者说output不能发生short。 4. N/P区(衬底或阱)不能floating。可能还有别的,不过我目前只知道这四种了,可以先了解一下。我下面分别说一下这四条规则的理由。

对于1,我们在设计芯片的时候总是会按最悲观的情况考虑问题,因此我们会认为PG的供电总是不稳定的。人们的初衷可能都是简单的,希望一个mos常开或者常关,但如果直接将PG接到gate上,在电压出现波动的时候(比如说由于静电),这个mos的开关就不那么稳定,其沟道电阻相应会受到影响。甚至电压波动很大的时候会发生逻辑错误,或者击穿mos管。

因此实际应用的时候,对于那些输入一直为0或者一直为1的情况,我们会从PG接一个TIE cell,再接到gate上。TIE cell可以起到一个稳定电压、中继的作用。

Cell的input如果floating,那个pin就是会类似一根天线,它的电压很容易受旁边电路的影响,此时就不能认为它是一个完美的高电压或者低电压了,相对应的数字信号就没了意义。这里可能要联系一点模拟的知识,假设高电压是5V,低电压是0V,我们可能就认为4V以上就是逻辑1,1V以下就是逻辑0,所以input输入是什么其实完全是由它的电压决定的。

在floating的情况下,输入就不确定,逻辑可能受到影响。除此之外还可能影响power,比如一个CMOS反相器,input如果不确定,NMOS和PMOS就处于一种“半导通半不导通”的状态。

我们知道反向器的任何一个mos导通的时候另一个mos关断,漏电流就不会很大,而这种“半导通半不导通”就会产生很大的漏电流,甚至会烧坏管子。

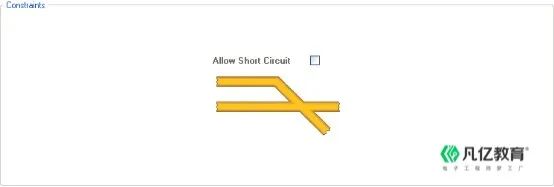

Multiple driver的情况,会导致电路VDD和VSS发生short。还是假设两个反相器,它们的output接在了一起,当第一个反相器输出逻辑1(高电平),第二个反相器输出逻辑0(低电平)的时候,相当于产生一条从VDD直接到VSS的电流通路。这是绝对不被允许的。

N/P floating,还是主要为了防止latch up。一般会将N well接VDD,P substrate接VSS,减小well/substrate和drain/source之间的电势差,可以防止latch up产生。

一般我们会把摆放cell的区域隔一段差一个tap cell,然后塞满filler cell,为的就是保证n/p区同一个row的cell公用,而且都能找到附近的tap cell。这一部分可以参考我之前写的一篇介绍latch up的文章。

除了ERC之外,现在还有PERC的概念,就是programmable ERC。指的是用户可以根据自己的design客制化编写一些ERC的rule来进行检查,一般都是会检查ESD相关的rule。

比如说PERC有current density检查,就是检查某一条专门用来ESD放电路径上current承载能力的;还有point to point resistance检查,是为了检查ESD放电路径的电阻,需要保证它的电阻小于其他路径的电阻,确保静电电流走预设好的放电路径。

PERC还支持layout的检查和schematic的检查,用户就自己设定检查规则,也很方便。

-

反相器

+关注

关注

6文章

329浏览量

44948 -

ERC

+关注

关注

0文章

7浏览量

10104 -

漏电流

+关注

关注

0文章

280浏览量

17842 -

电压波动

+关注

关注

0文章

58浏览量

8628 -

GDS

+关注

关注

0文章

28浏览量

6636

发布评论请先 登录

简单认识eSchema电路设计工具

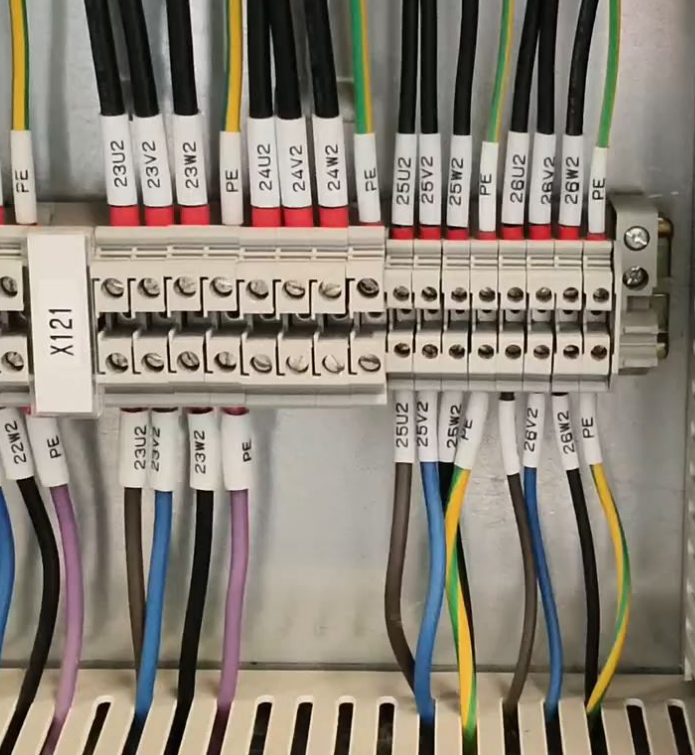

电气设计线号标记规则

Room规则导致网络丢失的情况,有什么好办法解决?

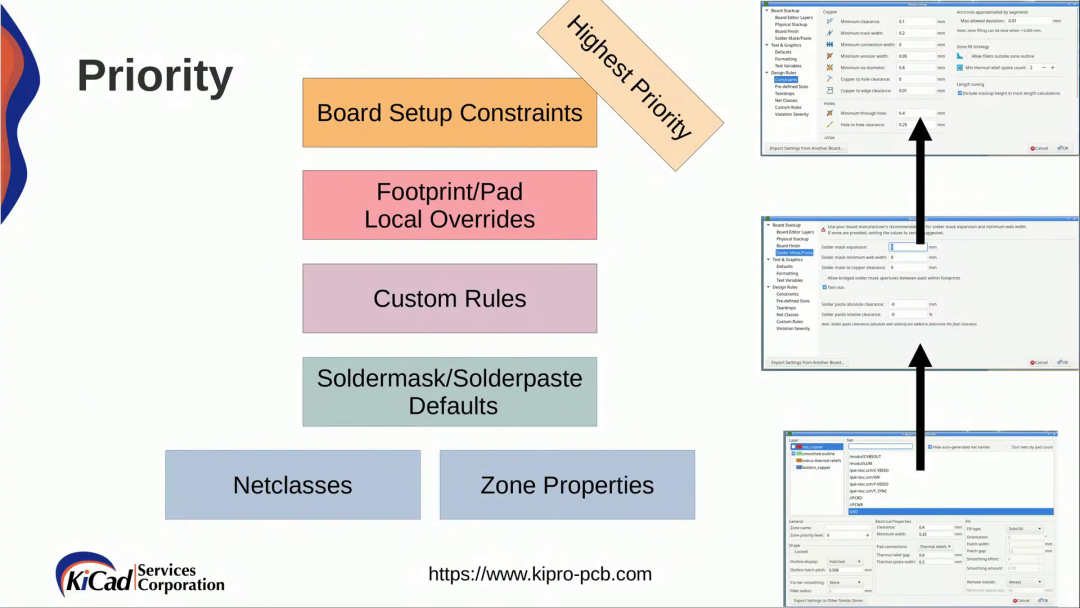

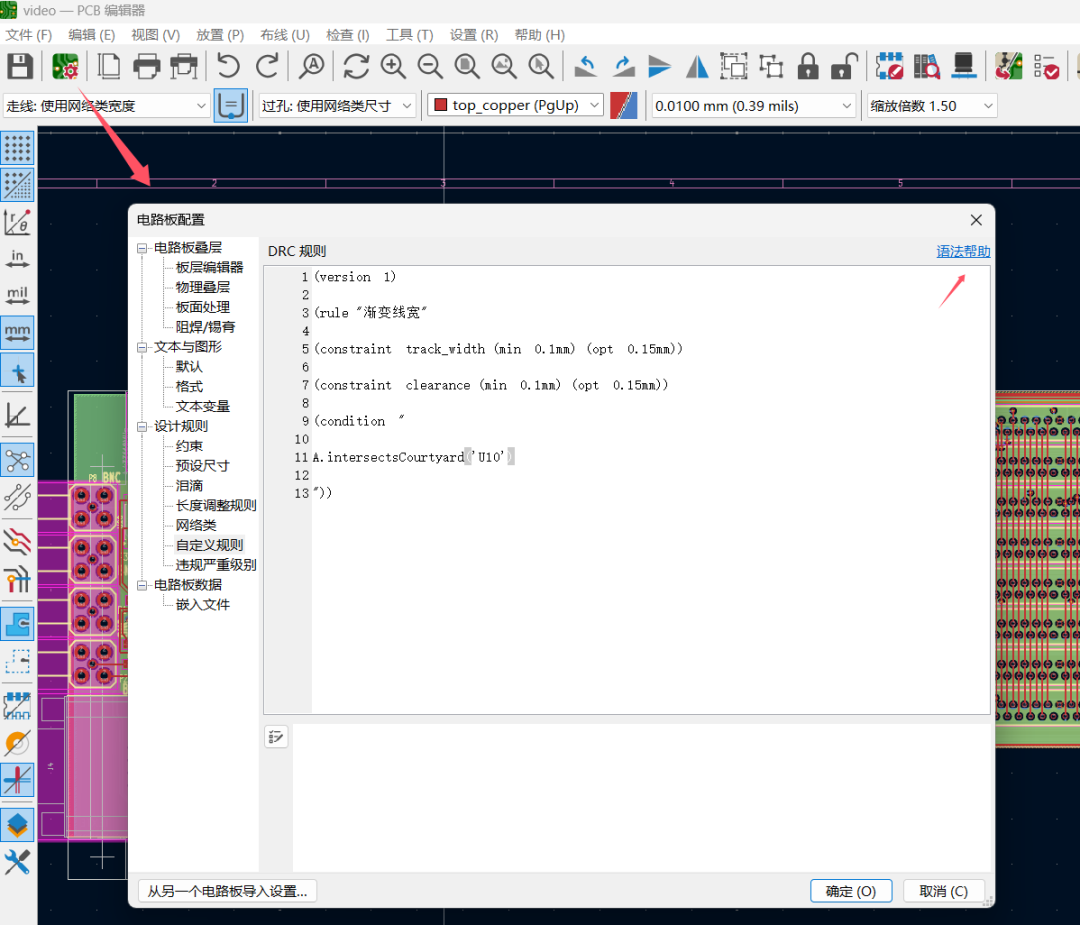

KiCad 中的自定义规则(KiCon 演讲)

新编电气工程师手册

时源芯微 PCB 布线规则详解

概伦电子先进电路检查分析平台工具NanoSpice CCK介绍

Altium Designer中PCB设计规则设置

如何在特定区域设置线宽、线距规则

什么叫电气规则呢?电气规则检查-ERC

什么叫电气规则呢?电气规则检查-ERC

评论