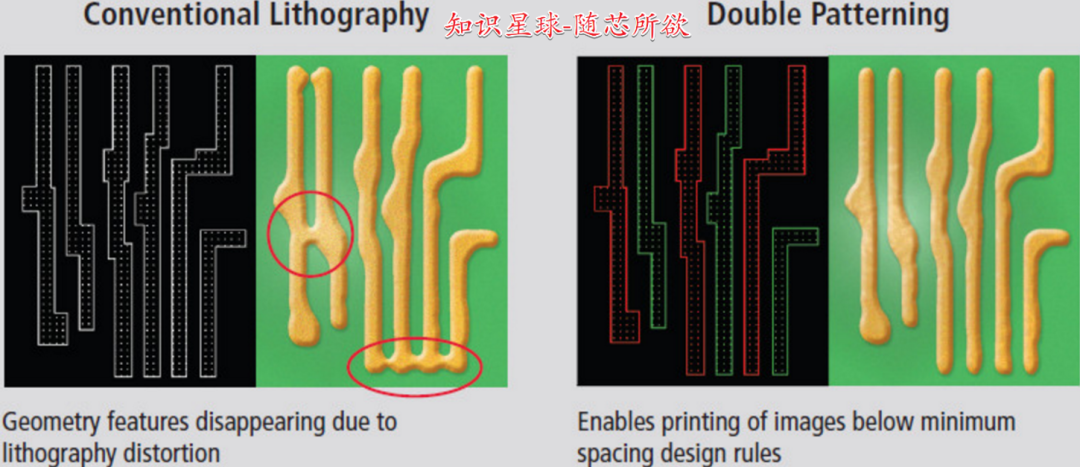

DPT Double Patterning Technology。double pattern就是先进工艺下底层金属/poly加工制造的一种技术,先进工艺下,如果用DUV,光的波长已经无法直接刻出很小的尺寸了(宽度或者间距),所以可以用两层甚至更多层mask来制造一层金属,如下图所示,所以可以看到版图中有红色和绿色(但看一种颜色,它们的间距光刻是可以加工的)。工艺有LELE(光刻 刻蚀 光刻 刻蚀)、LFLE(光刻 freeze 光刻 刻蚀)、SADP(自对准double patterning),以后有空也会专门介绍一下这些工艺。

FinFET是什么?请简要画出FinFET的三维结构,并解释FinFET技术有什么优缺点以及相应的原因。

参考答案:

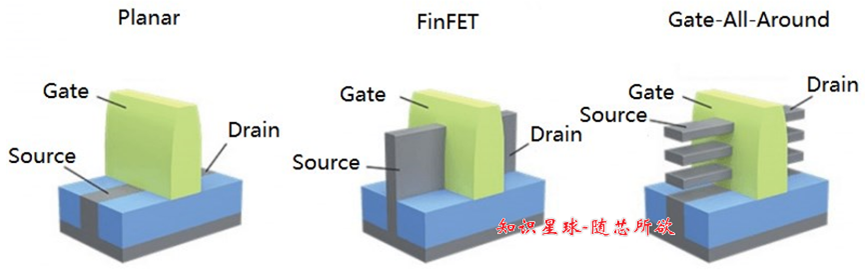

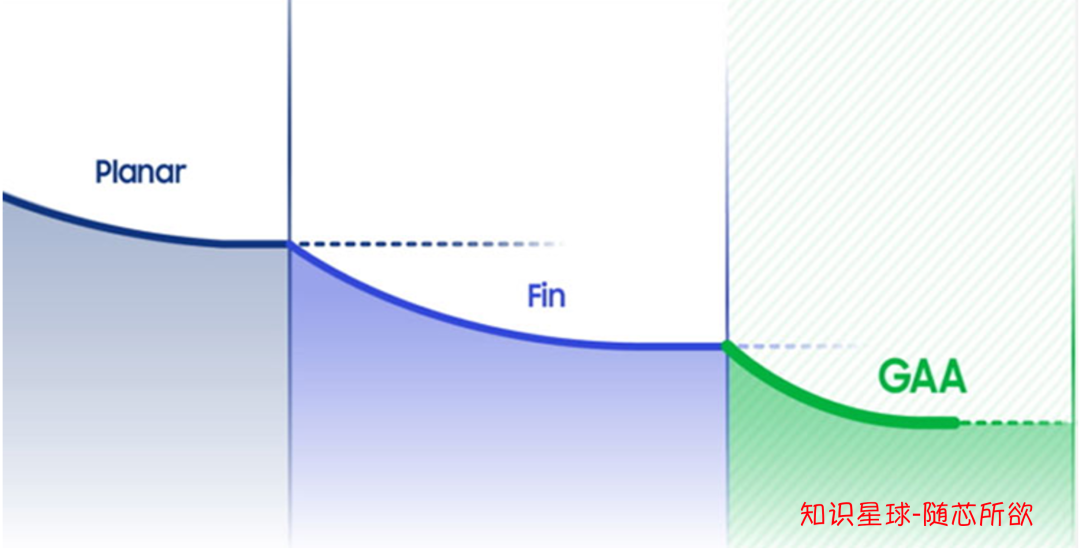

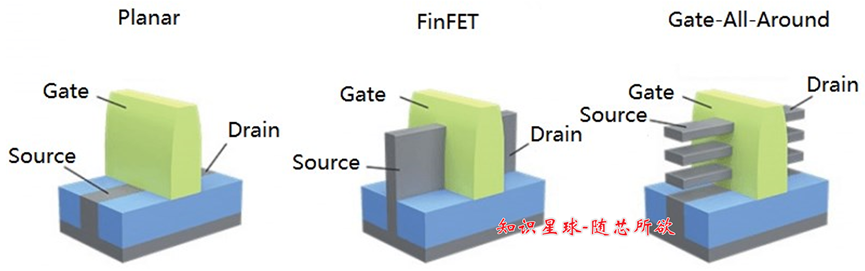

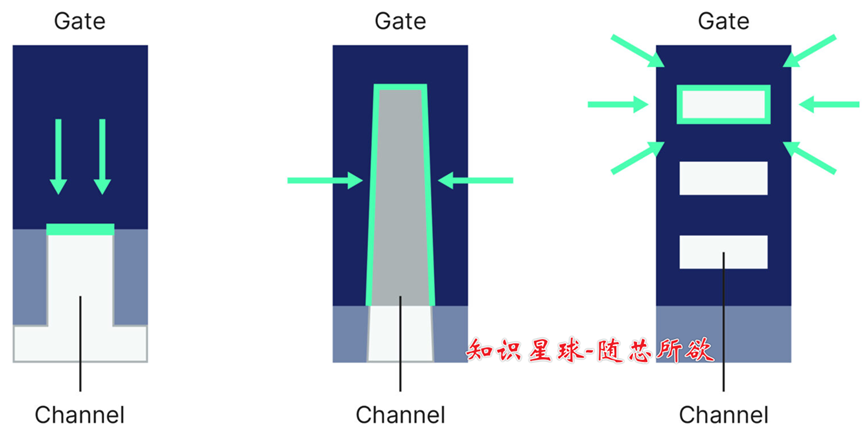

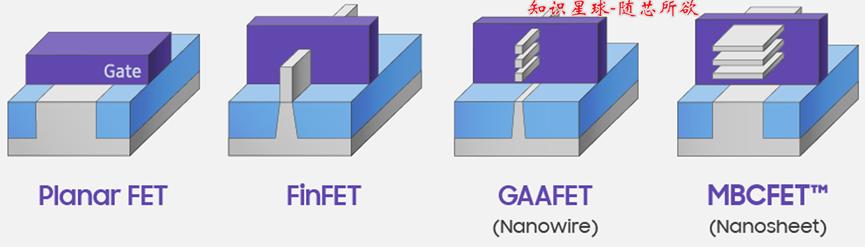

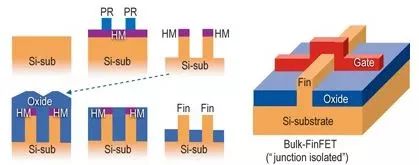

FinFET全称Fin Field-Effect Transistor,中文名叫鳍式场效应晶体管,与平面工艺最大的不同之处是:平面工艺有效沟道只有栅下面的一段,而FinFET则是把栅立了起来,栅包围着沟道,沟道由1个面增大到了3个面,因此栅的控制能力更强了,漏电流会降低,另外MOS管的饱和电流会增大,因此Cell驱动能力会提升,器件速度更快。缺点是在小的面积下有更大的电流,热量不好散发出去,因此对散热的要求会更高。

与之类似,GAA则是FinFET结构的一个升级,由原来的3面的栅升级为了4面环栅,且可以堆叠多层,因此以上特性会得到进一步提升。

可以提出一个类似的问题:

请说出MOS结构有哪些种,它的演变路线以及GAA以及MBCFET的结构与特点

参考答案:

平面工艺到FinFET以及GAA的演变:

GAA(Gate-All-Around):

与前面的FinFET类似,GAA则是FinFET结构的一个升级,由原来的3面的栅升级为了4面环栅,且可以堆叠多层,因此以上特性会得到进一步提升。这种中间堆叠的是尺寸较小的纳米线Nanowire,这种需要堆叠的数量比较多,且加工难度相对比较大。

三星提出了另一种的GAA结构-MBCFET,它用纳米片取代了纳米线,因此加工会相对容易一点,且能得到类似的性能。

问题:

星主,请问有关cut metal的相关概念和常见drc问题能不能有些讲解,比如CM0的spacing问题如何修复,这一层是什么时候加上的,pr工具里看不到这些层但eco后版图里报了一些相关的错误,谢谢

参考答案:

不同时钟串在一个chain的时候中间要加lockup latch,因为不同时钟的latency不同,setup有充足的margin,而hold就很容易有问题了,加上lockup latch之后可以借半个周期的时间,对hold有利,一般加了之后就不会有timing问题了。

backend弟中弟 提问:星主您好,有几个面试问题请教您.

1.flip-chip 与 wirebond 的区别?我回答了下面几个,当时也就想到这几个了,您能补充一下吗?

1.RDL层的厚度不一样;flip-chip会更厚一点;这里追问了为什么?没回答上来.

2.Flip-chip通过RDL层将信号从IO连到core 的中的bump上,bump就是一块八变形的金属块;Wirebond封装是直接将pad放在IO上,封装的时候后从pad上打金线过去。

3.flip-chip的优点,有利于时序以及IR,一般用在比较规模比较大的芯片,追问多大算大?然后后面又问了,为什么这个项目用flip-chip的封装,我当时可能也没回答好?

2.后端中你认为比较有难度的环节是哪个环节,有时候还需要有一些创新的方法来解决问题的,为什么?我回答的是floorplan,但是好像不是面试官想要的答案。

谢谢啦。

星主你好!想请问一个面试的问题。

面试官:Finfet与传统cmos器件有什么区别(这个问题不用此处回答,能答上来)?他们在实际项目中有啥值得注意的地方,比如floorplan阶段?或者比如在DRC方面有何影响?会不会存在检查不到的情况?(这个没答上来。)他接着说你可以关注macro或者cell的user guide(太细了,这个没怎么关注过)。

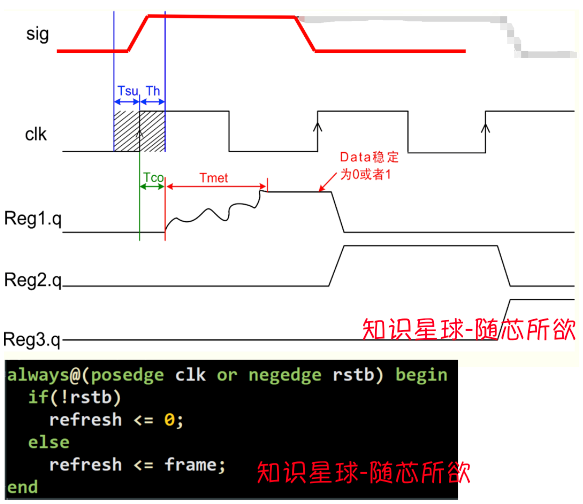

亚稳态与两级reg解决亚稳态问题的原理以及synchronizer的verilog

标签:sync 后端知识 亚稳态

匿名用户 提问:星主,想问问您两个关于“打拍”的问题。

1.图里对sig打拍采样,我不解的是:第一拍是亚稳态,我本来是想采sig的高电平1,结果亚稳态最终稳定在0了,那后面打这一拍也没意义呀,把想要的信号都错过了…

2.图里的Verilog,要是想对frame打两拍去采样,应该咋改啊?

麻烦您了。

问题:

请问,新接触一个工艺,怎么看这个工艺是不是double pattern的呢?不是T的,也不是smic,不是GF,不是三星

标签:DPT 先进工艺

回答:看tf里面对应的layer后边的numMasks,如果有这个属性, 且值大于1就是dpt的,techLEF也是类似

匿名用户 提问:starRC抽取寄生参数时,需要导入std,memory,sub block的gds吗?怎么导入?如果不需要导入的话,看不到这些ip及block的金属层,抽取的rc准确吗

标签:StarRC软件教程

回复:

对于sub block,只用DEF就好了。

对于std cell, memory,项目早期对精度要求没有那么严格,或者GDS没有的情况下,可以用LEF DEF,在项目后期signoff的时候,需要指定GDS。没有GDS的话提取与真实情况会有一些偏差。

审核编辑:汤梓红

-

MOS管

+关注

关注

110文章

2752浏览量

74925 -

FinFET

+关注

关注

12文章

259浏览量

92034 -

数字后端

+关注

关注

0文章

11浏览量

3199 -

GAA

+关注

关注

2文章

38浏览量

7908

原文标题:数字后端先进工艺知识

文章出处:【微信号:集成电路设计及EDA教程,微信公众号:集成电路设计及EDA教程】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

数字IC后端(CAD)

数字IC后端设计介绍,写给哪些想转IC后端的人!

数字后端设计工程师主要干什么?

数字后端设计流程

数字后端关于Litho Grid基本概念介绍详解

数字后端基本概念介绍——Placement Blockage的9中人为约束

介绍数字后端概念--Shape Blockage

数字后端基本概念介绍

浅谈数字后端工程师的工作

数字后端基本概念介绍—FinFET Grid

基于超表面天线阵列的射频前端与数字后端联合抗干扰方案

数字后端先进工艺知识科普

数字后端先进工艺知识科普

评论