技术工艺:晶圆级封装的关键工艺——硅通孔

半导体封装的四个主要作用,包括机械保护、电气连接、机械连接和散热。封装的形状和尺寸各异,保护和连接脆弱集成电路的方法也各不相同。

半导体封装的分类

半导体封装方法,大致可以分为两种:传统封装和晶圆级(Wafer-Level)封装。传统封装首先将晶圆切割成芯片,然后对芯片进行封装;而晶圆级封装则是先在晶圆上进行部分或全部封装,之后再将其切割成单件。

晶圆级封装方法可进一步细分为四种不同类型:

1)晶圆级芯片封装(WLCSP),可直接在晶圆顶部形成导线和锡球(Solder Balls),无需基板;

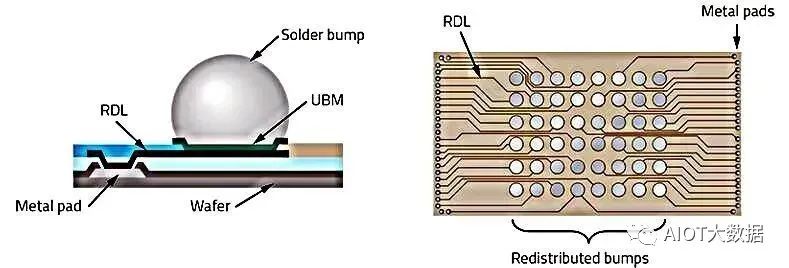

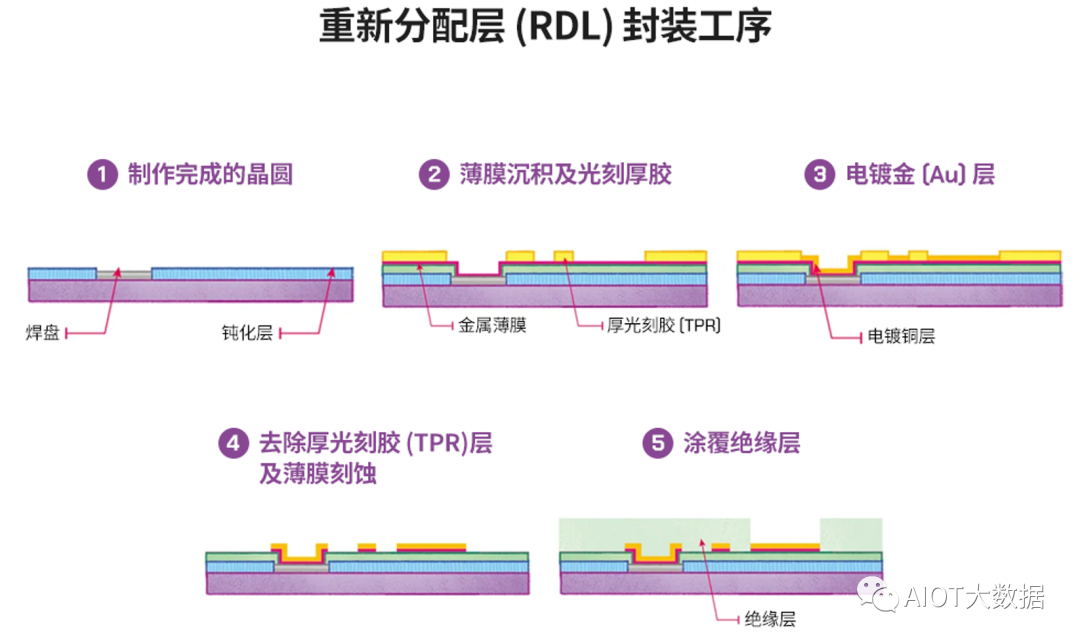

2)重新分配层(RDL),使用晶圆级工艺重新排列芯片上的焊盘位置1,焊盘与外部采取电气连接方式;

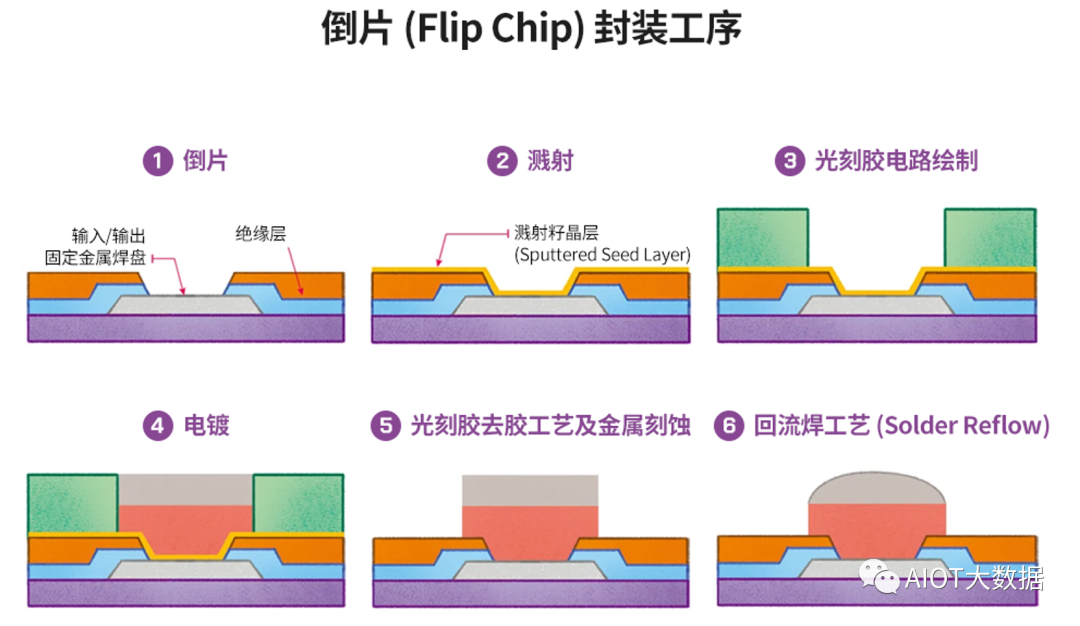

3)倒片(Flip Chip)封装,在晶圆上形成焊接凸点2进而完成封装工艺;

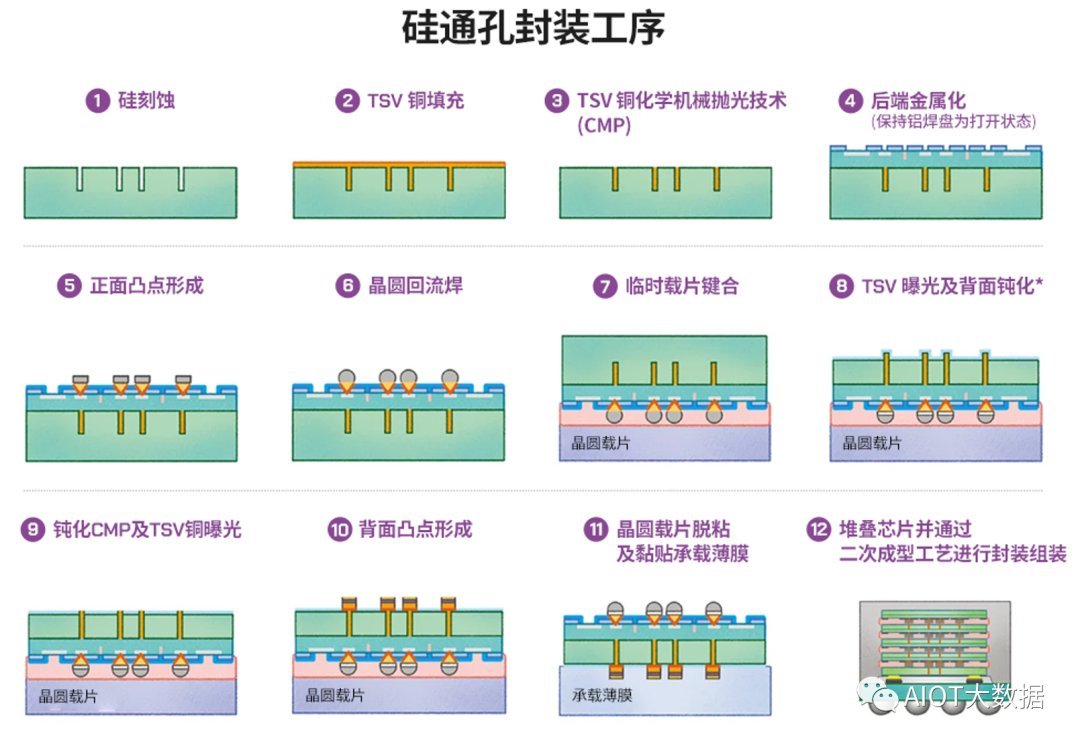

4)硅通孔(TSV)封装,通过硅通孔技术,在堆叠芯片内部实现内部连接。

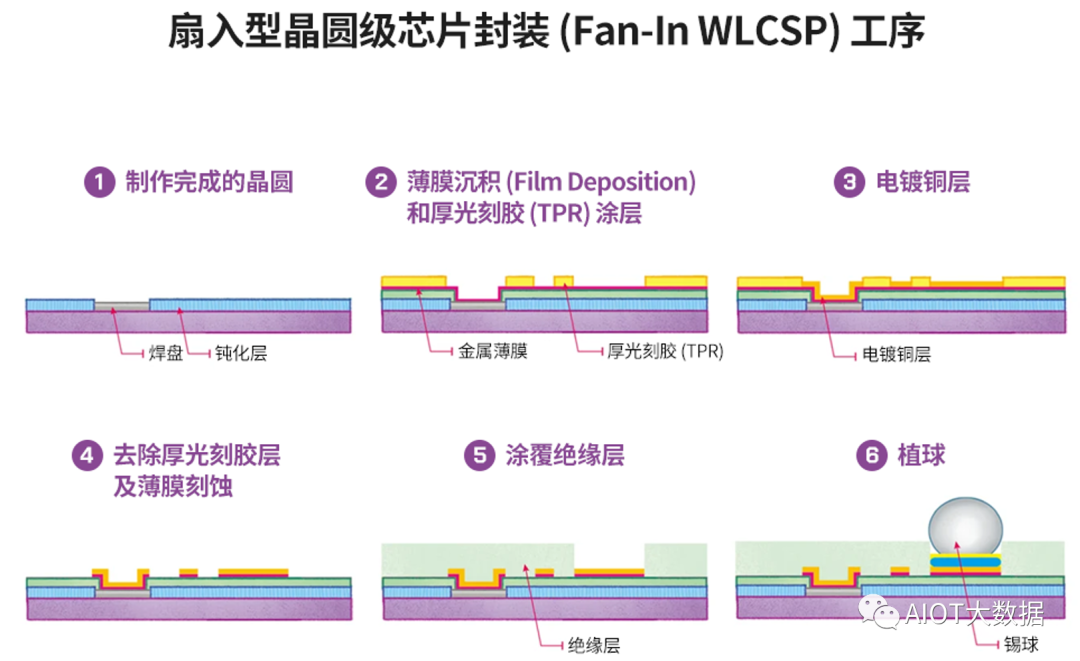

晶圆级芯片封装分为扇入型WLCSP和扇出型WLCSP。

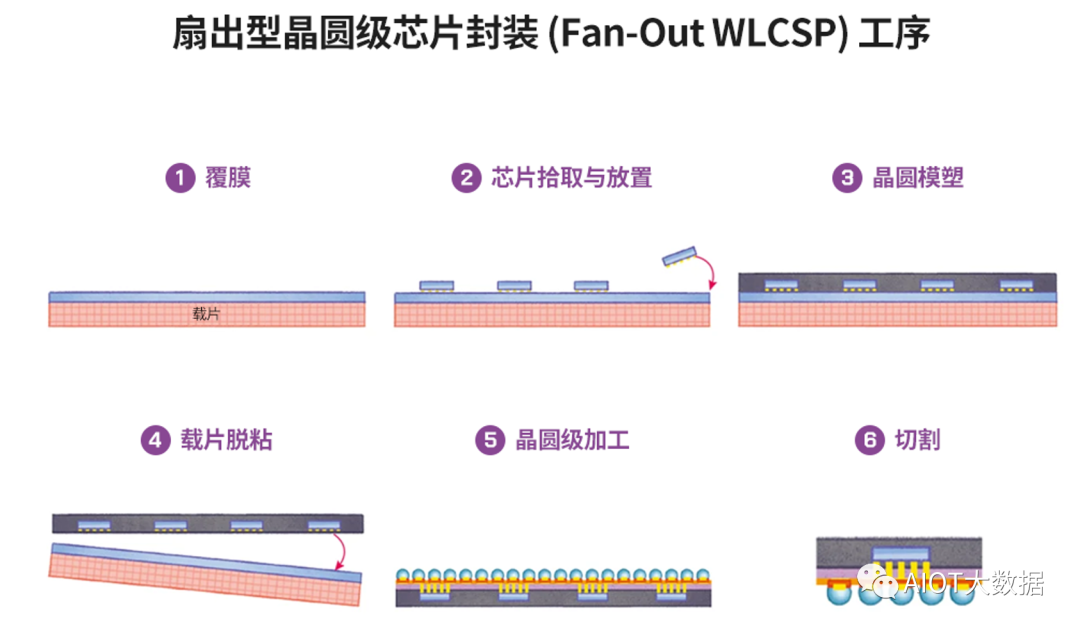

扇入型WLCSP工艺将导线和锡球固定在晶圆顶部,而扇出型WLCSP则将芯片重新排列为模塑3晶圆。这样做是为了通过晶圆级工艺形成布线层,并将锡球固定在比芯片尺寸更大的封装上。

扇入型 (Fan-In) WLCSP (Wafer Level Chip Scale Package)

晶圆级芯片封装的大多数制造过程都是在晶圆上完成的,是晶圆级封装的典型代表。然而,从广义上讲,晶圆级封装还包括在晶圆上完成部分工艺的封装,例如,使用重新分配层、倒片技术和硅通孔技术的封装。在扇入型WLCSP和扇出型WLCSP中,“扇”是指芯片尺寸。扇入型WLCSP的封装布线、绝缘层和锡球直接位于晶圆顶部。与传统封装方法相比,扇入型WLCSP既有优点,也有缺点。

在扇入型WLCSP中,封装尺寸与芯片尺寸相同,都可以将尺寸缩至最小。此外,扇入型WLCSP的锡球直接固定在芯片上,无需基板等媒介,电气传输路径相对较短,因而电气特性得到改善。而且,扇入型WLCSP无需基板和导线等封装材料,工艺成本较低。这种封装工艺在晶圆上一次性完成,因而在裸片(Net Die,晶圆上的芯片)数量多且生产效率高的情况下,可进一步节约成本。

扇入型WLCSP的缺点在于,因其采用硅(Si)芯片作为封装外壳,物理和化学防护性能较弱。正是由于这个原因,这些封装的热膨胀系数与其待固定的PCB基板的热膨胀系数5存在很大差异。受此影响,连接封装与PCB基板的锡球会承受更大的应力,进而削弱焊点可靠性。

存储器半导体采用新技术推出同一容量的芯片时,芯片尺寸会产生变化,扇入型WLCSP的另一个缺点就无法使用现有基础设施进行封装测试。此外,如果封装锡球的陈列尺寸大于芯片尺寸,封装将无法满足锡球的布局要求,也就无法进行封装。而且,如果晶圆上的芯片数量较少且生产良率较低,则扇入型WLCSP的封装成本要高于传统封装。

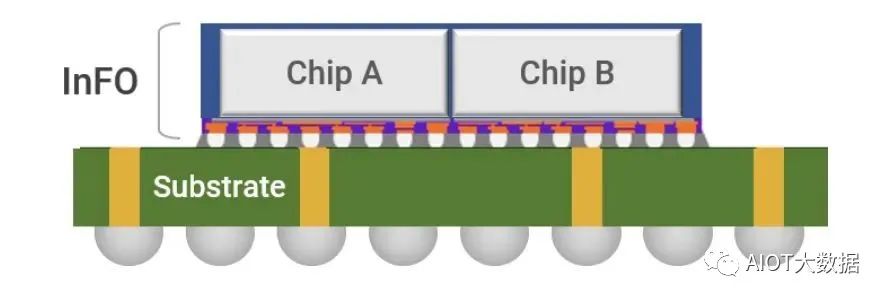

扇出型WLCSP

扇出型WLCSP既保留了扇入型WLCSP的优点,又克服了其缺点。

扇入型WLCSP的所有封装锡球都位于芯片表面,而扇出型WLCSP的封装锡球可以延伸至芯片以外。在扇入型WLCSP中,晶圆切割要等到封装工序完成后进行。因此,芯片尺寸必须与封装尺寸相同,且锡球必须位于芯片尺寸范围内。在扇出型WLCSP中,芯片先切割再封装,切割好的芯片排列在载体上,重塑成晶圆。在此过程中,芯片与芯片之间的空间将被填充环氧树脂模塑料,以形成晶圆。然后,这些晶圆将从载体中取出,进行晶圆级处理,并被切割成扇出型WLCSP单元。

除了具备扇入型WLCSP的良好电气特性外,扇出型WLCSP还克服了扇入型WLCSP的一些缺点。这其中包括:无法使用现有基础设施进行封装测试;封装锡球陈列尺寸大于芯片尺寸导致无法进行封装;以及因封装不良芯片导致加工成本增加等问题。得益于上述优势,扇出型WLCSP在近年来的应用范围越来越广泛。

WLCSP 封装流程

晶圆片级芯片规模封装(Wafer Level Chip Scale Packaging,简称WLCSP),即晶圆级芯片封装方式,不同于传统的芯片封装方式(先切割再封测,而封装后至少增加原芯片20%的体积),此种最新技术是先在整片晶圆上进行封装和测试,然后才切割成一个个的IC颗粒,因此封装后的体积即等同IC裸晶的原尺寸。

WLCSP封装的大致流程:(一般分为Bumping,CP test,WLCSP三个阶段)

Bumping阶段

1. Customer Wafer

这是第一道工序,主要是将从晶圆厂收到的wafer经过Pre-Clean + SRD预处理,然后使用O2 Plasma等离子清洗并烘干,目的是去除来料wafer表面的杂质。

2. PI coating

PI是一层聚合物薄膜层,可以加强芯片的passivation,起到应力缓冲的作用。做法是将预处理后的wafer置于设备吸盘上,wafer正面朝上,在wafer正面喷涂高度光敏感性的光刻胶,设备吸盘高速旋转,使光刻胶均匀喷涂在整个wafer表面。

3.PI Expose

PI曝光是在喷涂光刻胶的wafer与光源(紫外光)中间放入掩膜版(mask),再用紫外光透过掩模照射在硅片表面,被光线照射到的光刻胶会发生反应。光刻胶有正性光刻胶和负性光刻胶两种。正性光刻胶是掩膜版遮挡的区域进行曝光,而负性光刻胶是对掩膜版未遮挡的区域进行曝光。

4.PI Develop

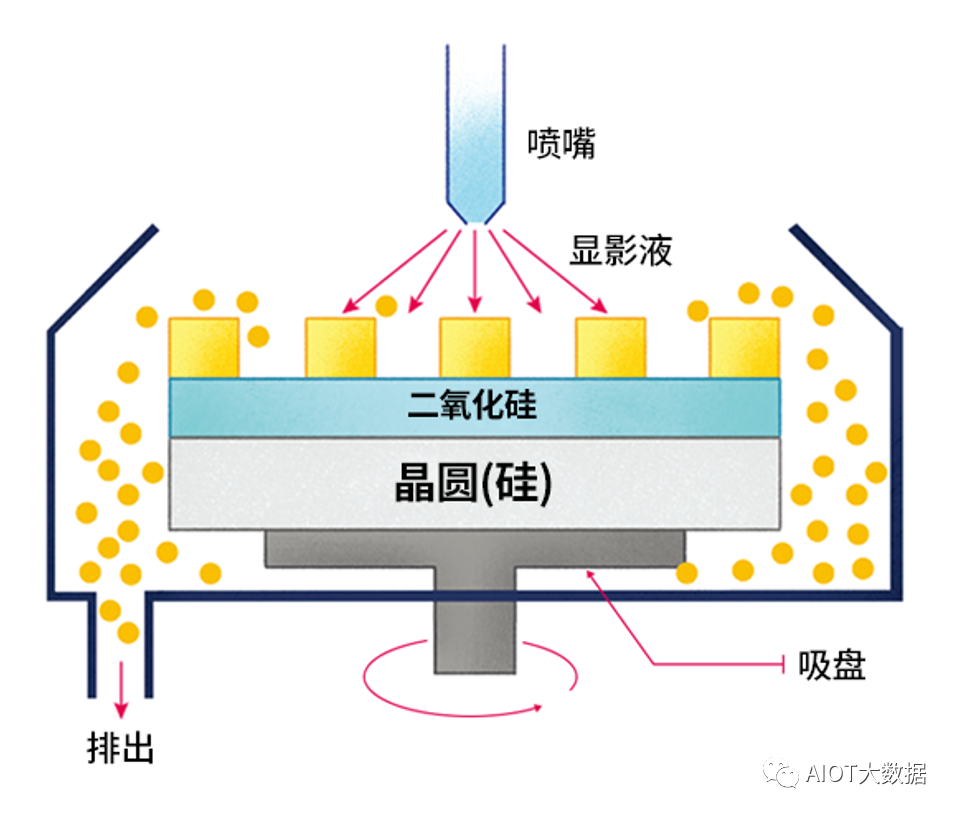

PI显影。与PI Coating原理类似,在wafer正面喷涂显影液,显影液与之前曝光区域形成化学反应后,会将曝光区域显影出来,即形成后续工艺中UBM层所需的一层开口区域。

5.PI CURE

对已显影的wafer进行烘烤,目的是蒸发掉剩余的溶剂使光刻胶变硬,提高光刻胶对硅片表面的粘附性。

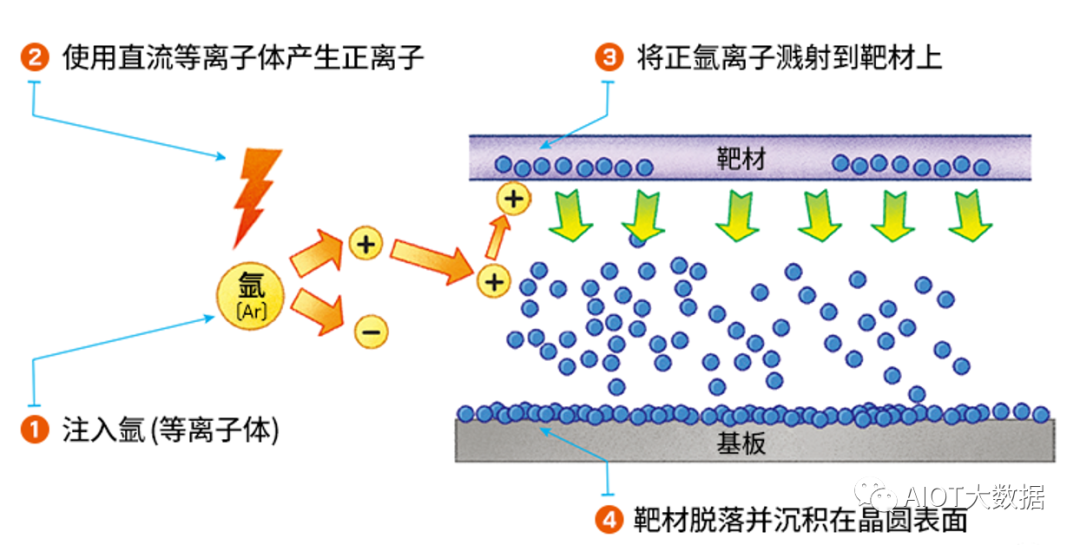

6.Sputter Ti

溅射Ti层。Ti层是组成UBM(under

ball metal)的第一层。UBM层一般有两层组成(有些厂家做三层),第一层为Ti,第二层为Cu。Ti具有高强度,耐腐蚀性等特点,能与AL

PAD和Passivation连接良好,所以Ti层能为UBM层提供高强度的支撑。Sputter

原理是在真空环境下,电极两端加上高压产生直流光辉放电,使加入腔体内的工艺气体(如Plasma)进行电离,电离后的正离子在电压的作用下高速轰击靶材,靶材逸出的原子和分子向wafer表面沉积形成薄膜层,即Ti层。

7.Sputter Cu

溅射UBM的第二层Cu. 此处的Cu一般只有1um左右,只是为了形成一个钝化层面,为后续电镀Cu提供坚实的基础。SputterCu的原理与Sputter Ti类似。

8. PR Coating

PR胶是一种负性光刻胶,是一种间接材料,与PI时的正性光刻胶作用相反。它的作用是为了在后续工艺中将不需要电镀Cu的地方覆盖,这样在电镀Cu时,只在PR胶未覆盖的地方”长”Cu,即UBM开口区域。

9.PR曝光

PR胶曝光同PI曝光原理类似,为了形成UBM开口区域,需通过曝光和显影工序将UBM开口区域多余的化学层去除。

10.PR显影

PR胶显影与PI显影原理类似,在PR曝光区域,利用显影液将曝光区域去除,只留出UBM开口区域。

11.Plating Cu

电镀Cu层,将刚溅射的Cu电镀到一定厚度,不仅为置球提供良好的支撑,也为锡球与wafer内部电路层提供良好的导电连接。此时PR胶覆盖区域就不会”长”Cu,而未覆盖区域”长”出所需要的Cu层。

12.刻蚀(PR, Cu , Ti )

利用化学品分别刻蚀掉UBM开口四周多余的PR层,Cu层,Ti层。至此,一个完整的UBM开口区域就形成了。

13.Ball Mount

置球。UBM开口形成后,就需要将球置于UBM开口上。将带有UBM开口的wafer置于钢网(Stencil)下面,UBM开口与钢网开口一一对齐,然后在钢网上刷上一层助焊剂Flux,最后用刮刀将锡球从钢网开口”落”在UBM开口区域

14.Reflow

回流焊。将置好球的wafer放入回流炉中,锡球在助焊剂flux和高温(大约260°)的作用下慢慢”长大”,并完美的填充UBM开口区域,与wafer形成良好的连接。锡球的作用是建立wafer内部电路与外部电路的”桥梁”。至此,整个Bumping工艺完全结束。

CP test阶段

晶圆测试。将完成回流焊的wafer进行测试,目的是将在bumping工艺中的不良筛选出来,提高后续封装的良率,监测整个bumping工艺的质量。

WLCSP阶段

1. Backside Grind

在wafer正面(球面)贴上一层蓝膜,保护锡球,然后在Wafer背面用磨轮磨至wafer指定厚度。

2. Wafer Backside Coating

在wafer背面刷一层背胶。目的是为了增强wafer的硬度,避免容易造成chipping。然后在一定温度下进行烘烤。(这一步选做,可做可不做)。

3. Marking(丝印)

在wafer背面按照产品要求打上Marking,包括公司Logo,生产日期,产品批次等相关信息。

4.Wafer Saw

Wafer切割。将打好丝印的wafer切割成一粒一粒的芯片。在切割之前,需在wafer背面贴上蓝膜,目的是为切割后的单颗芯片提供保护,不会散落。

5.Tape & Reel

先由顶针将切割后的芯片从蓝膜上一颗一颗顶起,然后由吸嘴吸起来,放在编带中进行卷带,最后包装出货。

以上步骤是整个流程的大致步骤,忽略了一些检验,ball shear之类的动作。

晶圆级封装(WLP)

晶圆级封装的五项基本工艺,包括:光刻(Photolithography)工艺、溅射(Sputtering)工艺、电镀(Electroplating)工艺、光刻胶去胶(PR Stripping)工艺和金属刻蚀(Metal Etching)工艺。

RDL(ReDistribution Layer)重布线层,起着XY平面电气延伸和互联的作用。

来自于《SiP与先进封装技术》

在芯片设计和制造时,IO Pad一般分布在芯片的边沿或者四周:

IO pad是一个芯片管脚处理模块,即可以将芯片管脚的信号经过处理送给芯片内部,又可以将芯片内部输出的信号经过处理送到芯片管脚。

这对于Bond Wire工艺来说自然很方便,但对于Flip Chip来说就有些勉为其难了。

因此,RDL就成为了此时的关键钥匙:

在晶元表面沉积金属层和相应的介质层,并形成金属布线,对IO端口进行重新布局,将其布局到新的,占位更为宽松的区域,并形成面阵列排布。

来自于台积电官网(CoWos-R)示意图

在先进封装的FIWLP (Fan-InWaferLevel Package) 、FOWLP (Fan-Out WaferLevel Package) 中:

RDL是最为关键的技术。

也正是这项技术的兴起,使得封装厂得以在扇出型封装技术上与晶圆厂一较高下。

通过RDL将IOPad进行FIWLP或者FOWLP,形成不同类型的晶圆级封装。

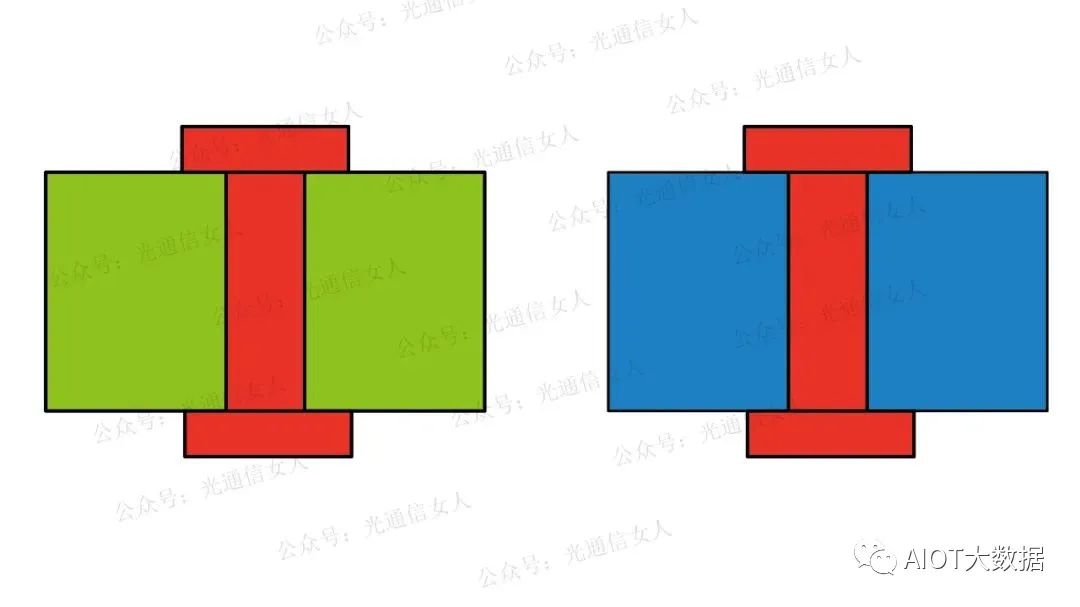

在FIWLP中:

bump全部长在die上,而die和pad的连接主要就是靠RDL的metal line,封装后的IC几乎和die面积接近。Fan-out,bump可以长到die外面,封装后IC也较die面积大(1.2倍)。

FOWLP是:先将die从晶圆上切割下来,倒置粘在载板上(Carrier)

此时载板和die粘合起来形成了一个新的wafer,叫做重组晶圆(Reconstituted Wafer);在重组晶圆中,再曝光长RDL。

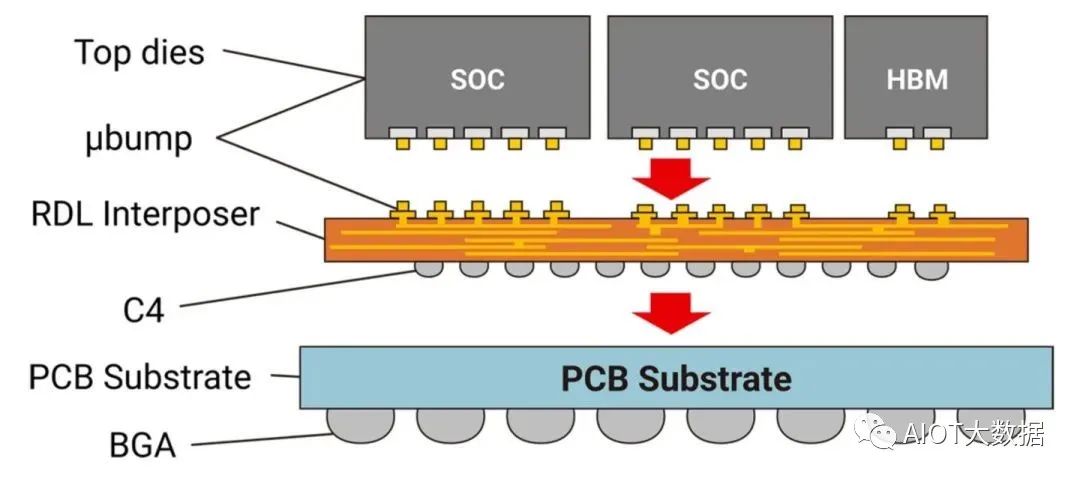

特别是在2.5D先进封装中,除了硅基板上的TSV,RDL同样不可或缺:

来自台积电的InFO(集成扇出)晶圆级封装

以台积电的2.5D先进封装的代表InFO为例:

InFO 在载体上使用(单个或多个)裸片,随后将这些裸片嵌入molding compound的重构晶圆中。

随后在晶圆上制造 RDL 互连和介电层,这是“chip first”的工艺流程。

单die InFO 提供了高凸点数选项,RDL 线从芯片区域向外延伸——即“扇出”拓扑。

讲到这,我们也应该也对RDL技术有了一定的了解。

放眼未来:

RDL工艺的出现和演变也和TSV等先进封装其他工艺一样,是一个不断演变与进化的过程。

但,当下可知的是:

RDL工艺的诞生,已经为先进封装中的异质集成提供了操作上的基础。

高密度扇出封装与细间距嵌入式线路RDL;具有有机介电层的双大马士革工艺(Dual Damascene, DM)铜制程克服了细线路定义的挑战。

封装完整晶圆

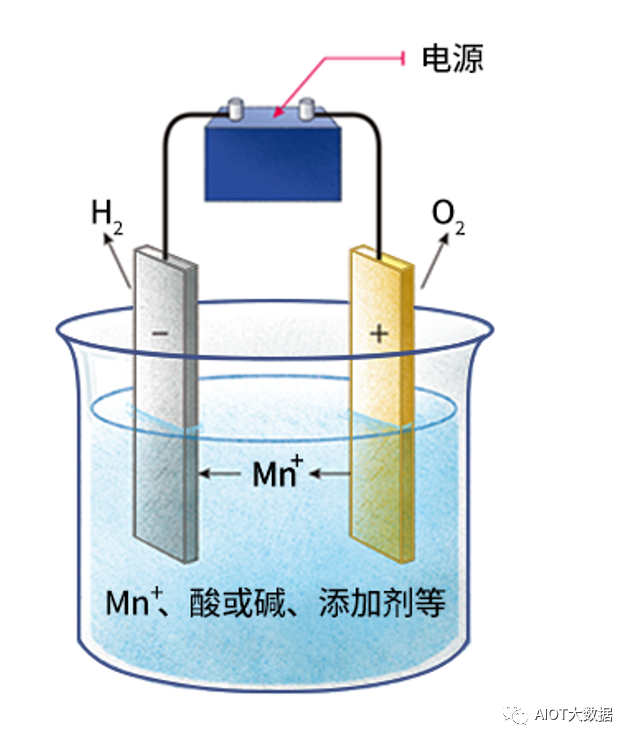

晶圆级封装是指晶圆切割前的工艺。晶圆级封装分为扇入型晶圆级芯片封装(Fan-In WLCSP)和扇出型晶圆级芯片封装(Fan-Out WLCSP),其特点是在整个封装过程中,晶圆始终保持完整。除此之外,重新分配层(RDL)封装、倒片(Flip Chip)封装及硅通孔1(TSV)封装通常也被归类为晶圆级封装,尽管这些封装方法在晶圆切割前仅完成了部分工序。不同封装方法所使用的金属及电镀(Electroplating)2绘制图案也均不相同。不过,在封装过程中,这几种方法基本都遵循如下顺序。

1硅通孔(TSV , Through-Silicon Via): 一种可完全穿过硅裸片或晶圆实现硅片堆叠的垂直互连通道。

2电镀 (Electroplating): 一项晶圆级封装工艺,通过在阳极上发生氧化反应来产生电子,并将电子导入到作为阴极的电解质溶液中,使该溶液中的金属离子在晶圆表面被还原成金属。

完成晶圆测试后,根据需求在晶圆上制作绝缘层(Dielectric Layer)。初次曝光后,绝缘层通过光刻技术再次对芯片焊盘进行曝光。然后,通过溅射(Sputtering)3工艺在晶圆表面涂覆金属层。此金属层可增强在后续步骤中形成的电镀金属层的黏附力,同时还可作为扩散阻挡层以防止金属内部发生化学反应。

此外,金属层还可在电镀过程中充当电子通道。之后涂覆光刻胶(Photoresist)以形成电镀层,并通过光刻工艺绘制图案,再利用电镀形成一层厚的金属层。电镀完成后,进行光刻胶去胶工艺,采用刻蚀工艺去除剩余的薄金属层。最后,电镀金属层就在晶圆表面制作完成了所需图案。这些图案可充当扇入型WLCSP的引线、重新分配层封装中的焊盘再分布,以及倒片封装中的凸点。下文将对每道工序进行详细介绍。

3溅射 (Sputtering): 一项利用等离子体束对靶材进行物理碰击,使靶材粒子脱落并沉积在晶圆上的工艺。

▲图1:各类晶圆级封装工艺及相关步骤

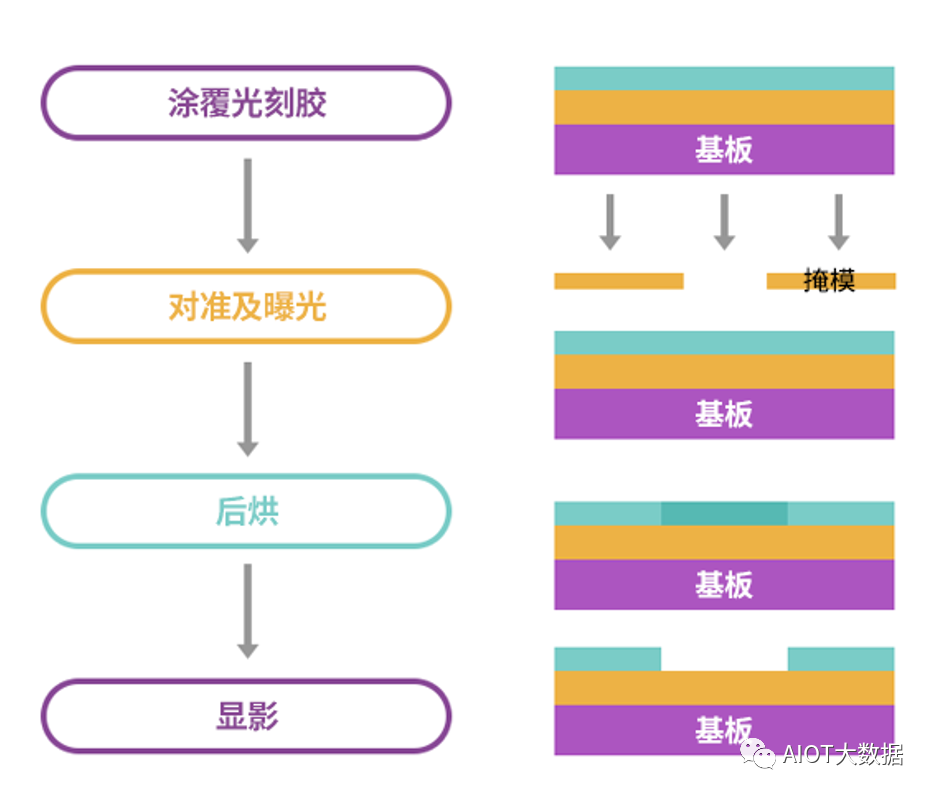

光刻工艺:在掩模晶圆上绘制电路图案

光刻对应的英文是Photolithography,由“-litho(石刻)”和“graphy(绘图)”组成,是一种印刷技术,换句话说,光刻是一种电路图案绘制工艺。首先在晶圆上涂覆一层被称为“光刻胶”的光敏聚合物,然后透过刻有所需图案的掩模,选择性地对晶圆进行曝光,对曝光区域进行显影,以绘制所需的图案或图形。该工艺的步骤如图2所示。

▲图2:光刻工艺步骤

在晶圆级封装中,光刻工艺主要用于在绝缘层上绘制图案,进而使用绘制图案来创建电镀层,并通过刻蚀扩散层来形成金属线路。

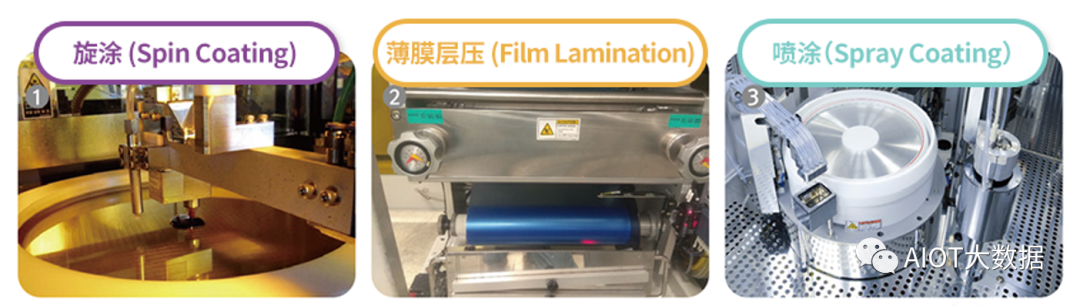

为更加清楚地了解光刻工艺,不妨将其与摄影技术进行比较。摄影以太阳光作为光源来捕捉拍摄对象,对象可以是物体、地标或人物。而光刻则需要特定光源将掩模上的图案转移到曝光设备上。另外,摄像机中的胶片也可类比为光刻工艺中涂覆在晶圆上的光刻胶。如图4所示,我们可以通过三种方法将光刻胶涂覆在晶圆上,包括旋涂(Spin Coating)、薄膜层压(Film Lamination)和喷涂(Spray Coating)。涂覆光刻胶后,需用通过前烘(Soft Baking)来去除溶剂,以确保粘性光刻胶保留在晶圆上且维持其原本厚度。

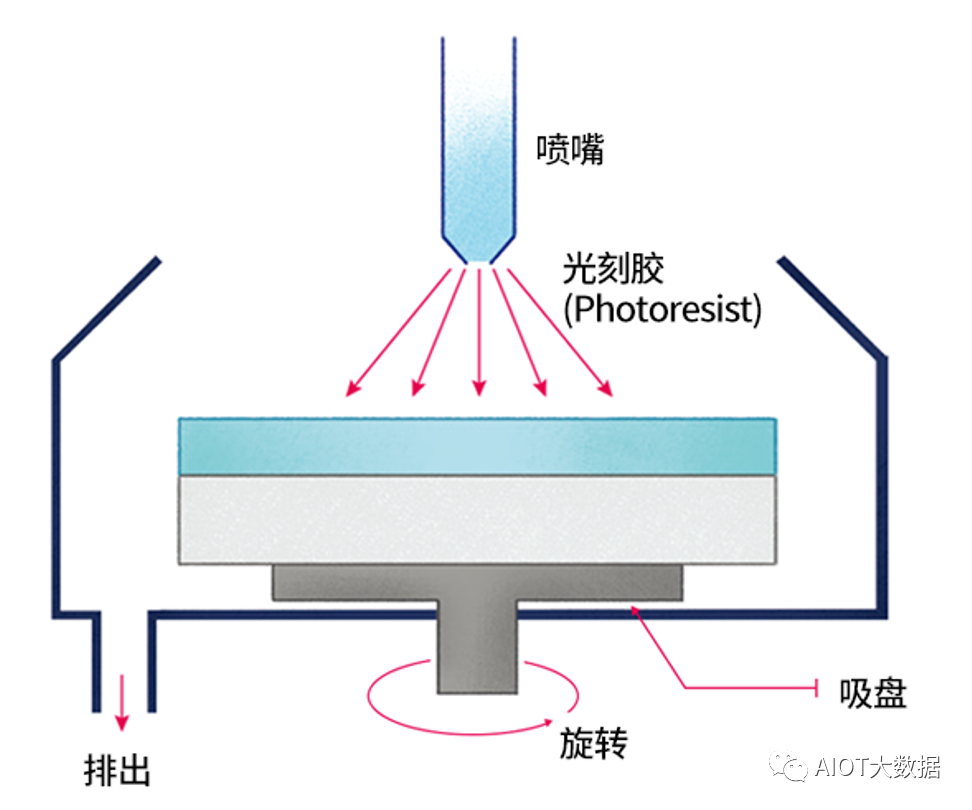

如图5所示,旋涂将粘性光刻胶涂覆在旋转着的晶圆中心,离心力会使光刻胶向晶圆边缘扩散,从而以均匀的厚度分散在晶圆上。粘度越高转速越低,光刻胶就越厚。反之,粘度越低转速越高,光刻胶就越薄。对于晶圆级封装而言,特别是倒片封装,光刻胶层的厚度须达到30 μm至100 μm,才能形成焊接凸点。然而,通过单次旋涂很难达到所需厚度。

在某些情况下,需要反复旋涂光刻胶并多次进行前烘。因此,在所需光刻胶层较厚的情况下,使用层压方法更加有效,因为这种方法从初始阶段就能够使光刻胶薄膜达到所需厚度,同时在处理过程中不会造成晶圆浪费,因此成本效益也更高。但是,如果晶圆结构表面粗糙,则很难将光刻胶膜附着在晶圆表面,此种情况下使用层压方法,会导致产品缺陷。所以,针对表面非常粗糙的晶圆,可通过喷涂方法,使光刻胶厚度保持均匀。

▲图4:光刻胶涂覆的三种方法

▲图5:旋涂方法示意图

完成光刻胶涂覆和前烘后,接下来就需要进行曝光。通过照射,将掩模上的图案投射到晶圆表面的光刻胶上。由于正性光刻胶(Positive PR)在曝光后会软化,因此使用正性光刻胶时,需在掩模去除区开孔。负性光刻胶(Negative PR)在曝光后则会硬化,所以需在掩模保留区开孔。晶圆级封装通常采用掩模对准曝光机(Mask Aligner)4或步进式***(Stepper)5作为光刻工艺设备。

4掩模对准曝光机(Mask Aligner): 一种将掩模上的图案与晶圆进行对准,使光线穿过掩模并照射在晶圆表面的曝光设备。

5步进式***(Stepper): 一种在工件台逐步移动时,通过开启和关闭快门控制光线以进行光刻的机器。

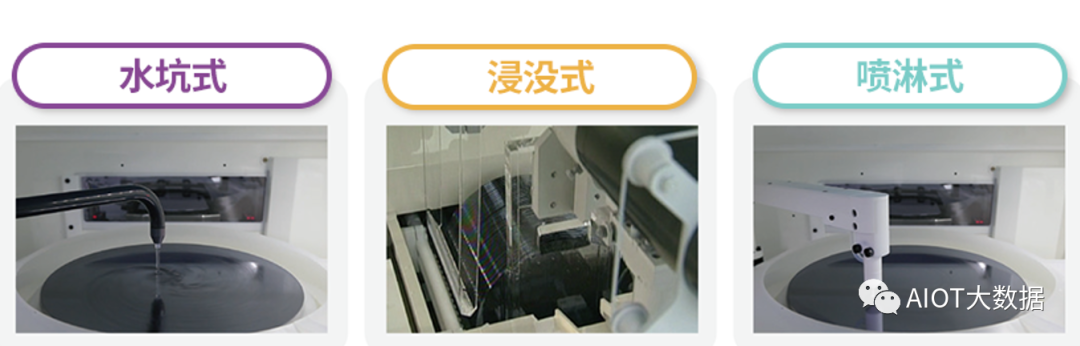

显影(Development)是一种利用显影液来溶解因光刻工艺而软化的光刻胶的工艺。如图6所示,显影方法可分为三种,包括:水坑式 显影(Puddle Development),将显影液倒入晶圆中心,并进行低速旋转;浸没式显影(Tank Development),将多个晶圆同时浸入显影液中;喷淋式显影(Spray Development),将显影液喷洒到晶圆上。图7显示了静态显影方法的工作原理。完成静态显影后,通过光刻技术使光刻胶形成所需的电路图案。

▲图6:三种不同的显影方法

▲图7:水坑式显影方法的工作原理

溅射工艺:在晶圆表面形成薄膜

溅射是一种在晶圆表面形成金属薄膜的物理气相沉积(PVD)6工艺。如果晶圆上形成的金属薄膜低于倒片封装中的凸点,则被称为凸点下金属层(UBM,Under Bump Metallurgy)。通常凸点下金属层由两层或三层金属薄膜组成,包括:增强晶圆粘合性的黏附层;可在电镀过程中提供电子的载流层;以及具有焊料润湿性(Wettability)7,并可阻止镀层和金属之间形成化合物的扩散阻挡层。例如薄膜由钛、铜和镍组成,则钛层作为黏附层,铜层作为载流层,镍层作为阻挡层。因此,UBM对确保倒片封装的质量及可靠性十分重要。在RDL和WLCSP等封装工艺中,金属层的作用主要是形成金属引线,因此通常由可提高粘性的黏附层及载流层构成。

如图8所示,在溅射工艺中,首先将氩气转化为等离子体(Plasma)8,然后利用离子束碰击靶材(Target),靶材的成分与沉积正氩离子的金属成分相同。碰击后,靶材上的金属颗粒会脱落并沉积在晶圆表面。通过溅射,沉积的金属颗粒具有一致的方向性。尽管晶圆平坦区经过沉积后厚度均匀,但沟槽或垂直互连通路(通孔)的沉积厚度可能存在差异,因此就沉积厚度而言,此类不规则形状会导致平行于金属沉积方向的基板表面的沉积厚度,比垂直于金属沉积方向的基板表面沉积厚度薄。

6物理气相沉积(PVD): 一种产生金属蒸气,并将其作为一种厚度较薄且具有粘性的纯金属或合金涂层沉积在导电材料上的工艺。

7润湿性(Wettability): 因液体和固体表面的相互作用,使液体在固体表面扩散的现象。

8等离子体(Plasma): 一种因质子和电子的自由运动而呈电中性的物质状态。当持续对气体状物质进行加热使其升温时,便会产生由离子和自由电子组成的粒子集合体。等离子体也被视为固态、液态和气态之外的“第四种物质状态”。

▲图8:溅射的基本原理

电镀工艺:形成用于键合的金属层

电镀是将电解质溶液中的金属离子还原为金属并沉积在晶圆表面的过程,此过程是需要通过外部提供的电子进行还原反应来实现的。在晶圆级封装中,采用电镀工艺形成厚金属层。厚金属层可充当实现电气连接的金属引线,或是焊接处的凸点。如图9所示,阳极上的金属会被氧化成离子,并向外部电路释放电子。在阳极处被氧化的及存在于溶液中的金属离子可接收电子,在经过还原反应后成为金属。

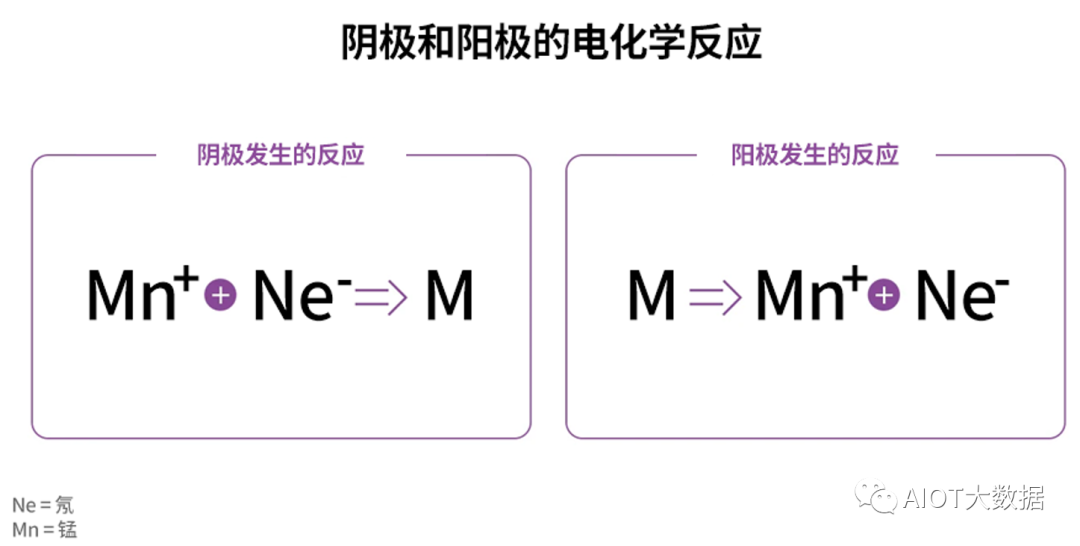

在晶圆级封装的电镀工艺中,阴极为晶圆。阳极由作为电镀层的金属制成,但也可使用如铂金的不溶性电极(Insoluble Electrode)9。如果阳极板由作为镀层的金属制成,金属离子就会从阳极板上溶解并持续扩散,以保持溶液中离子浓度的一致性。如果使用不溶性电极,则必须定期补充溶液中因沉积到晶圆表面而消耗的金属离子,以维持金属离子浓度。图10展示了阴极和阳极分别发生的电化学反应。

9不溶性电极(Insoluble Electrode): 一种主要用于电解和电镀的电极。它既不溶于化学溶液,也不溶于电化学溶液。铂金等材料常被用于制作不溶性电极。

▲图9:电镀过程

▲图10:阴极和阳极电化学反应公式

在放置晶圆电镀设备时,通常需确保晶圆的待镀面朝下,同时将阳极置于电解质溶液中。当电解质溶液流向晶圆并与晶圆表面发生强力碰撞时,就会发生电镀。此时,由光刻胶形成的电路图案会与待镀晶圆上的电解质溶液接触。电子分布在晶圆边缘的电镀设备上,最终电解质溶液中的金属离子与光刻胶在晶圆上绘制的图案相遇。随后,电子与电解质溶液中的金属离子结合,在光刻胶绘制图案的地方进行还原反应,形成金属引线或凸点。

光刻胶去胶工艺和金属刻蚀工艺:去除光刻胶

在所有使用光刻胶图案的工艺步骤完成后,必须通过光刻胶去胶工艺来清除光刻胶。光刻胶去胶工艺是一种湿法工艺,采用一种被称为剥离液(Stripper)的化学溶液,通过水坑式、浸没式,或喷淋式等方法来实现。通过电镀工艺形成金属引线或凸点后,需清除因溅射形成的金属薄膜。这是非常必要的一个步骤,因为如果不去除金属薄膜,整个晶圆都将被电气连接从而导致短路。可采用湿刻蚀(Wet Etching)工艺去除金属薄膜,以酸性刻蚀剂(Etchant)溶解金属。这种工艺类似于光刻胶去胶工艺,随着晶圆上的电路图案变得越来越精细,水坑式方法也得到了更广泛的应用。

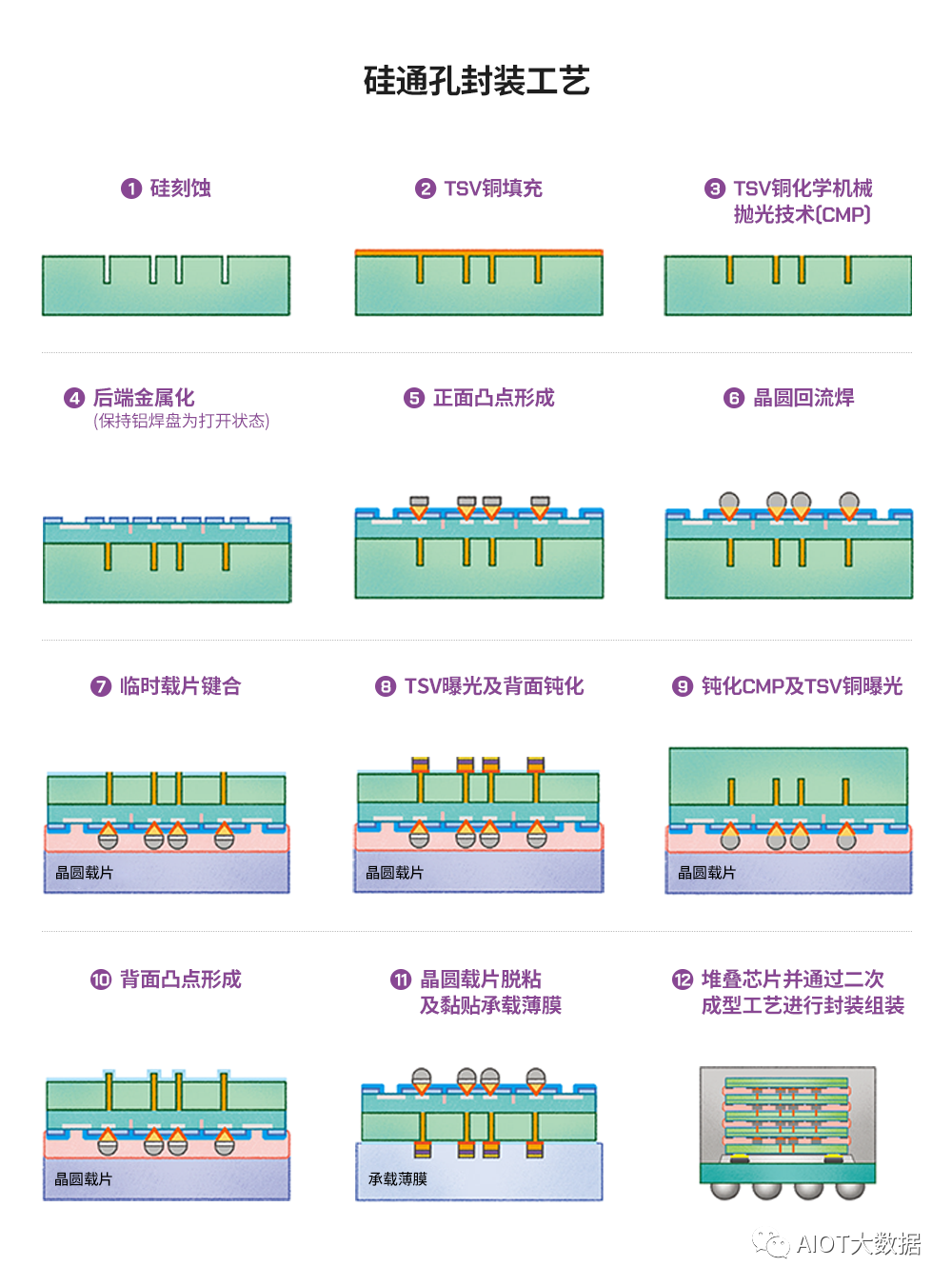

硅通孔封装工艺

图6展示了采用中通孔(Via-middle)5方法的硅通孔封装工艺步骤。首先在晶圆制造过程中形成通孔。随后在封装过程中,于晶圆正面形成焊接凸点。之后将晶圆贴附在晶圆载片上并进行背面研磨,在晶圆背面形成凸点后,将晶圆切割成独立芯片单元,并进行堆叠。5中通孔(Via Middle):一种硅通孔工艺方法,在互补金属氧化物半导体形成后及金属层形成之前开展的工序。接下来,将简单概括中通孔的基本工序。首先在前道工序(Front-end of Line)中,在晶圆上制作晶体管,如互补金属氧化物半导体等。

随后使用硬掩模(Hard Mask)6在硅通孔形成区域绘制电路图案。之后利用干刻蚀(Dry Etching)工艺去除未覆盖硬掩膜的区域,形成深槽。再利用化学气相沉积工艺(Chemical Vapor Deposition)制备绝缘膜,如氧化物等。这层绝缘膜将用于隔绝填入槽中的铜等金属物质,防止硅片被金属物质污染。此外绝缘层上还将制备一层金属薄层作为屏障。6硬掩膜(Hard Mask):一种由硬质材料而非软质材料制成的薄膜,用于绘制更为精细的电路图案。硬掩膜本身对光线并不敏感,所以需使用光刻胶才能进一步绘制电路图案,以最终实施刻蚀工艺。此金属薄层将被用于电镀铜层。电镀完成后,采用化学机械抛光(Chemical Mechanical Polishing)技术使晶圆表面保持平滑,同时清除其表面铜基材,确保铜基材只留在沟槽中。然后通过后道工序(Back-end of Line)完成晶圆制造。

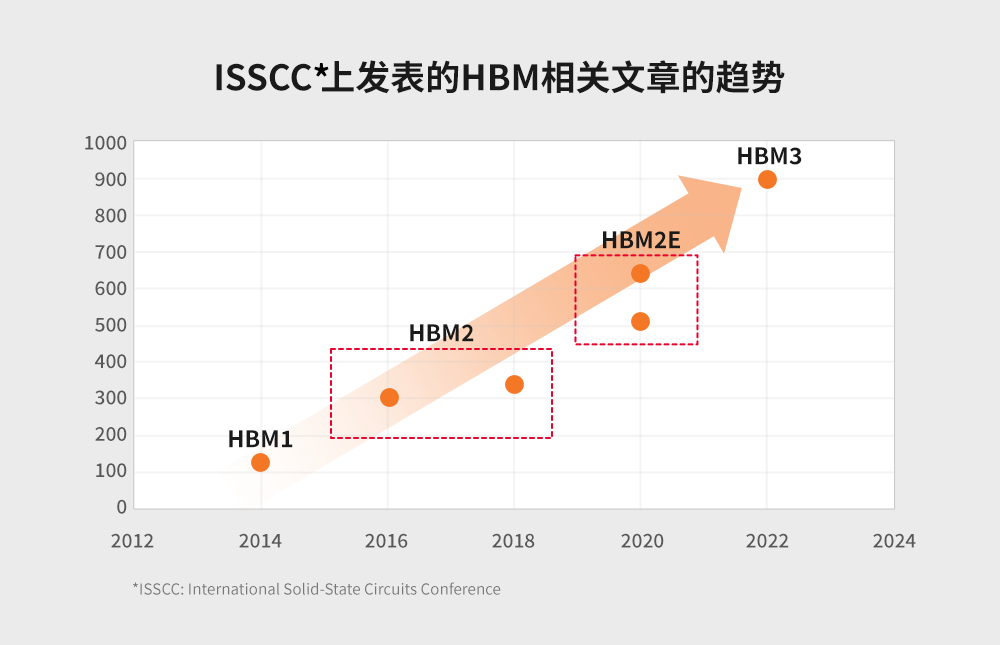

▲图6:硅通孔封装工序(ⓒ HANOL出版社)使用硅通孔技术制造芯片堆叠封装体时,一般可采用两种类型的封装方法。第一种方法是利用3D芯片堆叠技术的基板封装。第二种方法则需创建KGSD,然后基于KGSD来制作2.5D或3D封装。下文将详细介绍如何创建KGSD,以及如何基于KGSD来制作2.5D封装的过程。作为利用硅通孔技术制作而成的芯片堆叠封装体,制作KGSD必需经历额外封装工艺,如2.5D封装、3D封装以及扇出型晶圆级芯片封装等,高带宽存储器(HBM)就是KGSD产品的一个典型例子。由于KGSD需经历额外封装工艺,其作为连接引脚的焊接凸点需要比传统锡球更加精细。因此3D封装体中芯片堆叠在基板上,而KGSD中的芯片则堆叠于晶圆上方,晶圆也可以视为KGSD的最底层芯片。就HBM而言,位于最底层的芯片被称为基础芯片或基础晶圆,而位于其上方的芯片则被称为核心芯片。此方法工序如下:首先,通过倒片工艺在基础晶圆和核心晶圆的正面制作凸点。在制作2.5D封装体时,基底晶圆需要排列凸点,使之能够附着到中介层(Interposer);相反,核心晶圆上的凸点布局则是有助于晶圆正面的芯片堆叠。在晶圆正面形成凸点后,应减薄晶圆,同时也需在晶圆背面形成凸点。然而,正如前文在介绍背面研磨工艺时所述,需注意在减薄过程中导致晶圆弯曲。在传统封装工艺中,进行减薄之前,可将晶圆贴附到贴片环架上,以防止晶圆弯曲,但在硅通孔封装工艺中,由于凸点形成于晶圆背面,所以这种保护方法并不适用。为解决此问题,晶圆承载系统(Wafer Support System)应运而生。利用晶圆承载系统,可借助临时粘合剂将带有凸点的晶圆正面贴附于晶圆载片上,同时对晶圆背面进行减薄处理。此时晶圆贴附于晶圆载片上,即使经过减薄也不会发生弯曲。此外,因晶圆载片与晶圆形式相同,因此也可使用晶圆设备对其进行加工。

基于此原理,可在核心晶圆的背面制作凸点,当核心晶圆正面及背面上的凸点均制作完成时,便可对载片进行脱粘。随后将晶圆贴附于贴片环架中,并参照传统封装工艺,对晶圆进行切割。基础晶圆始终贴附于晶圆载片上,从核心晶圆上切割下来的芯片则堆叠于基础晶圆之上。芯片堆叠完成后,再对基础晶圆进行模塑,而后进行晶圆载片脱粘。至此,基础晶圆就变成了堆叠有核心晶圆的模制晶圆。随后对晶圆进行研磨,使其厚度达到制作2.5D封装体所需标准,然后再将其切割成独立的芯片单元,以制作KGSD。HBM成品包装后将运送至制作2.5D封装体的客户手中。

硅通孔(TSV)

硅通孔(TSV) 是当前技术先进性最高的封装互连技术之一。基于 TSV 封装的核心工艺包括 TSV 制造、RDL/微凸点加工、衬底减薄、圆片键合与薄圆片拿持等。

(1)TSV 制造:TSV 制造可以分为两种类型,类型I是孔底部不需要直接导电连接的制造类型,类型II是孔底部需要直接导电连接的制造类型。TSV 制造的主要工艺步骤包括孔刻蚀、绝缘层沉积、扩散阻挡层/种子层沉积、导电材料填充及表面平坦化等。对于孔底部需要直接导电连接的类型,在完成绝缘层沉积后,需要选择性地将孔底部绝缘层去除。

(2)RDL/微凸点加工:再布线层提供了 TSV 及讨底上已有电路或器件的电学重分布,可为 TSV 提供更多的连接自由度,微凸点主要用于实现TSV衬底与其他芯片或封装基板的直接电学连接。对于线宽小于 1μm 的RDL,需要用到镶嵌工艺(又称大马士革工艺);对于线宽为 1μm 以上的 RDL,可采用厚膜掩模电镀加成式工艺来实现。

(3)衬底减薄:根据工艺流程设计,衬底减薄分为有 TSV 孔的减薄和无TSV 孔的减薄两种情况。对于减薄时衬底内无 TSV 的情况,仅需要处理硅材料,相对比较容易,只要保证处理后的表面平整度即可。对于减薄时衬底内包含TSV 的情况,在减薄完成后,需要将 TSV 从衬底背面露出来,因此应考虑硅与TSV 填充材料(如铜)的同步研磨或抛光,并应控制填充材料不能与衬底硅导通或污染衬底硅。

(4)圆片键合与薄圆片拿持:在圆片减薄完成后,往往还需要很多后续工艺或临时性工艺,其日的是提高生产过程中的成品率与效率,因此要保证薄圆片在这些工艺步骤中的安全,通常这是通过与承载片键合保护来实现的。如果承载片是功能性的,则键合 是一种永久键合。根据所使用的中间层材料,永久键合可以分为氧化硅键合、聚合物键合、金属键合,以区这些键合的混合形式等。当承载圆片是非功能性的衬底时,需要临时性的键合,以便在后续工艺过程中实现键合分离。

实现薄圆片拿持的基本工艺思路是,首先将待减薄圆片与一个承载圆片键合,之后进行圆片减薄及减薄后的工艺加工,最后将承载圆片拆除,从而完成薄圆片的加工。

根据工艺集成方案中TSV、有源器件片内互连的工艺顺序,TSV 封装工艺可以分为 Via First、Via Middle、Via Last 三种工艺方案。Via First 是指先完成 TSV的制作,再做有源芯片及其互连;Via Middle 是指先做有源器件,然后制作ISV,之后再进行片内互连工艺;Via Last 是指先完成有源芯片和有源芯片片内互连层,最后制作TSV。 Via Middle 和 Via Last 工艺是目前应用较广泛的 TSV 解决方案。

目前,TSV 主要有三大应用领域,分别是三维集成电路(3D 1C)封装、维圆片级芯片尺寸封装(3D WLCSP)和2.5D 中介转接层(Interposer)封裝。

(1)3D1C封装:目前,3D IC 的应用方向主要是存储类产品,其原因是存储类产品引脚密度小,版图布局规律,芯片功率密度小等。通过 TSV 通孔实现三维集成,可以增加存储容量,降低功耗,增加带宽,减小延迟,实现小型化。

(2)3D WICSP: 主要应用于图像 指纹、滤波器、加速度计等传感器封装领域。其特点是采用 Via Last 工艺,TSV 深宽比较小(1:1~3:1),孔径较大。出于对成本的考虑,目前图像传感器封装大多采取低深宽比的 TSV 结构。

(3) 2.5D 中介转接层封装:细线条布线中介转接层针对的是 FPCA、CPU等高性能的应用,其特征是正面有多层细节距再布线层和细节距微凸点,主流ISV 深宽比达到 10:1,厚度约为 100wm。由于受技术难点和成本的限制,以及封装厚度增加等问题,目前2.5D 中介转按层处于小批量生产阶段。

硅通孔最大的敌人,寄生电容

硅通孔对于带宽的影响很大,尤其是寄生电容很大,导致RC常数很大,带宽降低,需要各种小心避免。

换句话说,硅不做“通”孔,就没有这些麻烦。

换第二句话说,PCB做“通”孔,也没有这些麻烦

换第三句话说,LTCC低温共烧陶瓷的多层布线做“通”孔,也没有这些麻烦

今天略聊一下,硅的“通”孔戳了啥马蜂窝

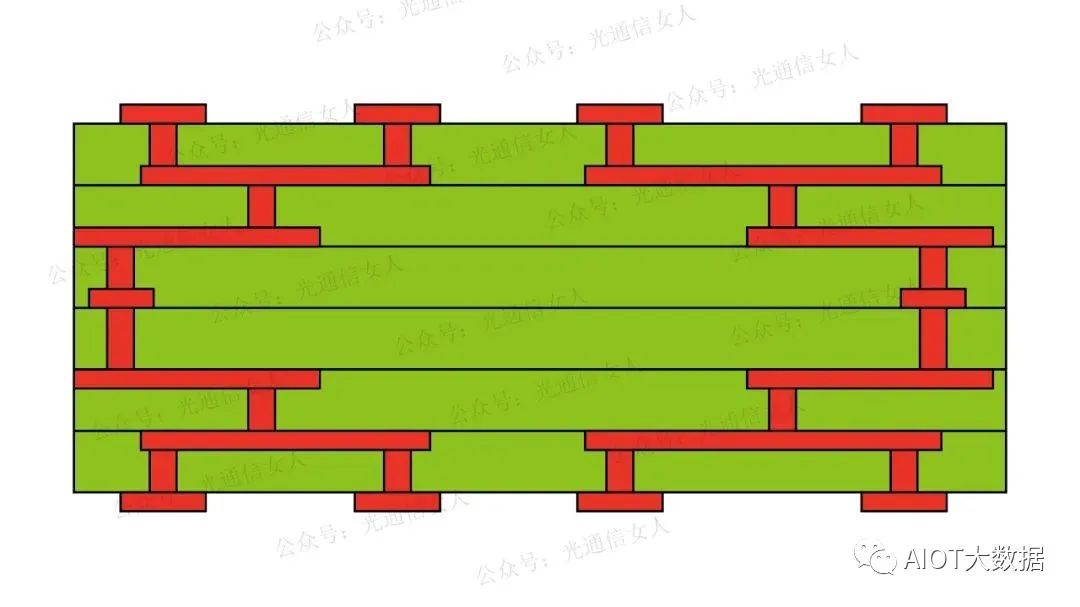

见过硅光工艺的布线吧,很多家工艺有单层的多层的,在绿色的氧化硅层纵向打孔,横向走线,可以起到互联作用。

层和层之间有氮化硅层

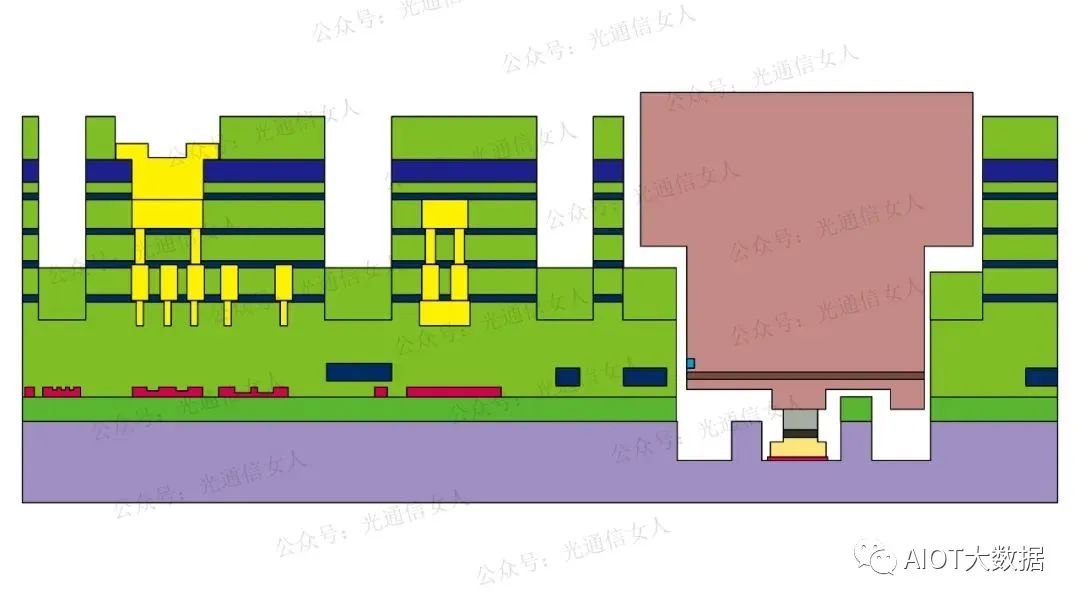

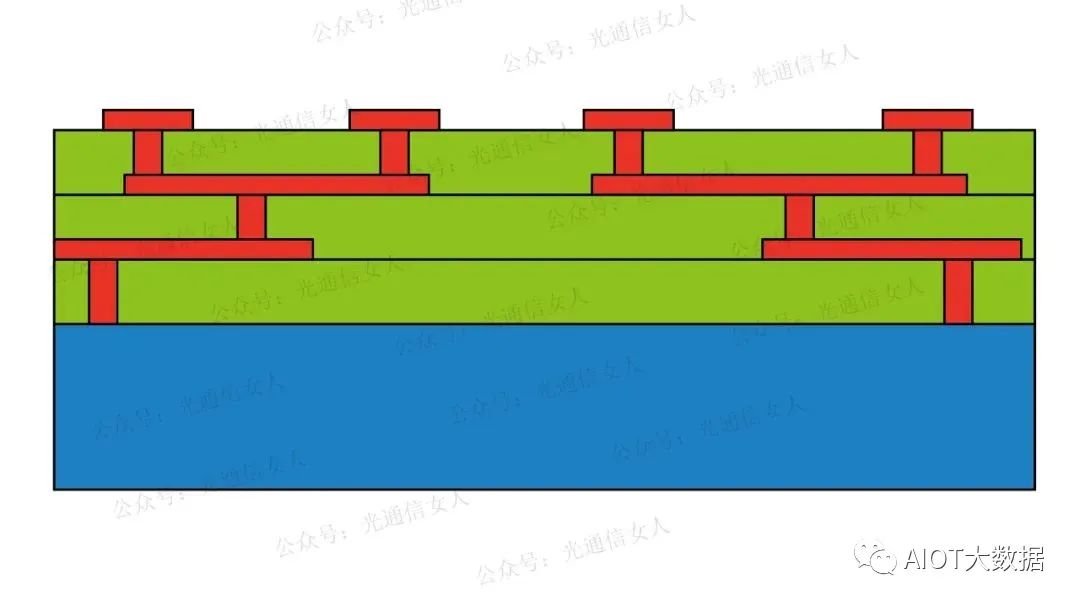

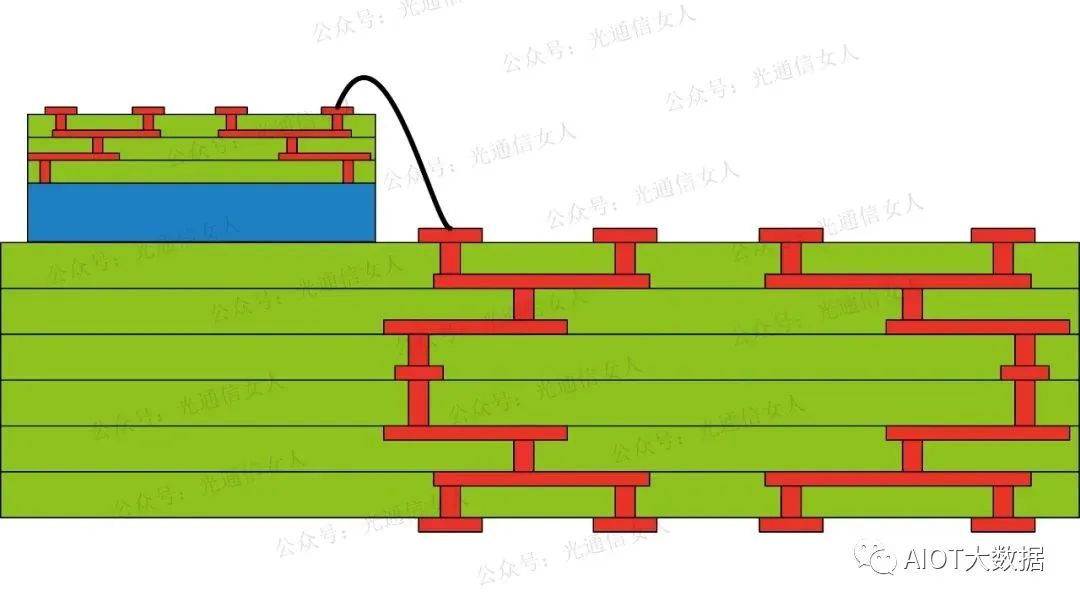

下图是IMEC的不包括硅通孔的硅光工艺

也写过基于硅通孔的工艺细节,用于各种热插拔和CPO的高密度封装。我个人习惯用绿色来表示氧化硅,粉色表示硅。

下图是Marvell的基于硅通孔的硅光芯片/光纤/激光器/DRV/TIA的组装结构。

从这些结构看不出来,硅通孔与非通孔有啥本质区别。我换个角度来聊。

只分三类材料,

第一类:导电的材料,都用橙色表示,比如PCB板中的铜、镍、金,比如集成电路中的钨、钛、镍、铂、金、铝、铜..., 总之,他们的目的是用来做“导体”路径的。

第二类:绝缘的材料,都用绿色表示,比如PCB板中的玻璃纤维、树脂等,比如集成电路中的氧化硅、氮化硅等,比如LTCC中的陶瓷..., 他们的目的是用来做“隔离”的,让各个导体之间不会短路。

有了导体和绝缘体,就可以做多层布线了,传统的PCB比较便宜,LTCC的多层陶瓷性能比较好,但也比较贵,等等。这些的核心性能是一致的,该导电的导电,不导电的就做好隔离工作。

PCB和LTCC做通孔,就不难。因为他们只有两大类材料,导电的材料和不导电的材料。

第三类材料,半导体材料(这里我把半绝缘材料也笼统的包进来,先不做细分)。半导体,就是半导电的固体材料,比如硅,这些材料有啥作用?

掺杂后形成P型半导体,N型半导体,PN之间,正向导通反向截止,这啥意思呢,正向偏压的时候看着像“导体”,反向偏压的时候看着像“绝缘体”,这就打开了另一个世界的通道,可控,听话,我们的信号就有了“开关”两个状态了,是吧。

P型半导体和N型半导体再复杂一些,就可以是NPN、PNP等双极性“开关”,就可以是NMOS、PMOS、CMOS等场控效应的“开关”,比如DSP就是很典型的半导体集成“电路”

利用PN还可以控制光学信号,比如PN半导体中,正偏压、反偏压,来控制光学折射率,做激光器、探测器、调制器、滤波器、谐振腔....等等,如果用硅这种半导体来控制光学,就是咱常听到硅光集成,也就是半导体集成“光路”

我们天蓝色来表示半导体,当半导体集成电路或者集成光路,制作万功能后,剩下的就是做多层互联,这时候不需要半导体再次表现出“正向反向”啥的变化,对于后期的信号线的布局,只需要该导电就导电,不导电就绝缘。

一般在顶层做线路互联时,导电的材料是金属(铜、铝、钨等),绝缘的材料是氧化硅和氮化硅。一层层向晶圆的顶层引出就行。

传统的集成电路和集成光路的布线层在顶面的几层

如果要把硅光芯片和PCB/LTCC的多层布线连在一起呢,也有三种形式,

一是“引线”键合,这种工艺用的最多了,有些引线,咱做光模块的能看到,比如COB工艺。有些引线咱看不到,是因为这些引线被封装起来了。

二是Flip Chip,倒装焊,把芯片翻个面,引线的部分就和我们的PCB/LTCC焊在一起。同样的,Flip Chip的结构,在光模块的封装工艺中,有些是可以看到的,有些看不到,芯片倒装焊在一个基板后封装好了再卖给我们的,我们只需拿来做SMT的贴装就行。

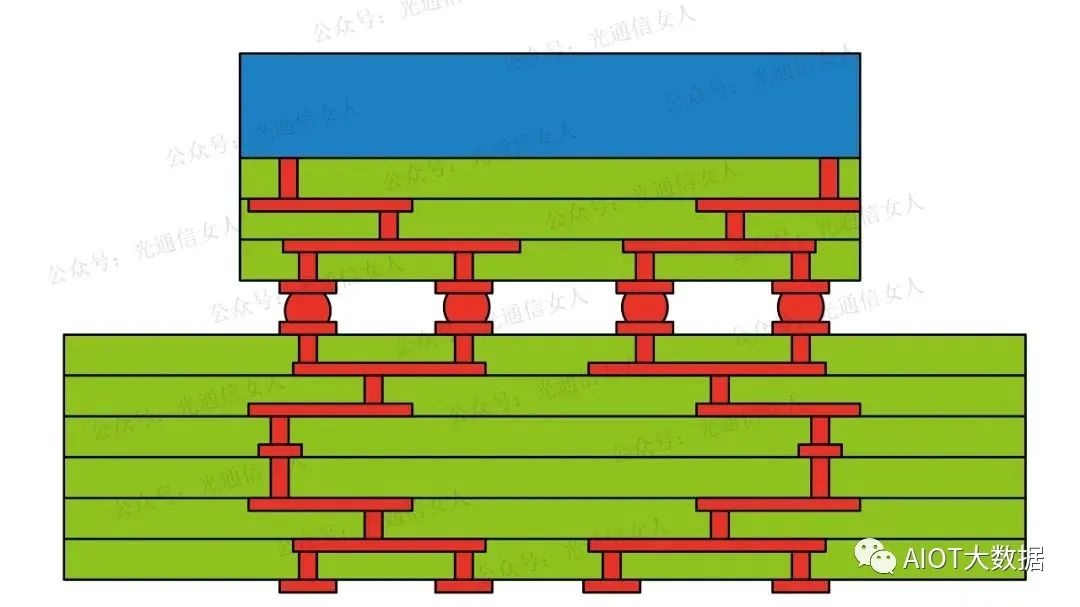

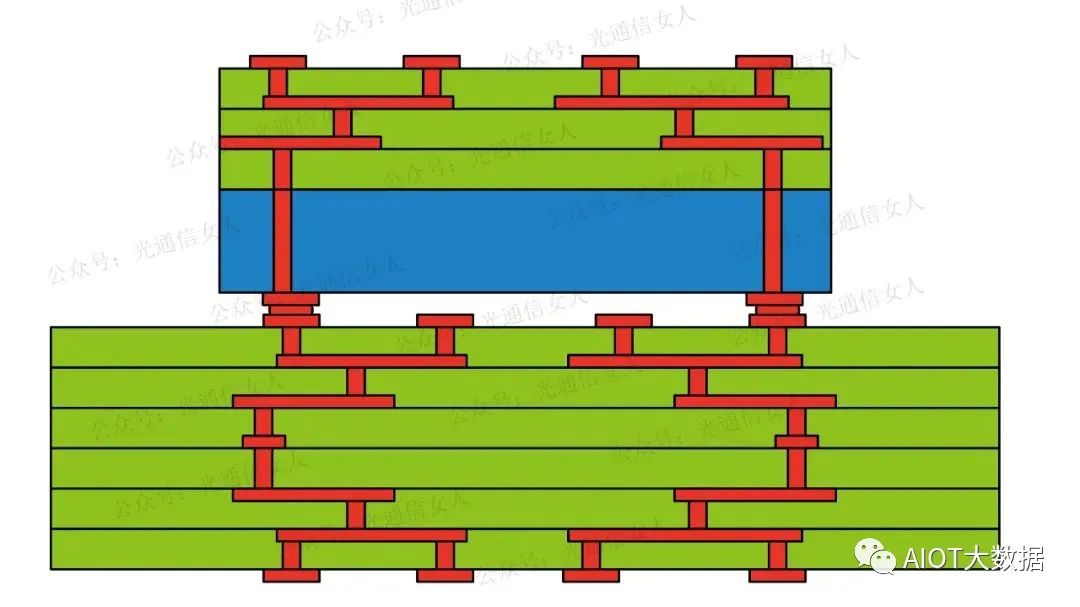

三,就是硅通孔,既不像第一种用外部金丝,也不像第二种反面。而是直接把蓝色区域穿个孔,把导电引过来。

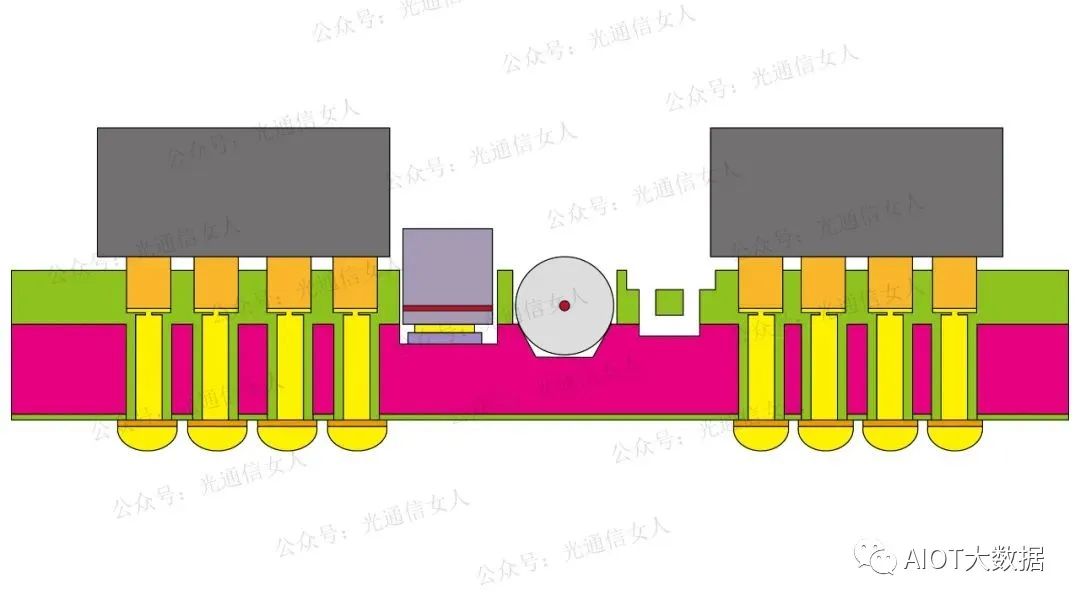

戳了马蜂窝的,就是金属线穿过蓝色的“半导”电的区域。

我们非常习惯的是导体在绝缘体中穿过来又穿过去,虽然导体有好的不好的各种优缺点,绝缘体材料也是各种优缺点,总的来说,信号的绝大部分是在导体中传送的。

但如果导体布线,并且直接在半导体中穿过来穿过去,就要了亲命了,直接连不行,半导体虽然不是很导电,但也是半导,信号的很大一部分能量就被半导体给消耗了,这压根就不能用。

下图左边,就是我们常见的什么PCB板、陶瓷板、玻璃基板、集成电路/光路的上半部分的结构,导体穿越的是绝缘体。这是可行的。

下图右侧,如果导体作为互联的信号线而言,直接穿越半导体,是不行的。

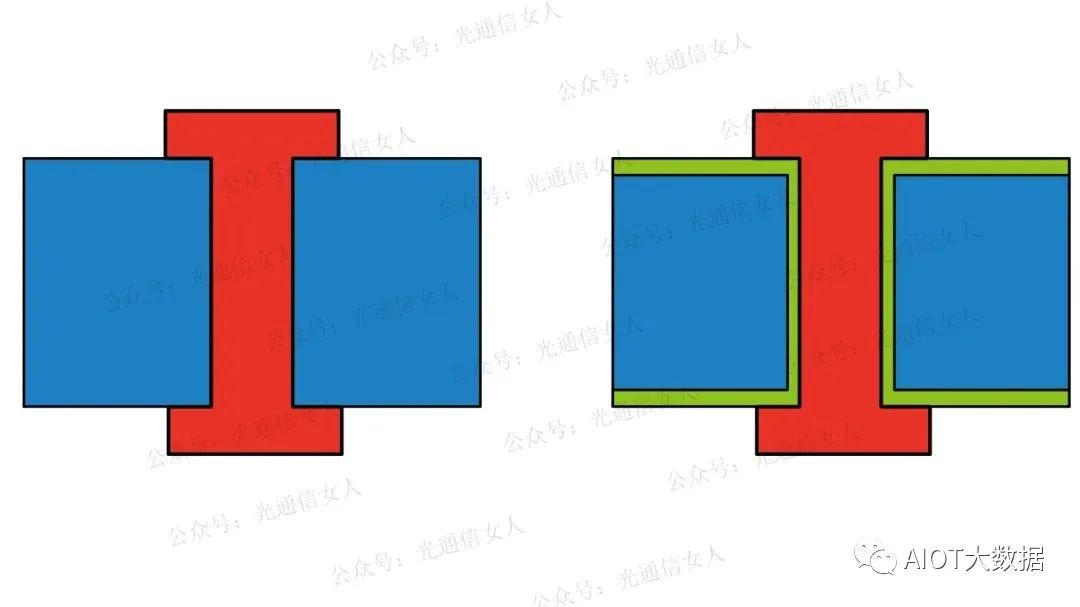

一个变通的方法,就是在半导体中打个孔,然后涂覆一层绝缘体,用绝缘体把导体和半导体隔离开,这总行了吧。嗯,这行

这就是硅要把下半部分打穿,形成“通”孔,常见的工艺,在硅这个半导体材料上,先氧化一下,形成薄薄的一层氧化硅绝缘体,里边再填注各种金属做导线。

马蜂窝,就是这个蓝/绿/橙三色叠加体,其他地方看不到的奇观,蓝是半导体硅,绿是氧化硅绝缘体,橙是金属导体

半导体-氧化硅-金属,这是个电容

这个电容导致带宽不足。

最后呼应一下前头换的那三句话。

换句话说,硅不做“通”孔,就没有这些麻烦,键合丝工艺或者Flip Chip工艺,都无需在半导体中穿孔,不会额外增加个大电容。

换第二句话说,PCB做“通”孔,也没有这些麻烦,因为PCB只做互联,就两类材料,导电的和不导电的,有寄生电容也很小,不是这种半导体-绝缘体-导体所寄生的大电容。

换第三句话说,LTCC低温共烧陶瓷的多层布线做“通”孔,也没有这些麻烦,理由与第二句话一样,陶瓷是绝缘体。

审核编辑:刘清

-

晶圆

+关注

关注

53文章

5348浏览量

131703 -

半导体封装

+关注

关注

4文章

312浏览量

15131 -

WLCSP封装

+关注

关注

2文章

10浏览量

16460 -

硅通孔

+关注

关注

2文章

28浏览量

12087 -

HBM

+关注

关注

2文章

426浏览量

15700

原文标题:技术前沿:HBM的关键工艺——硅通孔的能与不能

文章出处:【微信号:AIOT大数据,微信公众号:AIOT大数据】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

硅通孔封装工艺流程与技术

简单介绍硅通孔(TSV)封装工艺

一文详解硅通孔技术(TSV)

3D IC集成与硅通孔TSV互连

3D封装与硅通孔(TSV)工艺技术

详解TSV(硅通孔技术)封装技术

HBM的关键工艺—硅通孔的能与不能

HBM的关键工艺—硅通孔的能与不能

评论