本文将介绍Vivado Non-Project模式几个常见问题及解决方法。

问题1:如何读入IP?

问题2:如果IP已经采用OOC综合那么是否可以将其修改为Global综合方式?

问题3:如何对IP执行OOC综合?

问题4:如何对用户模块执行OOC综合并将其集成到整个设计流程中?

相比于Project模式,Vivado Non-Project模式可以提供用户更多的控制权,进而用户可以自主管理整个编译流程,可以根据需要选择是否生成相应的dcp文件或者相关报告。但也面临一个问题就是需要借助Tcl脚本,同时所用到的Tcl命令和Project模式有很大不同且两者不可混用。

问题1:Non-Project模式下如何导入IP,是用read_ip还是import_ip?

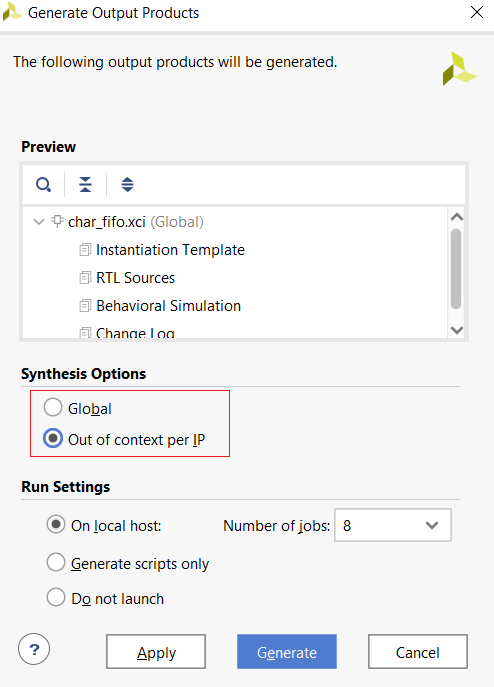

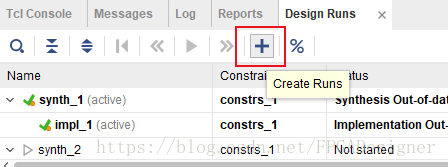

我们知道对于Vivado IP Catalog中的IP,只能采用Vivado进行综合。Vivado提供了两种综合方式:Global和Out-of-context(OOC),如下图所示。其中OOC模式就是单独对IP进行综合生成相应的dcp文件。

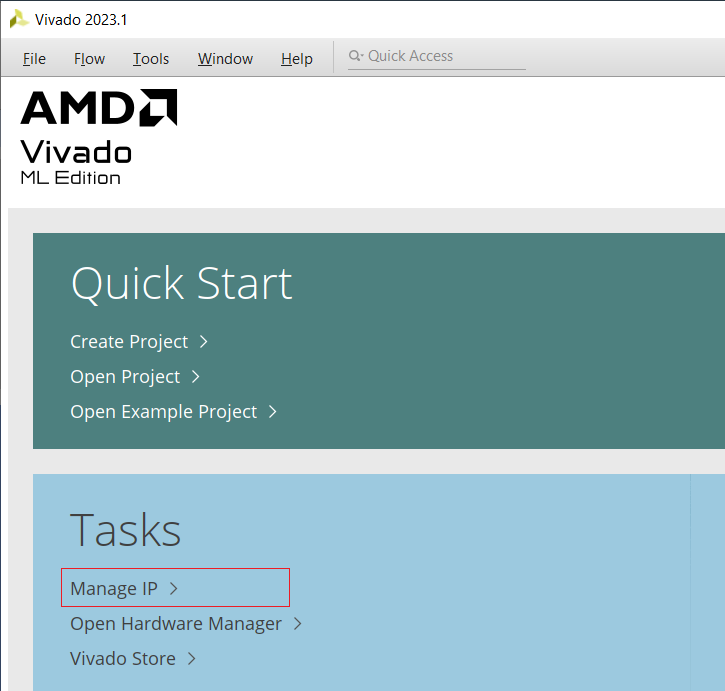

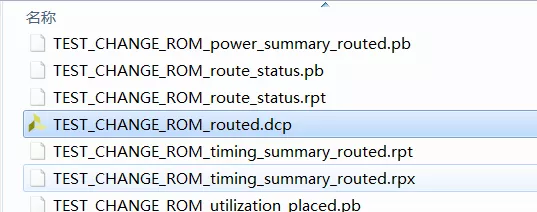

对于设计中用到的IP,建议采用VivadoManage IP创建IP工程,单独对IP进行管理,如下图所示。

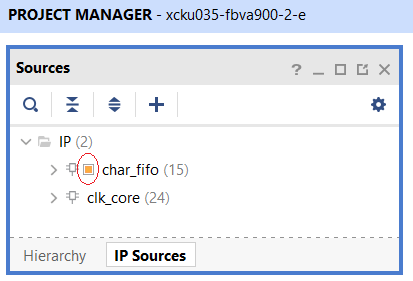

创建IP工程后即可定制IP,如下图所示,定制了两个IP:char_fifo和clk_core。其中前者采用OOC综合方式,可以看到其图标处有一个橙色方块。后者为Global综合方式。通常情况下,建议对IP采用OOC综合方式并在IP工程中完成对IP的单独综合。

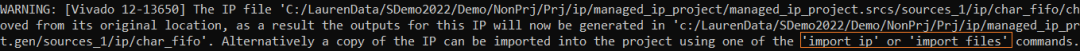

这种情况下Non-Project模式读入IP时需要用命令read_ip,而不是import_ip,即使会报告如下图所示警告(忽略该警告,尽管这个警告是建议使用import_ip,但import_ip是在Project模式时使用的)。

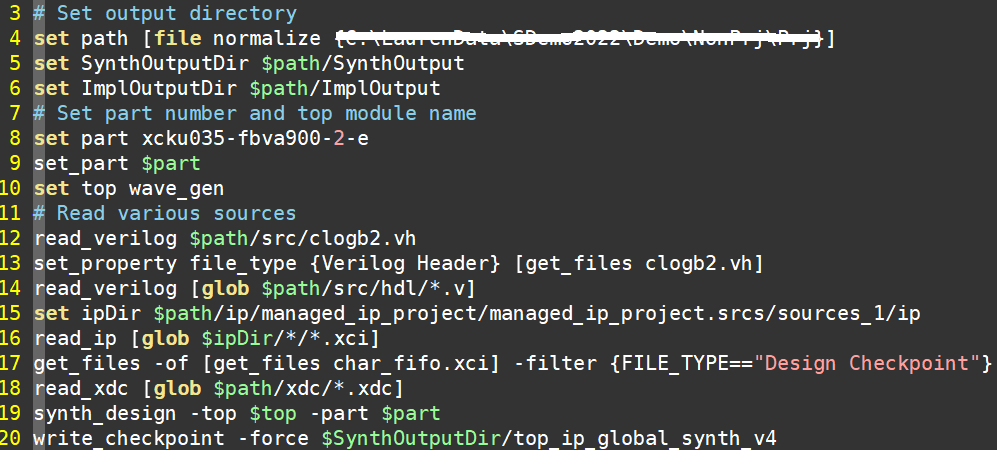

实际上read_ip读入的不只是.xci文件,已经完成OOC综合所产生的所有输出文件都会被读入,包括dcp文件,因此这种情况下并不需要再次对IP综合,而是可以直接进行顶层设计的综合,相应脚本如下图所示。

其中代码第9行set_part命令用于指定当前工程用到的具体芯片型号,代码第17行用于验证read_ip读入的文件包括IP对应的dcp文件。

问题2:如果IP已经采用OOC综合那么是否可以将其修改为Global综合方式?

审核编辑:刘清

-

fifo

+关注

关注

3文章

407浏览量

45895 -

CLK

+关注

关注

0文章

132浏览量

18095 -

Vivado

+关注

关注

19文章

860浏览量

71388 -

OOC

+关注

关注

0文章

4浏览量

4963

原文标题:Vivado Non-Project模式几个常见问题

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

开源RISC-V处理器(蜂鸟E203)学习(二)修改FPGA综合环境(移植到自己的Xilinx FPGA板卡)

GSM给您解释解释XILINX XST综合的选项的含义(完成)

浅谈IC设计中逻辑综合

verilog可综合与不可综合-学习一下

verilog 循环以及@(clock)的综合

xilinx EDF已经综合过的网表文件怎样添加到Vivado工程中?

Linux Vivado怎么实现一次运行四个或更多OOC模块 ?

如何从综合中排除特定的OOC模块?

关于高阻态和OOC(out of context)综合方式

修改BRAM初始化值的避免综合与实现

Vivado使用技巧分享:OOC综合技术运行流程

如果IP已经采用OOC综合那么是否可以将其修改为Global综合方式?

如果IP已经采用OOC综合那么是否可以将其修改为Global综合方式?

评论