1. LC-VCO起振条件及振荡频率的计算

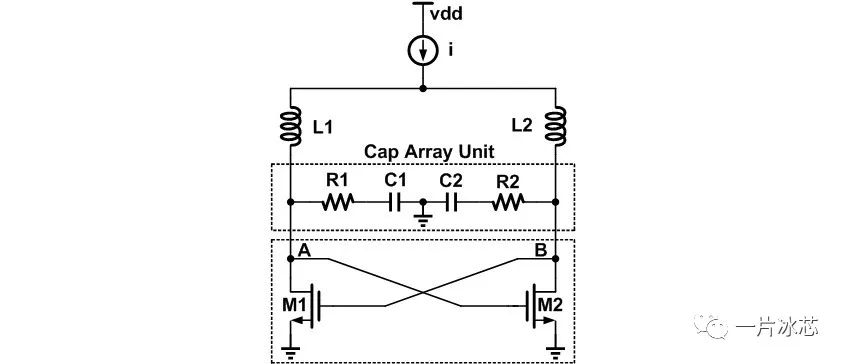

LC-VCO的等效电路如图1所示,实际应用中L1和L2由带中间抽头的对称电感组成,抽头接电流源(图中i)。

为减小Rj,vdd通常由LDO供电。电流源可由PMOS管实现,也可由电阻实现,两者在工程中都有应用,差异主要是低中频的闪烁噪声和热噪声及电流是否固定,具体差异以后有机会再跟大家分享。

R1、R2、C1、C2组成LC-VCO的电容阵列,其中R1、R2为MOS管的导通或关断电阻,C1、C2通常为MOM电容,电容阵列(图中Cap Array Unit)通常带有二进制权重(如1:2:4:8:16)。

交差耦合管M1、M2形成负阻用于抵消LC振荡环中的寄生电阻,以维持等幅振荡。为了简化分析图1中没有画出varactor电容,varactor电容用于调整VCO的输出频率。

Fig1. LC-VCO等效电路

可通过计算或前面阻抗变换中介绍的sp仿真得到电容阵列的等效并联电阻Rpc及并联电容Cpc。图1中电感为理想电感,感值为L1+L2,如果为非理想电感可通过电感的S参数模型仿真出等效电感、电容、电阻,为了便于分析这里简化成了理想电感。

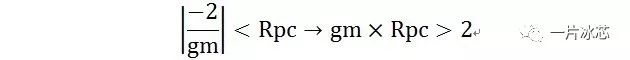

通过画小信号可得,A、B两点向下看进去的等效并联阻抗为Rpm=-2/gm,(gm1=gm2=gm),A、B两点向下看进去的等效并联电容为Cpm。为了维持振荡,有下式成立:

其中gm为M1或M2的跨导,Rpc为电容阵列的等效并联电阻(工程中还要与电感和varactor电容的等效并联电阻进行并联)。

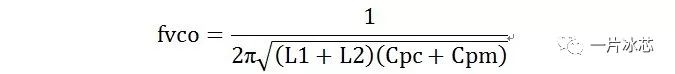

在满足上述起振条件的前提下,振荡频率有如下表达式:

Rpc、Rpm及gm只影响起振及振荡幅度,振荡频率只取决于L1、L2、Cpc、Cpm。

**2. **仿真验证

在T28工艺下搭建图1所示的等效电路模型,其中M1和M2管选用tsmcN28工艺库中的nch_hvt_mac器件,尺寸为48um/30nm。其余全部调用analogLib中的理想器件,L1=L2=200pH,C1=C2=800fF,i=3mA,vdd=1V。

图1中的R1、R2从1 Ohm逐渐增大,sp仿真发现电容阵列的等效Rpc不断减小,当R1=R2=5.7 Ohm时,Rpc=108 Ohm,Cpc=300fF,此时振荡器刚好处于临界振荡状态,gm=20.95ms,Cpm=70fF。

用第1章给出起振条件公式计算出gm x Rpc = 20.95 ms x 108 Ohm = 2.26 >2。

用第1章给出振荡频率公式计算出fvco = 1.3GHz,仿真结果约为12.5GHz。

注:仿真交叉耦合管M1和M2的等效并联电阻及电容时,应给A、B两点合理的共模电压,因为共模电压会影响并联阻抗;如果A、B两点振荡幅度较大,使得M1和M2管处于大信号状态小信号sp仿真将不再适用,应采用pss+psp进行大信号仿真。

-

振荡器

+关注

关注

28文章

4158浏览量

142358 -

MOS管

+关注

关注

110文章

2754浏览量

75063 -

VCO

+关注

关注

14文章

314浏览量

71104 -

等效电路

+关注

关注

6文章

296浏览量

33730 -

寄生电阻

+关注

关注

1文章

23浏览量

2503

发布评论请先 登录

请问一下spectre19或spectre20做长时间仿真时出现error停止该如何解决?

Cadence仿真VCO始终不出合理的振荡波形的原因?怎么解决?

Cadence IC617的Spectre下gm/ID曲线的仿真怎么设置?

如何利用SMIC55nm工艺设计VCO版图?

请问在spectre仿真器中怎么去使用spice模型?

TSMC350nm的工艺库是不是不太适合做LC-VCO啊?

请大神指点为什么spectre不能连续进行仿真?

PA、LNA、Mixer、VCO等射频模块的指标仿真方法以及实例工程文件

如何对Spectre下的LC-VCO进行仿真验证?

如何对Spectre下的LC-VCO进行仿真验证?

评论