我使用的是HVACI_sensorless_2833x的例程,它是使用IQ格式写的,其实controlsuite里面大多数的例程都是用这个格式来做的,因为它有两个优势,首先运行速度快,使用于定点芯片,另一个是可移植性强。

但是我使用的是28335的板子,它是一款浮点计算为主的板子,我忽略了它的主要优势,一直在跟IQ格式的使用较劲,虽然28335也支持定点格式,但是真正使用起来,却远远不像浮点型那么方便,IQ格式需要你去估计参与计算的变量的数值大小,保证不会溢出,使用这个格式会多花费你一般的时间;我原本只是用来产生SVPWM波形,这个理论看了好几遍,还是不太懂得,但要复述原理也能说得差不多,从这个例程里面,直接利用build1进行调节,就可以调出来马鞍波。参考文件可以看这个例程里面的doc文件,这样就可以解决第一步问题;

二、加锁相环SRF-SPLL

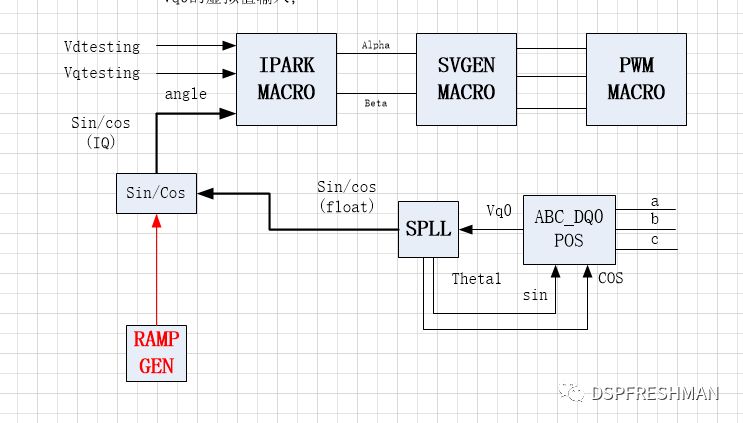

首先给出一张结构图,我的想法大概是这样的,实际操作之后证明是可行的;

由三相电压进入,经过变换,然后把Vq值给到数字锁相环,锁相环产生sin/cos数值,给到ipark的输入angle,然后经过SVGEN产生占空比,得到马鞍波,红色部分是用例程中程序直接调试的到的,黑色部分是我这一个月调试的过程,其中大部分时间都用来研究IQ格式了,现在还有好多不是太明白的地方,当然如果你也有遇到,可以跟我及时交流;这里面注意两种格式变换的地方是在angle那里,由浮点变为定点,然后使用graph功能(初学的话这里也是一个会花费功夫的地方)来进行观测;

三、注意的问题以及解决方法

我使用的SRF-SPLL是从TI论坛里面找到的参考程序

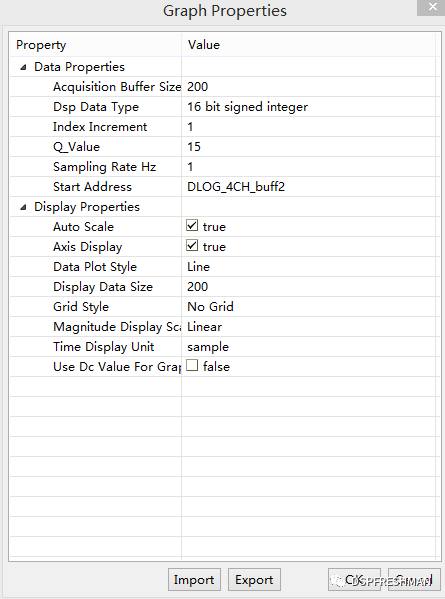

还有一个就是Graph功能的设置,下面给出一个基于本例程的正确的设置方法,如下图所示:

当然,这只是帮助你少去走一些弯路,实际调试可能还会遇到很多问题;

还有一定,就是SPLL调用的文件,在初始化的时候,1/ISRfrequency是指的工程的采样周期,不要真的把后面的值代入就完了。

-

锁相环

+关注

关注

36文章

637浏览量

91302 -

数字锁相环

+关注

关注

3文章

36浏览量

13844 -

SVPWM

+关注

关注

15文章

616浏览量

92616 -

三相电压

+关注

关注

0文章

104浏览量

15482 -

SPLL

+关注

关注

0文章

3浏览量

9343

发布评论请先 登录

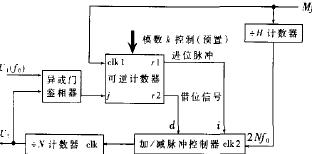

数字锁相环设计步骤

CCS6.2 Graph图像功能显示的数值相差很多的原因?

智能全数字锁相环的设计

数字锁相环(DPLL),数字锁相环(DPLL)是什么?

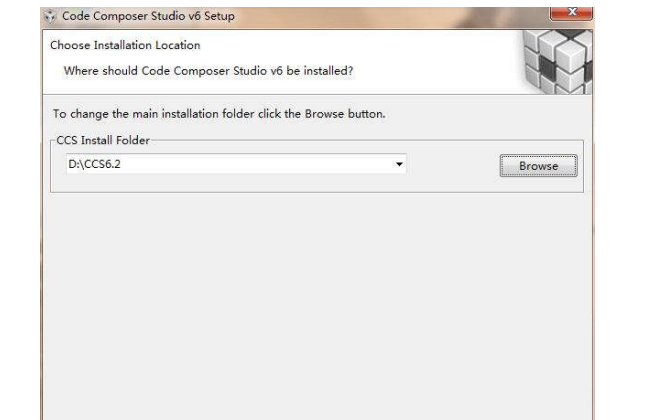

CCS6.2的详细使用方法说明

如何在CCS6.2中调试SRF数字锁相环?

如何在CCS6.2中调试SRF数字锁相环?

评论