今天看了一篇很有意思的文章《Utilizing Fine Line PCBs with High Density BGAs》,讲的是PCB BGA高密度fanout带来的阻抗不连续。考虑到基板层叠设计以及基板加工工艺的约束带来的基板阻抗设计偏差,也可以应用上这种评估方法。总结一下我从这篇文章get到的关键点:

1、PCB加工量产工艺已经可以做到线宽最小15um,同样这家美国公司的基板已经在研发5um的线宽、间距。(这直接吊打国内众多封装基板厂商,任重而道远啊)

来祸祸一下大家的眼睛,这是PCB BGA区域的fanout。是的,你没看错,两个0.8mm pitch BGA PAD之间穿了7根20um线宽的单线。

2、在不明确整个系统的情况下,可以通过一种简单的方法,粗略评估链路阻抗不连续的影响风险,得到一个大致约束范围。

那么来重点讲讲Eric Bogatin大佬的这个评估方法。首先这个评估方法是仅能提供一个指导性的方向,不能作为sign-off的标准要求。

既然要进行评估,那就需要一个判定要求。Eric大佬认为-10dB的回损可以作为一个判定边界,这个值是由以下推导得来。

在理想无损的系统中,输入的能量等于传输通过的能量与反射能量之和。这是满足能量守恒定律的。也就是在一个二端口系统中,传输通过的增益S21与反射系数S11的平方和等于1。

(全频段f均满足此公式)

(全频段f均满足此公式)

根据这个公式可以得到下图。

从图中可以看出来,在回损-20dB以下时,插损的变化非常小(小于0.1dB),可以忽略不计。当回损达到-10dB时,插损影响大概为-0.5dB。

Eric认为,局部区域回损恶化-10dB,才会对RX端插损恶化-0.5dB,且这个是可以接受的。(当然这个应该根据每个设计自行选择判断,若插损裕量足够大的情况下可以进一步放开。)

由此,我们可以得到一个回损的边界:-10dB。

接来下我们分析,阻抗不连续的两个主要影响因素主要是设计阻抗与目标阻抗的偏差和阻抗不连续长度。针对这两个因素分别来进行控制变量分析。

1、阻抗偏差最大可以做到多少?

2、阻抗不连续长度最大可以做到多少?

来解决第一个问题。我们也采用回损-10dB这个作为判定边界。按照正常走线50ohm,前端阻抗不匹配来进行仿真。

小P开始整活儿,搭建了这么一个简单的仿真链路。第一段传输线做阻抗不匹配,其中阻抗从30ohm扫描到80ohm。阻抗不匹配的长度先按短的走线来看,8mm(315mil)。

回损的仿真结果如下图,在0~3GHz都满足小于-10dB。那么说明,如果我们的信号奈奎斯特率在3GHz以内,30ohm和80ohm的阻抗偏差,在300mil长度的走线上,是可以接收的。

我们在同样的这个阻抗范围内,把阻抗不匹配的走线加长到50mm(约2inch),得到的回损结果如下图,回损在1GHz附近达到了最大值-6dB。可见在同等条件下,不匹配阻抗线的长度还是影响着我们的带宽。

那么第一个问题的答案就跃然而出了,设计者可以根据自己的插损裕量,信号的带宽要求,仿真得出此局部区域阻抗偏差的范围。

我们接着来看第二个问题,我们发现不匹配阻抗线加长以后,回损出现了一个最大值。回损的最大值可以通过公式算出:

(全频段f均满足此公式)

(全频段f均满足此公式)

Z-dB(S11)的曲线如下图,可以知道在回损最大值小于-10dB的阻抗范围是36.3~68.8ohm。

修改链路,阻抗不匹配段的阻抗设置为36.3ohm,走线长度从5mm80mm(2003200mil)。

由仿真结果可以看出,回损最大值没有超过-10dB。

第二个问题的答案也浮现出来了。如果可以找到回损最大值对应的阻抗,那么阻抗不匹配的走线长度增加不会导致回损的最大值变大。

前面的这些,其实全在Eric大佬的文章中做了,同时其文中也提到差分走线与单端走线在这个特性上的表现是一致的。

那小P在这里就基于90ohm差分线也做一下仿真模拟。

类似单端信号的做法,搭建仿真链路。端口的端接设置为单端45ohm,导体电导率设置为1E50,介质损耗角设置为0,模拟无损链路。

先设置阻抗不匹配段走线长度为7.6mm(约300mil),扫描得到的回损仿真结果如下图。仍然按3GHz来卡-10dB的要求。也就是带宽在3GHz以内的信号,阻抗可以300mil长度的差分阻抗可接受范围是60~135ohm。

若是以回损的最大值来换取任意长度的阻抗不连续链路,则由下图可以得到当差分阻抗在65.4~123.8ohm之间。

基于这个阻抗范围,阻抗不连续长度从仿真得到的回损波形如下图,可见是符合预期的。

前面全部是基于理想的无损传输线进行的仿真,我们再对比一下有损传输线和无损传输线的情况。毕竟实际评估的链路肯定都是有损的。

下图是90ohm差分,不连续阻抗65ohm,不连续长度1inch的有损/无损插回损对比。

可见回损的是比较一致的。因此前面的结论也适用于有损传输线链路。

小P这里再拿芯片封装来举个实例:

假定我们有一颗封装尺寸是25x25mm的ETH接口芯片。基板采用buildup层叠设计。若采用GZ41(DK=3.3@1GHz)作为介质,buildup层一般则是30um厚度,铜箔厚度约15um。再考虑基板厂加工能力(25um为国内基板厂能力,大陆外高端厂可以做到15um)。因此,基板封装阻抗一般控制在90ohm以下。

由于基板工艺以及基板材料的限定,高速链路的走线层的层叠一般是如下图。

| LAYE | THICKNESS | PLAN | SINGLE | DIFFERENTIAL |

|---|---|---|---|---|

| COPPER | 15um | PWR/GND | / | / |

| BUILDUP | 30um | |||

| COPPER | 15um | SIGNAL | 25um:46ohm20um:50ohm | 25/25um:73ohm25/50um:85ohm25/79um:90ohm20/100um:100ohm |

| BUILDUP | 30um | |||

| COPPER | 15um | PWR/GND | / | / |

注:小于25um的线宽设计不选,以扩大基板厂选择范围。

那么假定的这个ETH接口芯片在基板厂的走线长度最大按曼哈顿距离来算也就是23mm,假设我们阻抗分别定义为85/90/100ohm。PCB上的走线长度为3inch 100ohm。分别得到85ohm的最大回损是-15.51dB,90ohm的最大回损是-19.39dB,100ohm的最大回损为-66.48dB。

把插损和回损的曲线画出来,如下图,可以得到对应的插损关系。

| 阻抗 | dB(S11) | dB(S21) |

|---|---|---|

| 85ohm/不匹配 | -15.51 | -0.25 |

| 90ohm/不匹配 | -19.39 | -0.1 |

| 100ohm/匹配 | -66.78 | 0 |

从结果来看,85 or 90ohm 对全链路的插损影响都比较小。当然如果设计上可以满足阻抗匹配,那就是最好的了。

-

阻抗

+关注

关注

17文章

983浏览量

48746 -

封装

+关注

关注

128文章

9139浏览量

147887 -

BGA

+关注

关注

5文章

581浏览量

50944 -

PCB

+关注

关注

1文章

2264浏览量

13204

发布评论请先 登录

如何解决PCB阻抗不连续问题

常用的解耦设计方法

一种基于PID神经网络的解耦控制方法的研究

基于补偿器的解耦控制方法的研究

基于H∞混合灵敏度解耦控制器实现BTT导弹自动驾驶仪的解耦设计

PCB设计阻抗不连续的原因及解决方法

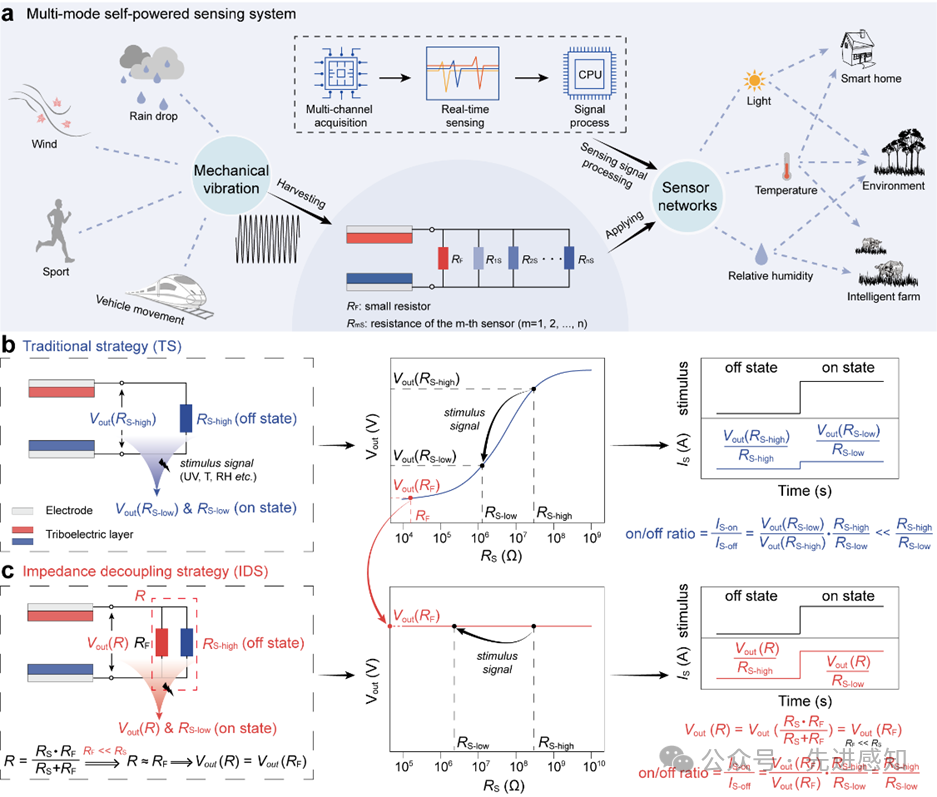

兰州大学:研究阻抗解耦实现高精度自供能多模传感

解耦系统的局部阻抗不连续肤浅风险评估方法

解耦系统的局部阻抗不连续肤浅风险评估方法

评论