背景知识:

Metal fill - DRC/DFM

Layout中对metal/poly/AA和via等有density的要求(window based max density和min density还有其他)。这其中有DRC的部分,也有DFM的部分,前者是必须要满足的,否则在你将GDS交付给Foundary之后也是会被打回来的。而后者是出于良率的考量,对于非商用芯片而言不是很重要,甚至也不用做Check。但是对于商用芯片而言,为了减少废片/降低成本,一般都会在PR阶段做一些优化以及检查。

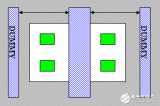

为了满足这些要求,一般都会在Layout里面添加Dummy/metal fill甚至是Track based metal fill。

对Timing的影响

在28nm以及之前的工艺中,Dummy metal对Timing的影响不是很大,因此一般在PR工具中做完布局布线之后导出GDS,然后进行Layout merge,然后用Calibre对Layout添加Dummy即可。此时不考虑Dummy对Timing的影响重新抽RC进行STA也是可以的。当然Star RC也提供了相应的解决方案,可以考虑Dummy metal来抽取RC,保险起见也可以用这种方法来抽RC重新进行STA对Timing进行Signoff。

在28nm之后的工艺甚至先进工艺里面,用这种方法来添加Dummy就不是特别合适了,因为它们对Timing的影响蛮大的,很多时候需要做Timing aware的Dummy insertion。现在的ICC/ICC2可以调用ICV做In-design的metal fill insertion,可以enable timing aware,也可以disable。

这里分享一下用Calibre基于layout merge之后的GDS来添加Dummy(包括metal, via, poly, AA等)的流程。

步骤:

在自己的版图通过了DRC和LVS之后,在Tape out之前,需要依次进行以下操作:

加Seal Ring,检查DRC,当只剩下AA(有源区)间距、密度这种错误后,做第二步(AA间距问题后边可以通过加AA的Dummy来解决,同理,密度问题也是);

用脚本加Dummy,检查DRC、LVS。

如果是数字版图,需要将版图进行合并(Merge),并导出完整的GDS版图,最好将GDS的Cell名和GDS名字一样。打开该版图,在上面加入border层,且border层的左下角为(0,0),右上角与版图重合,因为后边加Dummy就是在该区域内部加的。将该GDS文件与下面所述的dfm文件放到一个目录内,并在该目录下运行以下命令:

calibre -drc -hier xxx.dfm

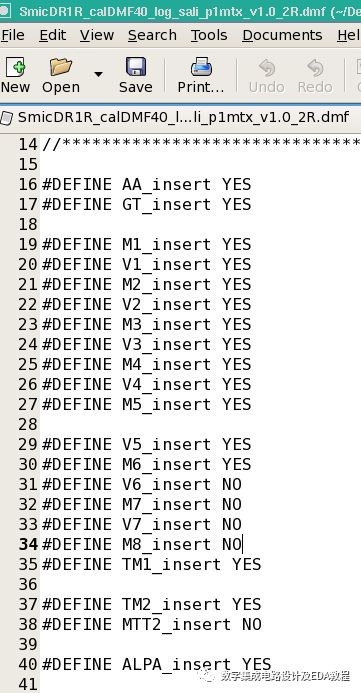

从Foundry官网上下载Calibre加Dummy的dfm文件,如下图所示,进行修改,根据所用工艺层次决定插入那些层次的Dummy。

例如,SMIC 40 nm 1P 8M 2TM工艺,用到的层次如下:

M1 M2 M3 M4 M5 M6 TM1 TM2

V1 V2 V3 V4 V5 TV1 TV2

文件中没有出现的层次说明不用加Dummy,例如(TV1和TV2);且设计中没有用到的层次都设置为NO,例如M7 M8 V6 V7 MTT2

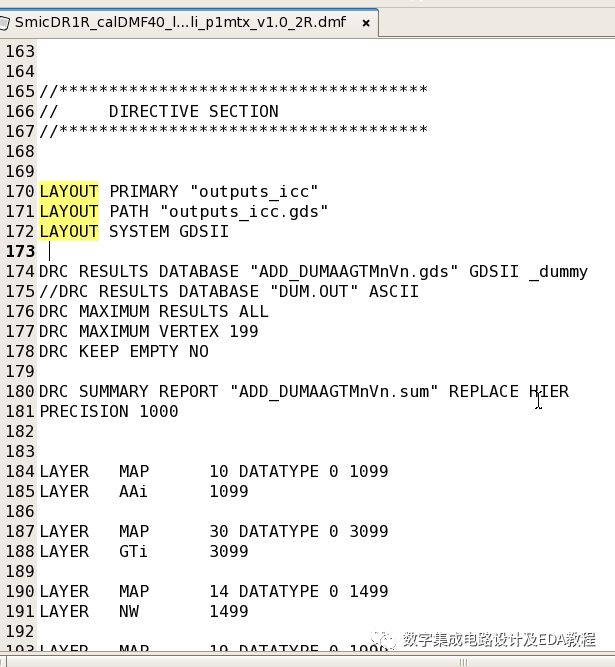

另外一处要修改的地方如右图所示,primary后边填写导出版图top cell的名字,path是gds的名字。

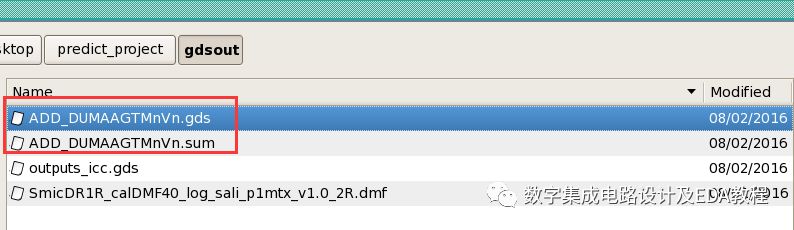

运行该命令后便会在该目录内部生成两个文件,其中一个是dummy的GDS文件。

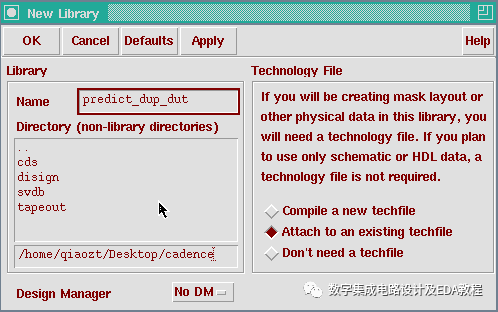

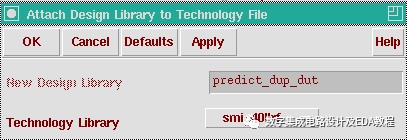

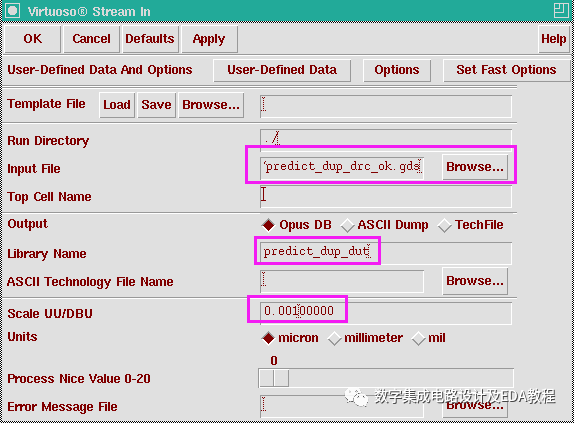

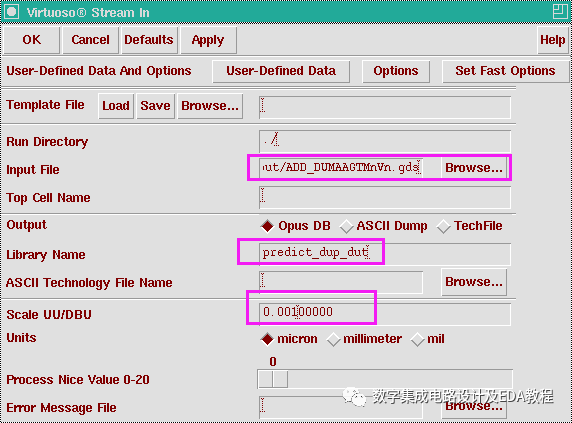

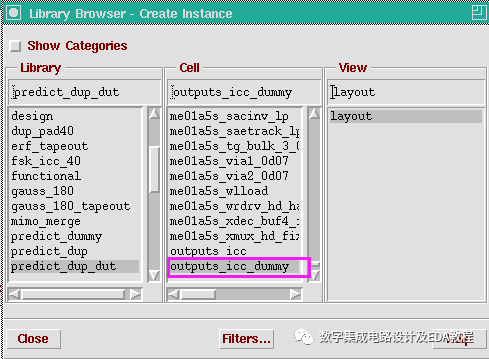

新建一个库,导入之前导出的gds版图以及dummy的版图

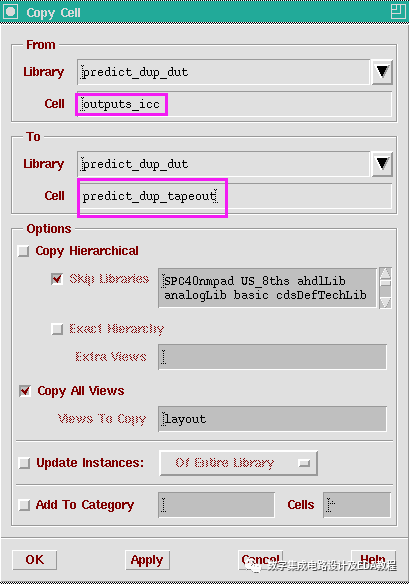

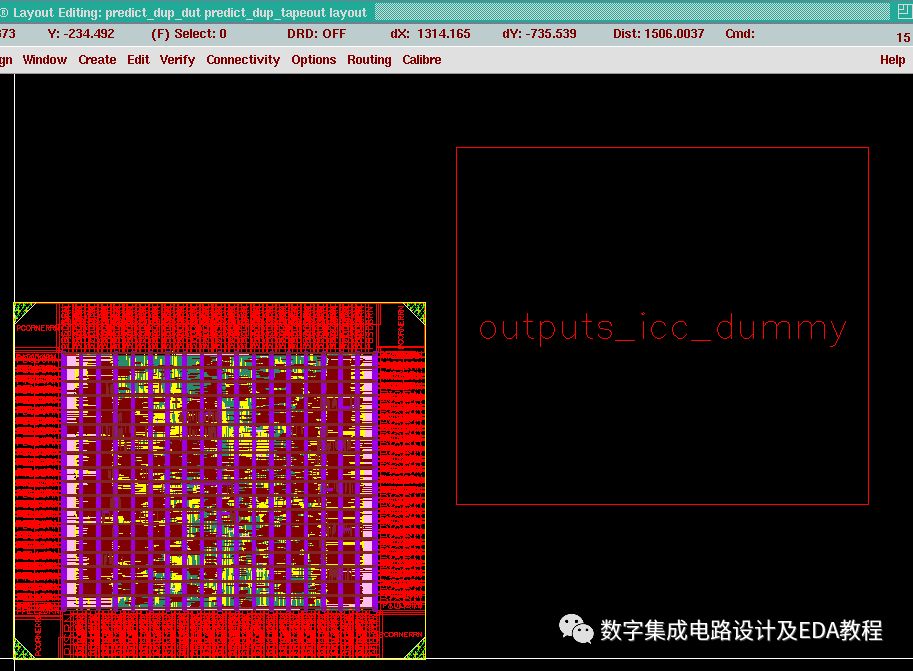

选中顶层Cell进行Copy,然后用instance的方式将dummy加入其中,不要用新建Cell,然后将顶层Cell和dummy都用instance的方式进行例化,因为这样的话进行LVS,会发现软件根本不识别里面在PAD上打的标签,不认为它们是port,会出现很多LVS错误。

同样,也不能将某些SRAM进行flatten,这样会平白无故多出来很多port,同样会出现很多LVS错误。

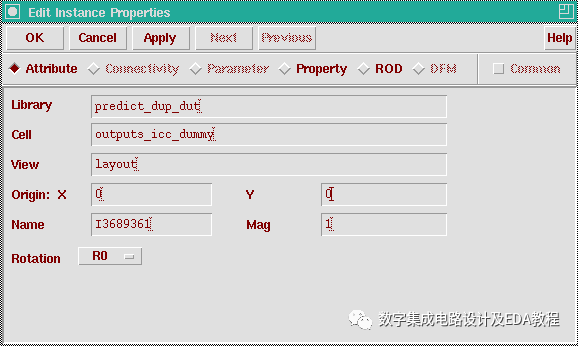

选中那个dummy的instance,点击q,修改属性,将原点坐标均改为(0,0)

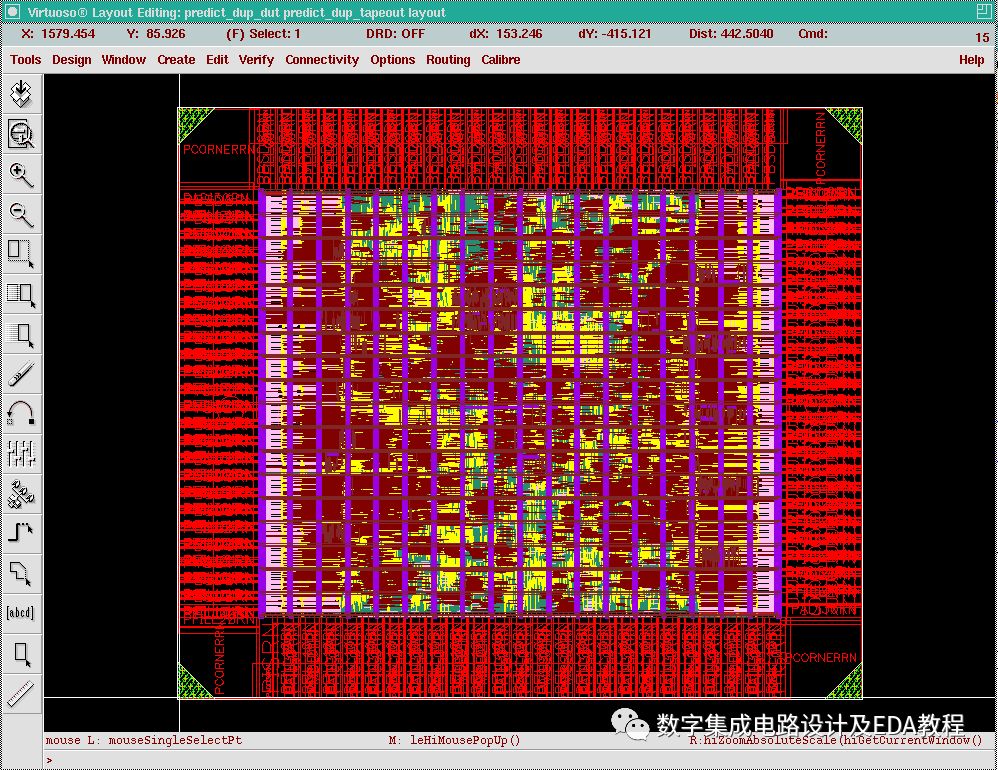

得到下图所示,对于规模很大的Layout,不要显示全部层次,否则会很卡,甚至软件会崩溃,直接用这种状态做DRC,LVS即可。

对于上面这些复杂的操作,其实我们都可以用Makefile和Calibredrv来完成,且非常方便、简单。

审核编辑:刘清

-

存储器

+关注

关注

39文章

7759浏览量

172286 -

sram

+关注

关注

6文章

834浏览量

117746 -

Layout

+关注

关注

15文章

424浏览量

75443 -

DRC

+关注

关注

2文章

157浏览量

38352 -

SRAM存储器

+关注

关注

0文章

89浏览量

17752 -

GDS

+关注

关注

0文章

28浏览量

6709

原文标题:用Calibre给版图加Metal fill/dummy

文章出处:【微信号:集成电路设计及EDA教程,微信公众号:集成电路设计及EDA教程】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

版图设计-上海

Mentor工具简介Calibre物理验证系列

基于Cadence与Mentor的CMOS模拟集成电路版图该如何去设计?

基于calibre的MIC总线控制器专用集成电路版图检查

应用Calibre xRC辅助模拟电路版图纠错

在IC版图设计中dummy的作用

dummy电阻的作用及注意事项

StarRC教程-如何基于Dummy/Metal Fill GDS抽取寄生RC文件

100分的Calibre只发挥了60分的作用?

到底谁能提升Calibre的效率?

如何提升跑Calibre效率呢?

如何在Virtuoso界面集成Calibre接口呢?

100分的Calibre只发挥了60分的作用是何原因?

如何用Calibre给版图加Metal fill/dummy呢?

如何用Calibre给版图加Metal fill/dummy呢?

评论