PG090中文文档简介

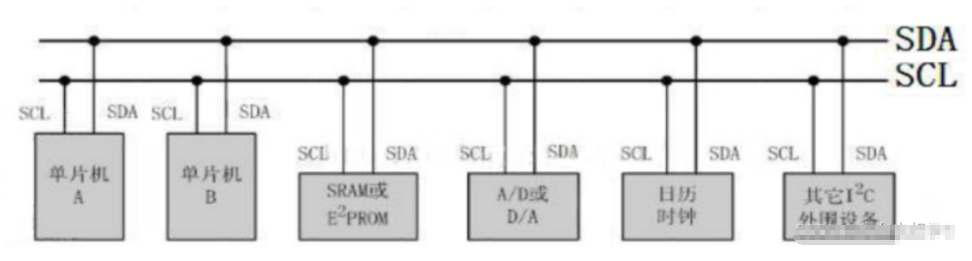

LogiCOREIPAXI IIC总线接口连接到AMBAAXI规范,提供低速、两线串行总线接口,可连接大量流行的设备。

本产品规格定义了架构、硬件(信号)接口、软件(寄存器)接口,以及AXI IIC总线接口模块的参数化选项。

特点

•符合行业标准I2C协议

•通过AXI4-Lite接口访问寄存器

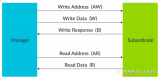

•主站或从站操作

•多主机运行

•软件可选确认位

•仲裁丢失中断,模式从主站自动切换到从站

•调用地址识别中断,从主站到从站的模式自动切换

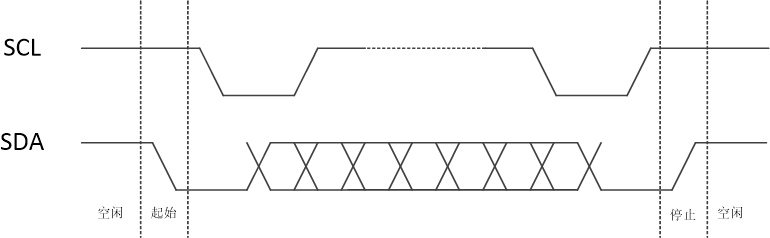

•启动和停止信号的生成和检测

•重复产生START信号

•确认位生成和检测

•总线繁忙检测

•快速模式增强型1 MHz、快速模式400 kHz或标准模式100 kHz运行

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

AMBA总线

+关注

关注

0文章

34浏览量

9486 -

IIC接口

+关注

关注

0文章

23浏览量

11576

原文标题:PG090 | AXI IIC总线接口

文章出处:【微信号:fpga加油站,微信公众号:fpga加油站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

IIC总线为什么是半双工?

IIC(Inter-Integrated Circuit)总线是一种半双工的串行通信接口。在I2C总线上,主设备和从设备之间的数据传输是采用半双工模式进行的。这意味着主设备和从设备在不

LogiCORE JTAG至AXI Master IP核简介

LogiCORE JTAG至AXI Master IP核是一个可定制的核,可生成AXIAXI总线可用于处理和驱动系统中FPGA内部的AXI信号。AXI

AMBA3.0 AXI总线接口协议的研究与应用

本文介绍了AMBA3.0AXI的结构和特点,分析了新的AMBA3.0AXI协议相对于AMBA2.0的优点。它将革新未来高性能SOC总线互连技术,其特点使它更加适合未来的高性能、低延迟设

发表于 09-20 08:30

基于AXI总线的DDR3读写测试

本文开源一个FPGA项目:基于AXI总线的DDR3读写。之前的一篇文章介绍了DDR3简单用户接口的读写方式:《DDR3读写测试》,如果在某些项目中,我们需要把DDR挂载到

IIC总线协议时序介绍 IIC总线程序设计

IIC总线是一个双向的两线连续总线,它为集成电路之间提供通信线路。其意思是完成集成电路或功能单元之间信息交换的协议。

发表于 07-23 11:45

•7478次阅读

自定义AXI-Lite接口的IP及源码分析

在 Vivado 中自定义 AXI4-Lite 接口的 IP,实现一个简单的 LED 控制功能,并将其挂载到 AXI Interconnect 总线互联结构上,通过 ZYNQ 主机控制

发表于 06-25 16:31

•2044次阅读

Xilinx FPGA AXI4总线(一)介绍【AXI4】【AXI4-Lite】【AXI-Stream】

从 FPGA 应用角度看看 AMBA 总线中的 AXI4 总线。

发表于 06-21 15:21

•1875次阅读

AXI IIC总线接口介绍

AXI IIC总线接口介绍

评论