在古代,我们的祖先就掌握了测试技术,例如农民发明吹风机测试稻谷,把饱满的谷粒和谷壳分离开来,这就是早期的测试机器。

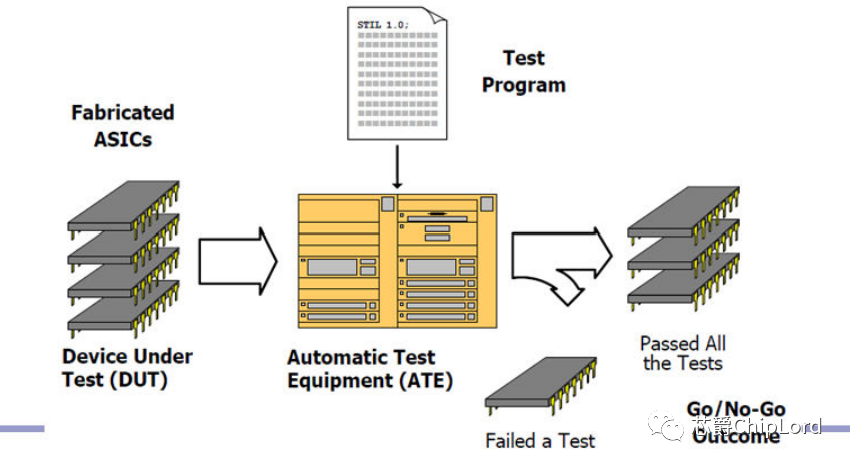

生产测试的目的是把好的物品和有瑕疵的物品分离出来,集成电路行业,测试的目标是把功能正确的芯片和有瑕疵的芯片分离出来,保证客户使用的是功能完整的芯片。

按照摩尔定律,集成电路的规模每两年翻一番,设计的规模越来越大,工艺尺寸越来越小。随着电路的集成度越来越高,生产测试的成本也越来越高。为了降低测试成本和难度,提高芯片的质量和良品率,需要为芯片进行可测性设计(design for test),简称DFT。

可测性设计是在芯片设计过程中保证功能的前提下,加入特殊的测试结构,芯片制造完成后进行DFT测试,如果在制造或者封装的过程中有瑕疵,芯片不能正常工作,通过DFT测试可以筛选出这种芯片。可测性设计与设计验证不同,设计验证是通过对设计的分析,排除设计中的错误,确保该设计符合其技术规范,保证设计与要求一致。

芯片制造和封装过程中的测试可以大致分为如下三类:

其中WAT测试和DFT没有关系,主要是用来检测FAB的制造工艺是否有问题,它并没有测试芯片,而是测试die和die之间的scribe line上面的特殊结构。

CP是测试晶圆上的每颗die,实际上,只有通过CP测试的die才会进行封装,而未通过测试的die会被淘汰。

FT测试是die封装以后的测试,如果没有异常,才会到客户那里。

可测性设计具体是什么呢?

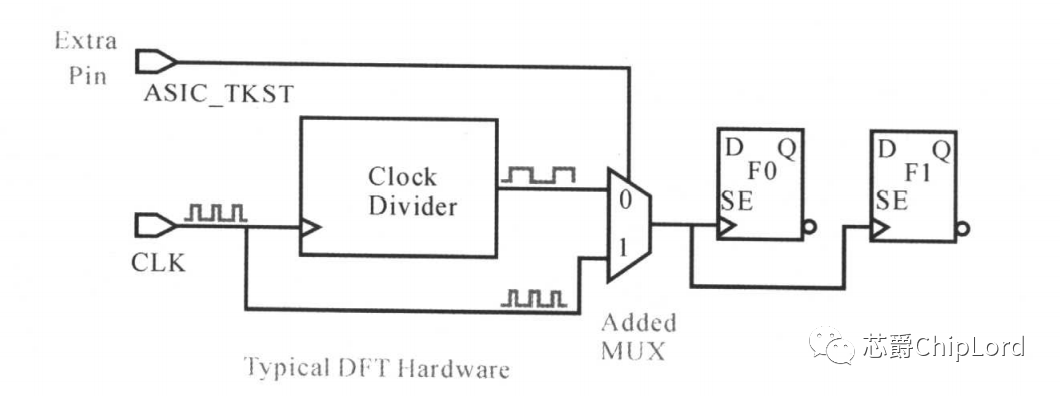

为了使芯片方便测试,在设计中额外的增加或者修改某些逻辑,增加输入,输出端口,但是这种设计不会改变芯片的功能。

如下图所示:DFT就是增加额外的输入端口(ASIC_TKST),在设计中加入MUX,使寄存器F0,F1的时钟引脚在测试过程中可以直接由输入时钟端口CLK控制。

可测性设计内容丰富,主要分为四大类:后面会详细介绍。

- Scan Chain

- Boundar Scan

- MBIST

- ATPG

当我们对已制造出来的芯片进行生产测试时,先把芯片插入自动测试设备中(ATE),然后输入测试程序,测试程序中包含ATPG生成的测试向量,测试向量简单理解包含输入值和期望值,如果ATE收集的实际值和期望值不一致,则可以判断芯片有故障。

接下来介绍物理瑕疵(defects)和故障模型(fault models),这里主要涉及抽象与建模。

芯片的物理瑕疵是指在生产制造过程中产生的瑕疵,这种瑕疵使得芯片不能正常工作,值得注意的是,这里的测试并不是测试逻辑设计的错误,而是测试在芯片生产过程中引入的瑕疵,主要由如下因素引起:

- 开路和短路(open and short)

- 金属线之间的桥接(bridging bewteen metal lines)

- 通过绝缘氧化物的导电性击穿(conductive pinholes through insulating oxides)

下图是一个简单CMOS反相器的物理版图,它由一个n型下拉晶体管(n-type pull-down transistor)和一个p型上拉晶体管(p-type pull-up transistor)组成。如果一粒尘埃落在金属连线上就可以使该线开路,过度的金属刻蚀可能引起金属桥接现象,即直接短路到电源或者地线上。一个有瑕疵的下来晶体管永远处于开路的状态,从而就像直接短路到地线上一样。

瑕疵的行为就像永久的短路到电源或者地线上一样,我们可以抽象为输入或输出引脚stuck at在逻辑"0"或"1"上,大部分的CMOS门单元的版图类似,因此可以抽象建模,把stuck at 1 or 0代表具体的物理瑕疵。

综上所述,故障模型(fault model)就是用抽象逻辑模型来表示物理瑕疵(defect)的结果。

stuck-at fault model(SAF)模型仍然是最常见的故障模型。

测试SAF的规则是不可以使用内部探针,我们只能通过输入/输出端口对芯片进行测试,经封装后,输入/输出端口对应于芯片的封装管脚,ATE设备可以对每个输入端口进行驱动,控制测试芯片的每个输入端,同时对每个输出端进行采样,把采样结果与预期值进行比较,来判断芯片的好坏。

-

寄存器

+关注

关注

31文章

5589浏览量

129064 -

晶体管

+关注

关注

78文章

10250浏览量

146278 -

DFT设计

+关注

关注

0文章

11浏览量

9060 -

时钟控制

+关注

关注

0文章

18浏览量

7127 -

CMOS反相器

+关注

关注

0文章

19浏览量

7186

发布评论请先 登录

可测性设计DFT-生产测试简介

可测性设计DFT-生产测试简介

评论