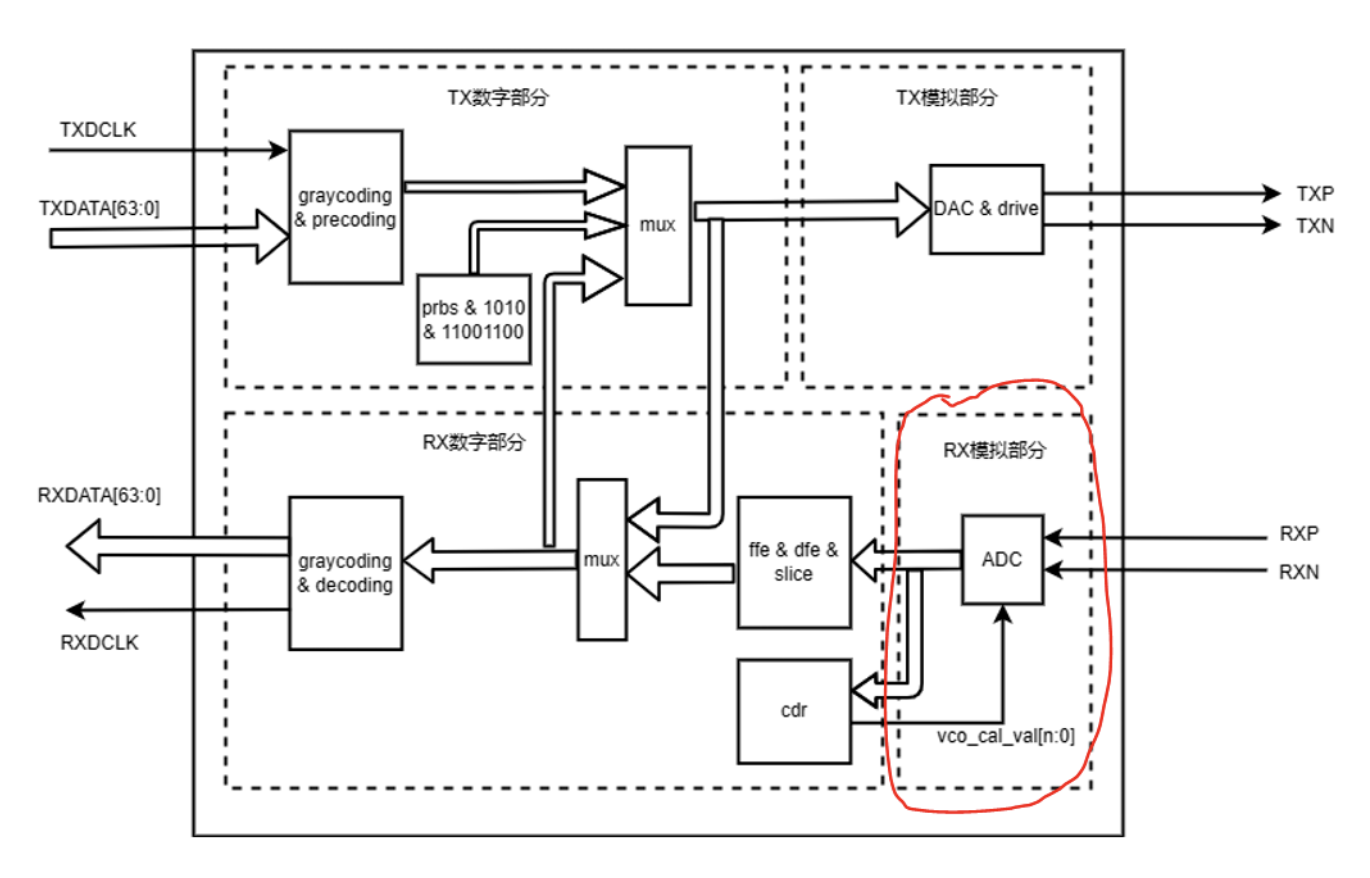

对于图1所示TX/RX模拟部分的实现方式,大家是不是一直有这样的疑问: Serdes在将并行data通过DAC串行发出去的时候,或者在接收端通过ADC进行串行data采样的时候,是怎么实现的?比如56G的serdes就是用56G的ADC和DAC吗?

答案是肯定不是,没有那么高频的ADC和DAC,通常ADC和DAC最大可以工作在1G频率左右,再大的频率无法实现精度的。所以采用多个ADC/DAC分时工作的模式。

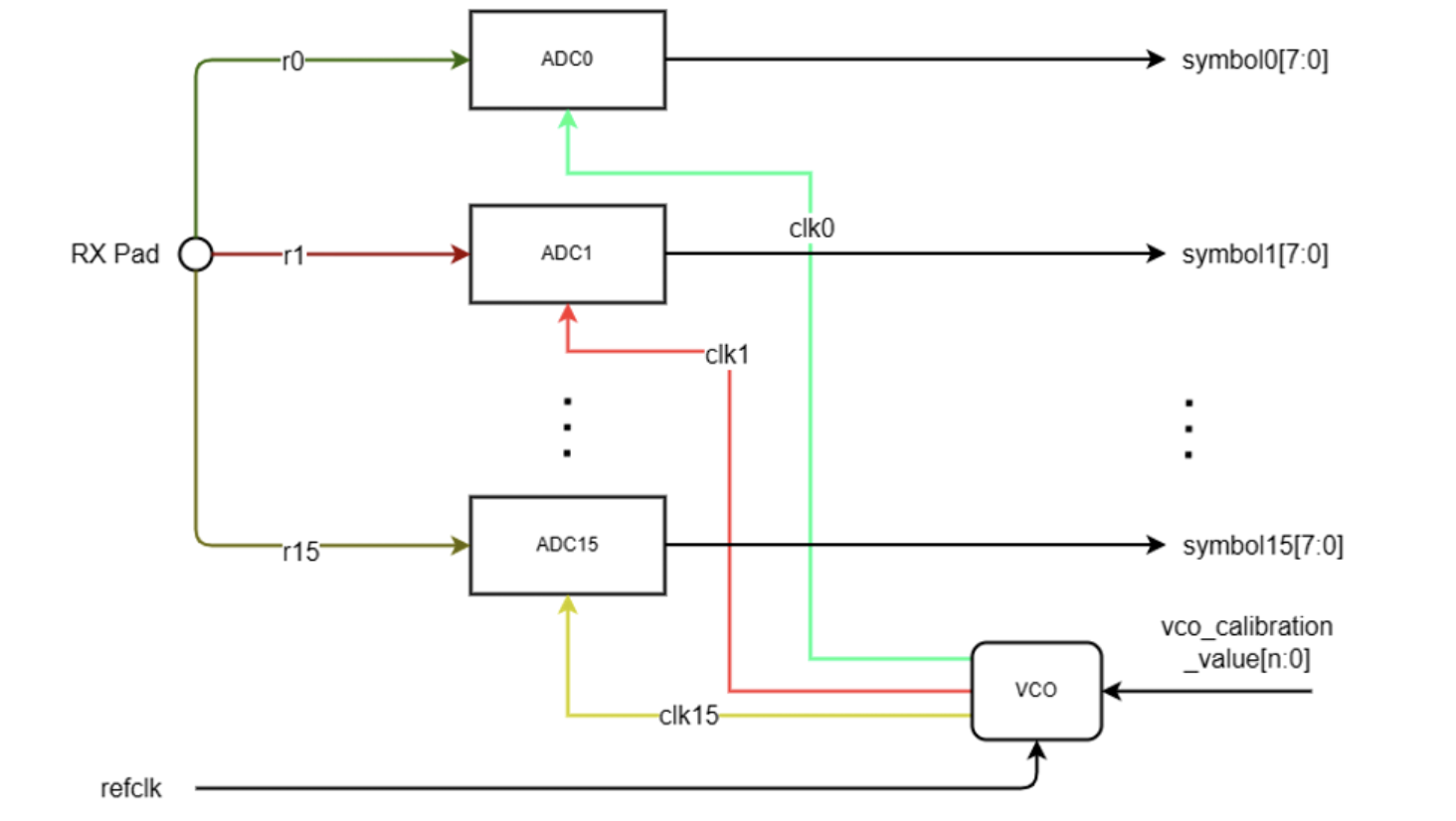

RX接收端采样方式如下图2,RX Pad连接到16个ADC上,后端要严格约束Pad到不同ADC之间的走线一样长,可以通过绕线方式实现。

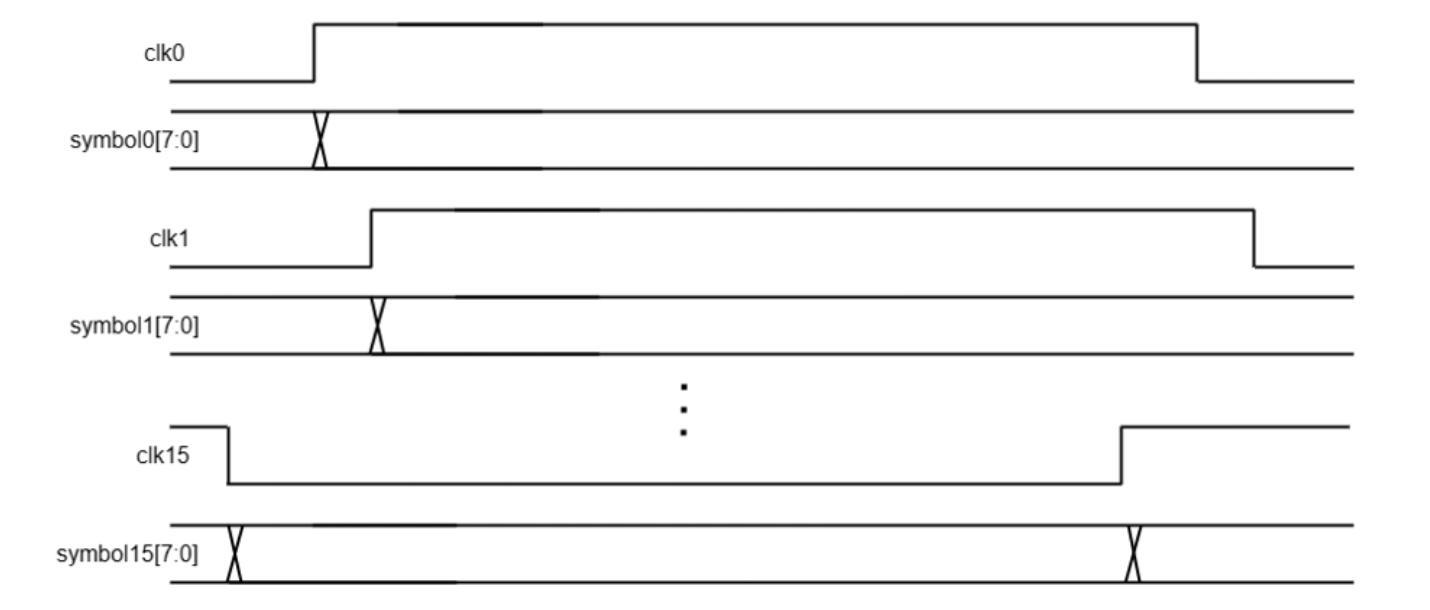

CDR的数字逻辑输出vco_calibration_value[n:0]到模拟VCO实现相位调整。VCO输出多路时钟到多个ADC,如图3所示,比如通过16个ADC分时采样,VCO输出的相邻时钟差90°/16。

ADC在时钟上升沿进行采样,然后模拟通过clk15将16个采样symbol[7:0] pipe到数字逻辑,然后进行均衡判决。TX端的DAC发送端是相同的方式进行的。

图1:serdes架构框图

图2:RX ADC采样框图

图3:RX ADC采样时钟图示

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

接收机

+关注

关注

9文章

1248浏览量

56452 -

adc

+关注

关注

100文章

7950浏览量

557033 -

时钟信号

+关注

关注

4文章

510浏览量

30097 -

ADC采样

+关注

关注

0文章

134浏览量

13616 -

VCO设计

+关注

关注

0文章

2浏览量

3594 -

SERDES接口

+关注

关注

0文章

28浏览量

3380

发布评论请先 登录

相关推荐

热点推荐

从SerDes到SoC,全场景适配的FCom差分晶振设计全解

芯片匹配方案

在差分晶体振荡器的系统设计中,确保时钟信号与接收芯片的电气特性完美匹配,是保证整体时序稳定与抖动抑制的关键。FCom在长期产品应用过程中,归纳出覆盖SerDes、高速ADC/DA

发表于 05-30 11:53

SERDES接口电路设计

通信,该SERDES接口方案具有成本低、灵活性高、研发周期短等特点。 1 硬件接口: 硬件的接口如上图所示,主要包括发送与接收模块。 发送模块包括8b/10b编码器,并串转换器

发表于 05-29 17:52

FPGA SERDES接口电路怎么实现?

串行接口常用于芯片至芯片和电路板至电路板之间的数据传输。随着系统带宽不断增加至多吉比特范围,并行接口已经被高速串行链接,或SERDES (串化器/ 解串器)所取代。起初, SERDES

发表于 10-23 07:16

SERDES传输和引脚关联

亲爱的Xilinx论坛,我正在实现基于SERDES协议的序列化传输。我需要在Kintex7上接收8个差分对,这些差分对承载由另一个Kintex7串行化的64位字,主时钟为100MHz。

发表于 03-17 09:53

使用SERDES(LVDS)作为背板怎么实现?

很好的应用笔记,用于在spartan fpgas中实现serdes但是对Virtex5没什么用?任何人都可以指出我使用V5 fpgas正确实现ser

发表于 07-13 15:54

SerDes是怎么工作的

FPGA发展到今天,SerDes(Serializer-Deserializer)基本上是标配了。从PCI到PCI Express, 从ATA到SATA,从并行ADC接口到JESD204, 从RIO

发表于 07-28 07:02

基于SERDES时钟的频率跟随的设计

在很多无线或者有线的系统应用中,都需要器件的接收端能够和链路的发送端的频率做跟随。通常的实现方案都是通过将SERDES的恢复时钟引到芯片外部,然后通过一个cleanup PLL过滤抖动

发表于 11-18 12:08

•8309次阅读

如何使用FPGA实现SERDES协议

速度的并行总线传输串行化的数据。一个实例是用单个PCI-Express 通道,替代传统的32 位、64MHz PCI 总线(可达到2.112Gb/s) ,仅用4 条线(运行在2.5GHz) ,可达到4Gb/s总数据率。简言之, SERD

发表于 10-09 17:25

•20次下载

单通道56G的SERDES,参考时钟如何选取?

为满足目前的56GPAM-4 SerDes技术,以支持更高带宽的100G+以太网和光网络设计。硬件开发人员通常需要100fs(典型值)以下RMS相位抖动规范的时钟。这些设计通常需要与CPU和系统时钟等其他频率时钟混用。

SERDES的优势 SERDES演变的看法

,另一个优势是能够通过一对差分对信号引脚(而不是8、16、32或N个数据引脚和一个时钟引脚)发送数据。在串行传输这个方面得益于更小的数据包和更密集的pcb而节省了成本。具体取决于晶片成本、封装成本、PCB成本和PCB拥塞等因素。 距离优势 在过去的十年里,

serdes串行发送和接收是怎么实现的?serdes就是用56G的ADC和DAC吗?

serdes串行发送和接收是怎么实现的?serdes就是用56G的ADC和DAC吗?

评论