引言

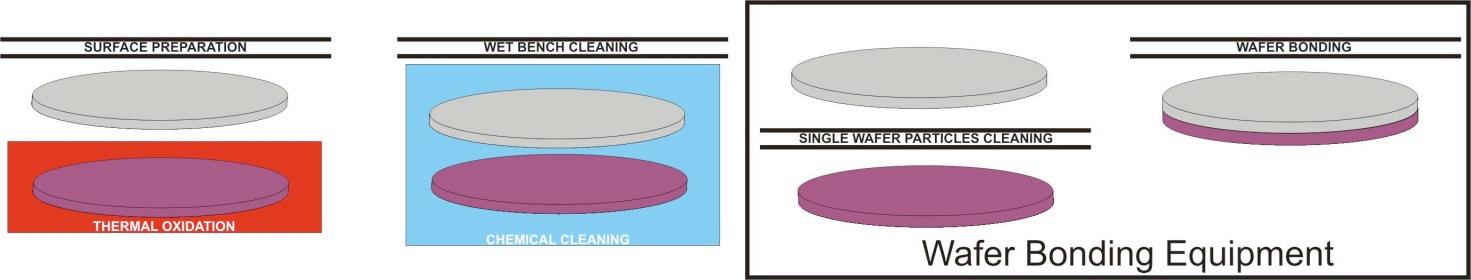

不同的微电子工艺需要非常干净的表面以防止颗粒污染。其中,晶圆直接键合对颗粒清洁度的要求非常严格。直接晶圆键合包括通过简单地将两种材料的光滑且干净的表面接触来将两种材料连接在一起(图1)。在室温和压力下,两种材料表面的分子/原子之间形成的范德华力会产生粘附力。

由于接触的两个表面是刚性的,被困在表面之间的颗粒会产生不接触的区域(未粘合区域或空隙),从而降低产量。已知直径为 1 µm的颗粒会产生键合缺陷(空隙)直径约1厘米!为了防止这种情况发生,集成了由单个晶圆清洁工艺组成的典型工艺步骤。

图1:直接晶圆键合工艺流程示意图

图1:直接晶圆键合工艺流程示意图

由于上述原因,晶圆键合对基板清洁度要求非常严格。如果对于 CMP 后清洁工艺,传入的晶圆将显示数千或数十个颗粒水平通过清洁过程去除的颗粒数量减少到每个晶圆数百或数十个,在直接键合的情况下,成功可靠的晶圆键合所需的颗粒水平在每200毫米或300 毫米直径晶圆少于10个颗粒的范围内(粒径>0.12 µm)。

有了这样的成功标准,这种新型清洁方法的效率还必须通过颗粒中性来鉴定。这里作为直接晶圆键合的应用进行研究,MegPie工艺也可以进行微调,以满足其他关键应用(热压键合、外延、层沉积、光刻)的清洁和吞吐量要求。

实验

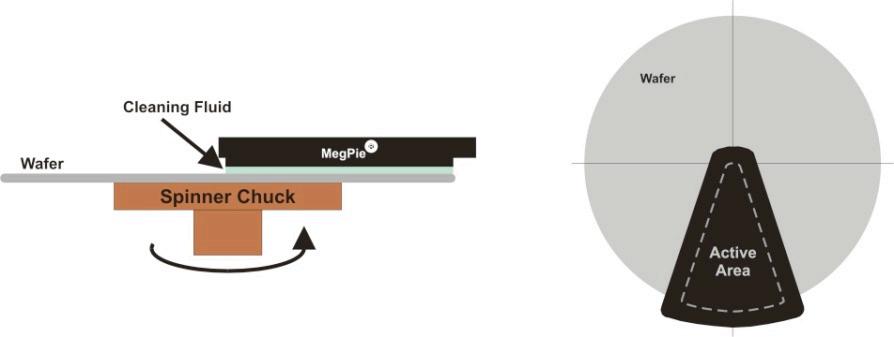

英思特在实验中使用了两种不同型号的径向均匀面积兆声波换能器 MegPie(图 2)。该换能器将声能耦合到由基板和换能器面形成的流体填充间隙中。形状和谐振器设计确保在旋转基底的整个表面上均匀的声学剂量,而无需扫描运动。持续监控前向和反射射频功率以及 PZT 晶体温度,确保一致且可重复的声学处理条件。

a

a  b

b

图2:基于MegPie换能器的单晶圆清洗系统:a.原理图设置b.集成在生产晶圆键合机上的V3 MegPie模型示例

结论

在许多关键的清洁步骤中,晶圆级键合需要无颗粒的表面以实现无缺陷的键合。这一要求要求在键合工艺步骤之前进行单晶片清洁步骤,该步骤能够去除剩余的少量颗粒,同时不添加任何额外的颗粒或金属离子污染物。

过去,清洁步骤是通过刷子擦洗、兆频超声波喷嘴或矩形兆频超声波区域换能器进行的。使用这些标准清洁方法可能不足以满足键合应用的要求,因为存在晶圆间交叉污染或接触活性表面的风险,均匀性相对较差(喷嘴清洁涉及使用几毫米的水流扫描晶圆),甚至由于不均匀地暴露于声波(例如对于矩形换能器)而引起表面下缺陷。

带有单晶蓝宝石谐振器的大面积 V3 MegPie在单晶圆预键合清洁站中实现,可实现高颗粒去除效率,并且不添加颗粒(颗粒中性)。该换能器的专有设计确保了非接触式清洁,并且整个晶圆上的声能径向均匀性非常高。

使用清洁化学品(例如稀释的 NH4OH)可以增强清洁效果。MegPie传感器已被证明是颗粒中性的,并且能够显示出高PRE结果。

审核编辑:汤梓红

-

半导体

+关注

关注

328文章

24520浏览量

202182 -

晶圆

+关注

关注

52文章

4527浏览量

126445 -

蚀刻技术

+关注

关注

0文章

23浏览量

7790

发布评论请先 登录

相关推荐

适用于基于晶圆键合的3D集成应用的高效单晶圆清洗

适用于基于晶圆键合的3D集成应用的高效单晶圆清洗

评论