Bump Metrology system—BOKI_1000

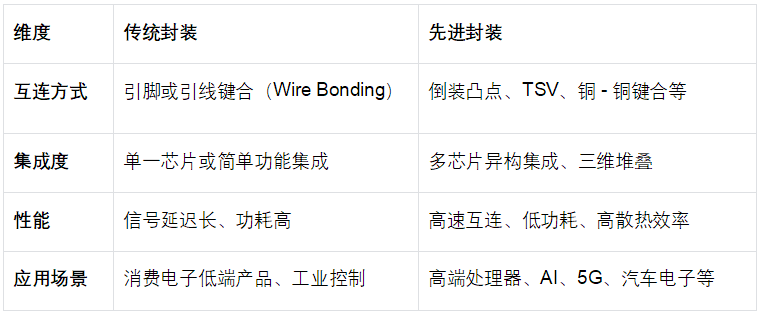

在半导体行业中,Bump、RDL、TSV、Wafer合称先进封装的四要素,其中Bump起着界面互联和应力缓冲的作用。

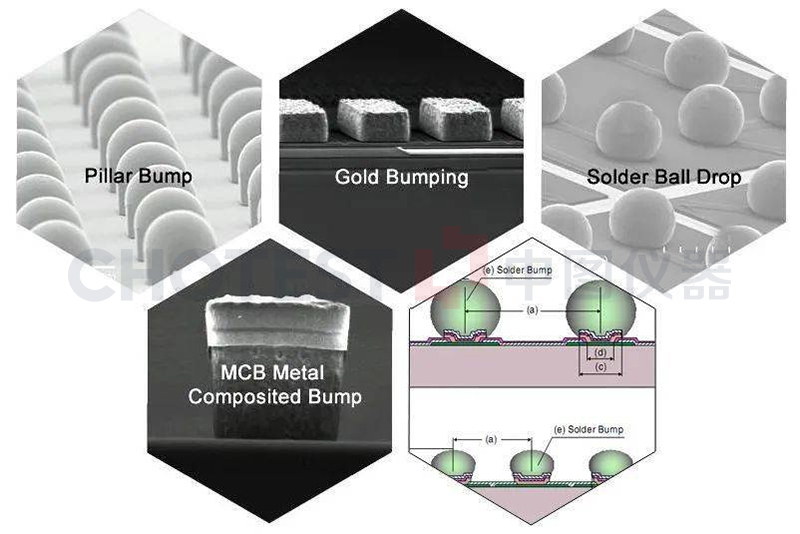

Bump是一种金属凸点,从倒装焊FlipChip出现就开始普遍应用,Bump的形状有多种,常见的为球状和柱状,也有块状等其他形状,下图所示为各种类型的Bump。

Bump起着界面之间的电气互联和应力缓冲的作用,从Bondwire工艺发展到FlipChip工艺的过程中,Bump起到了至关重要的作用。随着工艺技术的发展,Bump的尺寸也变得越来越小,从最初 Standard FlipChip的100um发展到现在最小的5um。

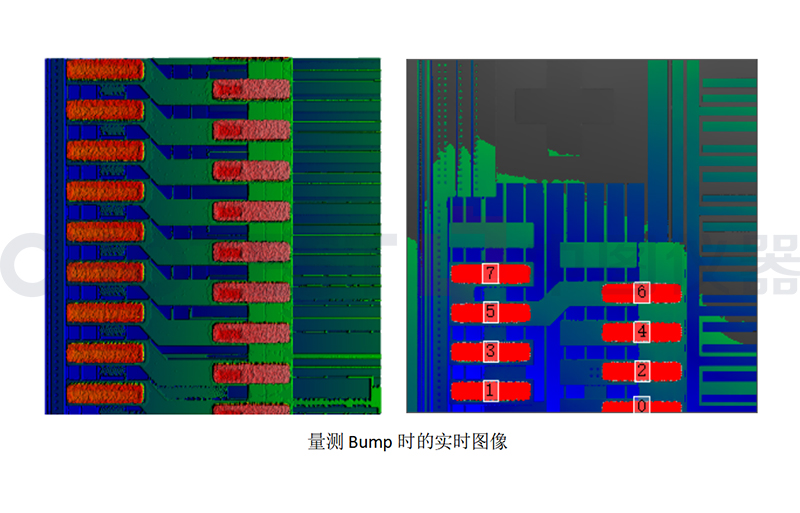

伴随着工艺技术的高速发展,对于Bump的量测要求也不断提高,需要把控长宽尺寸,高度均匀性,亚纳米级粗糙度、三维形貌等指标。

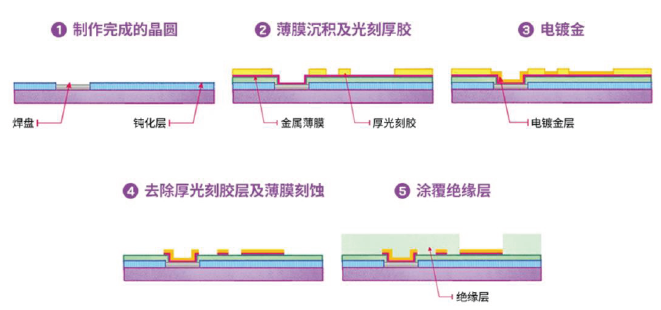

以粗糙度指标为例,电镀工艺后的Cu 凸点表面粗糙并存在一定的高度差,所以键合前需要对其表面进行平坦化处理,如化学机械抛光(CMP),使得键合时Cu 表面能够充分接触,实现原子扩散,由此可见把控Bump表面粗糙度是必不可缺的过程。

为了贴合工艺制程,积极响应客户Bump计量需求,中图仪器以高精度、多功能合一等优势将自研量测设备推向众多半导体客户。BOKI_1000系统支持键合、减薄、翘曲和切割后的基板,可以为包括切割后、预键合、铜焊盘图案化、铜柱、凸块(Bump)、硅通孔(TSV)和再分布层(RDL)在内的特征提供优异的量测能力。

-

封装

+关注

关注

128文章

9139浏览量

147888 -

测量仪器

+关注

关注

3文章

889浏览量

45873 -

先进封装

+关注

关注

2文章

517浏览量

972

发布评论请先 登录

晶圆级封装Bump制作中锡膏和助焊剂的应用解析

晶圆级封装(WLP)中Bump凸点工艺:4大实现方式的技术细节与场景适配

看点:台积电在美建两座先进封装厂 博通十亿美元半导体工厂谈判破裂

矽塔栅极驱动IC原厂代理供应

矽塔栅极驱动IC原厂代理供应

台积电最大先进封装厂AP8进机

先进封装,再度升温

先进封装技术-19 HBM与3D封装仿真

先进封装厂关于Bump尺寸的管控

先进封装厂关于Bump尺寸的管控

评论