arm中断是怎么实现的

首先,了解什么是中断。中断是指在CPU执行某个程序时,突然发生的一些事件需要CPU立即停止正在执行的程序并去执行该事件相应的程序,这个过程叫做中断。中断是系统中一个重要的机制,能够提高系统的实时性和可靠性。在ARM处理器中,中断的实现主要涉及到下面的几点。

一、中断控制器

ARM系统中,中断控制器是实现中断的重要组成部分。中断控制器的主要作用是监控外部硬件中断请求并向CPU发出中断请求信号,同时还需要根据优先级为CPU分配中断请求。

ARM中断控制器有两种类型:简单中断控制器(Simple Interrupt Controller,简称SIC)和通用中断控制器(Generic Interrupt Controller,简称GIC)。SIC适用于较为简单的系统,而GIC则适用于较为复杂的系统,支持更多的中断请求。具体地,GIC一般包含一个中央控制器,多个本地控制器和一个分配器。中央控制器负责处理高优先级中断故障,本地控制器负责处理本地外设的中断,分配器负责将中断请求分配给本地控制器。

二、中断向量表

在ARM中,中断向量表是用来存储中断服务例程(Interrupt Service Routine,简称ISR)的一组内存区域。中断向量表中有多个向量表项,每个向量表项对应一种中断类型,其中存储着相应的中断服务例程的入口地址。

中断服务例程是中断处理程序,用于响应中断事件。当中断请求发生时,中断控制器会向CPU发送中断请求,此时CPU读取中断向量表中相应的向量表项得到ISR的入口地址,然后跳转到该地址执行ISR。ISR会负责处理中断事件,并将处理结果返回。

三、中断的优先级

在ARM中,设备的中断请求有不同的优先级,优先级越高的请求将先被响应。中断优先级是在编译链接时静态确定的,每个设备都有一个预设的中断请求优先级,这些优先级由系统设计人员在初始化系统时进行设置。

在中断处理时,如果有多个中断同时发生,CPU会先执行优先级最高的中断,而其他中断则被挂起。一旦执行完毕,CPU会返回到挂起的中断程序中继续执行,如此循环直至所有中断都被处理完毕。

四、中断处理流程

当外部设备发生中断请求时,中断控制器会对请求进行处理:

1、中断请求的产生:外部设备发生某种事件的时候,向外部中断控制器发出中断请求。

2、中断控制器的处理:中断控制器接收到请求后,通过优先级算法,确定优先级最高的中断,然后发送一个中断请求到CPU。

3、中断向量表的查询:CPU响应中断请求后,根据请求所对应的中断类型,查询中断向量表得到对应的ISR入口地址。

4、执行ISR:CPU通过跳转到ISR入口地址开始执行ISR代码,中断服务例程开始处理中断事件。

5、保存现场:ISR代码中,对于需要暂停程序的部分,需要保存当前程序现场以保证中断处理结束后能正确恢复执行的指令。

6、处理中断:在ISR中,处理中断的对应逻辑,确定该中断事件对应的操作,并执行相应的操作完成该中断的处理。

7、恢复现场:中断处理结束后,ISR需要恢复保存的现场,以便中断结束后程序能继续执行。

通过以上的流程,ARM的中断处理功能才可以有效地响应外部设备中断请求,并完成对应的中断处理工作,起到保障系统实时性和可靠性的作用。

-

ARM

+关注

关注

135文章

9499浏览量

388555 -

中断控制器

+关注

关注

0文章

62浏览量

9773

发布评论请先 登录

电能质量在线监测装置是如何实现对电压中断事件的识别的?

芯源MCU中断相关寄存器

Arm神经技术是业界首创在 Arm GPU 上增添专用神经加速器的技术,移动设备上实现PC级别的AI图形性能

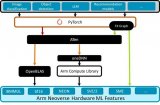

Arm KleidiAI与XNNPack集成实现AI性能提升

Arm Neoverse N2平台实现DeepSeek-R1满血版部署

Arm+AWS实现AI定义汽车 基于Arm KleidiAI优化并由AWS提供支持

Arm Kleidi扩展到汽车市场 Arm Kleidi实现性能自动优化

Arm Cortex-A320 CPU助力嵌入式设备实现高能效AI计算

单片机中断技术详解

串口中断是内部中断还是外部中断,串口中断是怎么触发的

串口中断需要清除标志位吗,串口中断标志位会自动清除吗

EE-188:使用C语言在ADSP-219x DSP上实现中断驱动系统

AN-1420:利用数字锁相环(DPLL)实现相位增建和无中断切换

利用Arm Kleidi技术实现PyTorch优化

arm中断是怎么实现的

arm中断是怎么实现的

评论