当ADC迅猛发展的时候,我们射频工程师的份额,又被吃掉了一块。

大家都慌慌的,心里想,如果ADC一直进步,一直进步,然后直接怼到靠近天线的那边,那射频工程师还能干些啥。

确实,如果把ADC放到靠近天线,采样后就变成数字信号,而数字信号的处理,比模拟信号要灵活的多。

在有的接收机设计中,ADC已经开始对RF直接采样了,也就是开始使用直采架构。

不过,要使用直采架构,也需要满足一定的条件,比如说,ADC在相应的采样率工作时,功耗是满足系统指标的。

采样定理

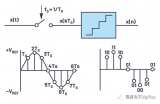

在使用ADC进行采样时,有两种采样方法,一种称为低通采样,也叫过采样(oversampling);另一种称为带通采样,也叫欠采样(undersampling)。

低通采样

低通采样的时候,要求采样率fs>=2*fH,信号才不会发生混叠,在这种情况下,是假定信号的有用信息,频率是DC~fH。但是,在大多数通信系统中,信号通常是窄带信号。在这种情况下,就可以使用带通采样。

带通采样

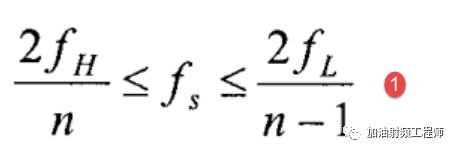

带通采样的时候,避免混叠的最小采样率,取决于信号带宽,而不是有用信号的最高频率fH,即fs>=2*BW,其中BW是信道带宽。不过,需要注意的是,这只是最低要求,除此之外,带通采样时的采样率还需要满足下面的等式,才能实现无混叠采样,即:

其中,fL和fH分别是指带通信号的最低和最高频率。允许的最大的n值为:

如何理解上面的采样速率的要求?

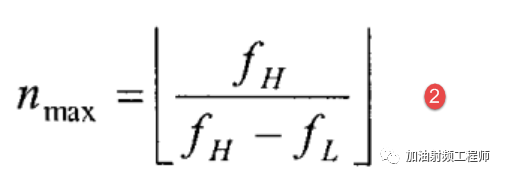

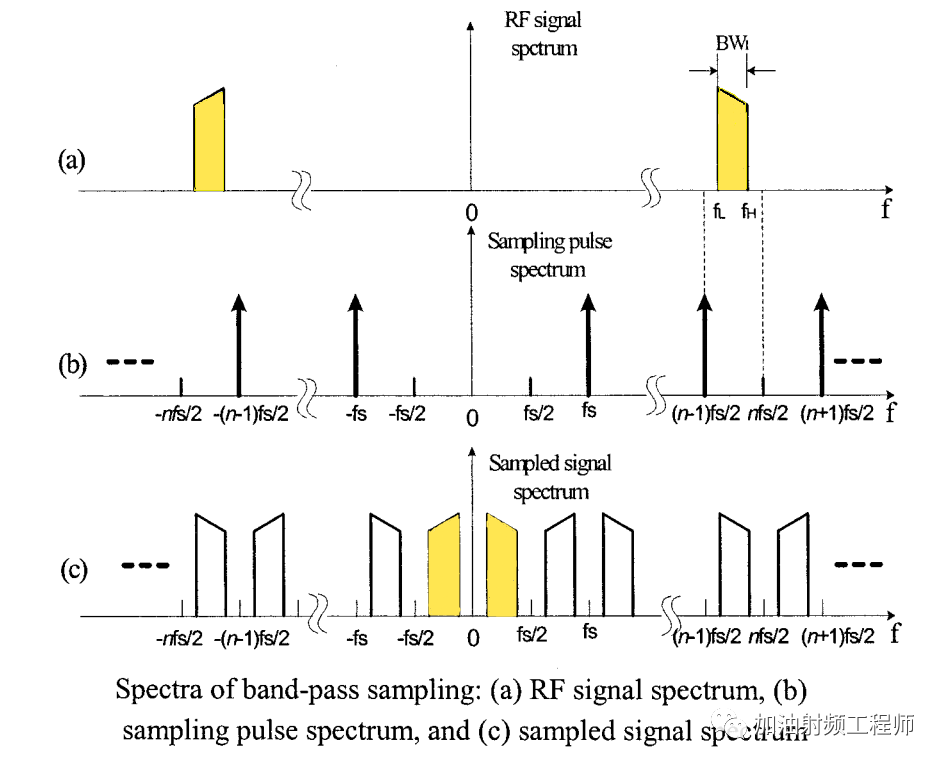

需要采样不混叠,则要求有用信号位于一个奈奎斯特域以内,即(n-1)fs/2~nfs/2以内,如下图所示。

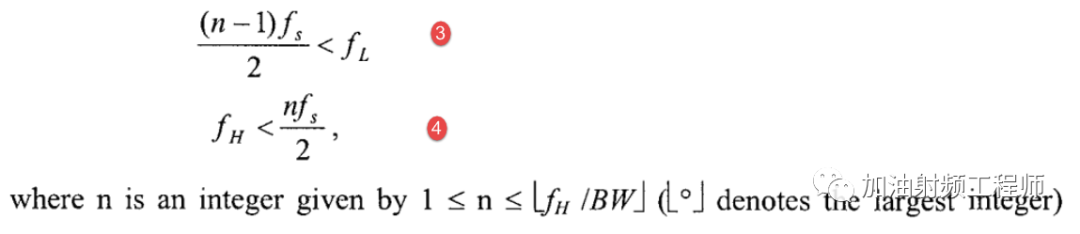

这样的话,很容易就列出下面的两个不等式,如下图所示。

对式子3和4稍微做一下整合,就可以得到式1。

也许会说,低通采样要记一个公式,带通采样又要记一个公式,好麻烦啊!

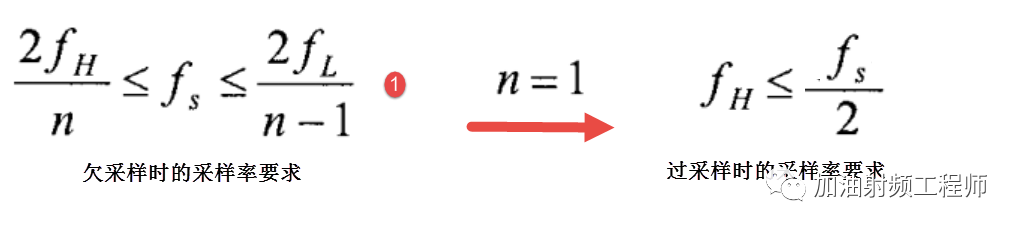

其实,仔细看看,这两个公式是统一的,当n=1的时候,欠采样时的采样率要求,即等于过采样时的采样率的要求。

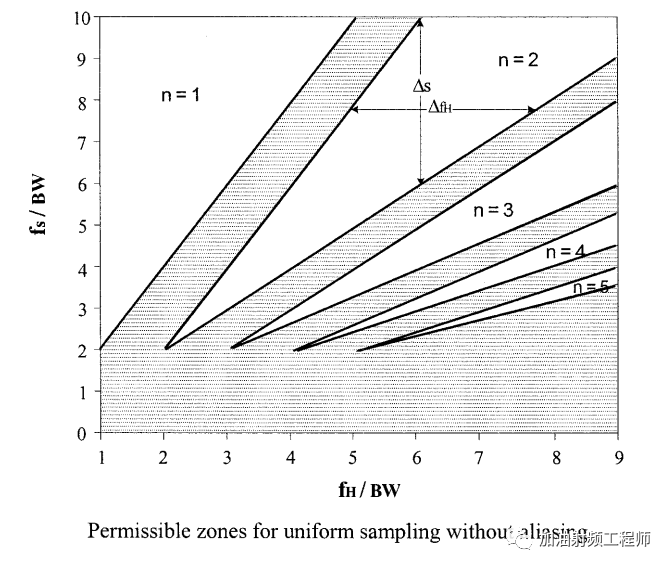

欠采样时的采样率的要求,可以用下图进行图形化表示,横坐标是fH/BW,纵坐标是fs/BW。白色部分,为能够实现无混叠采样的区域,阴影部分,则代表会产生混叠。从图中可以看出,无混叠的区域,随着fs/BW和fH/BW的增加而增加。

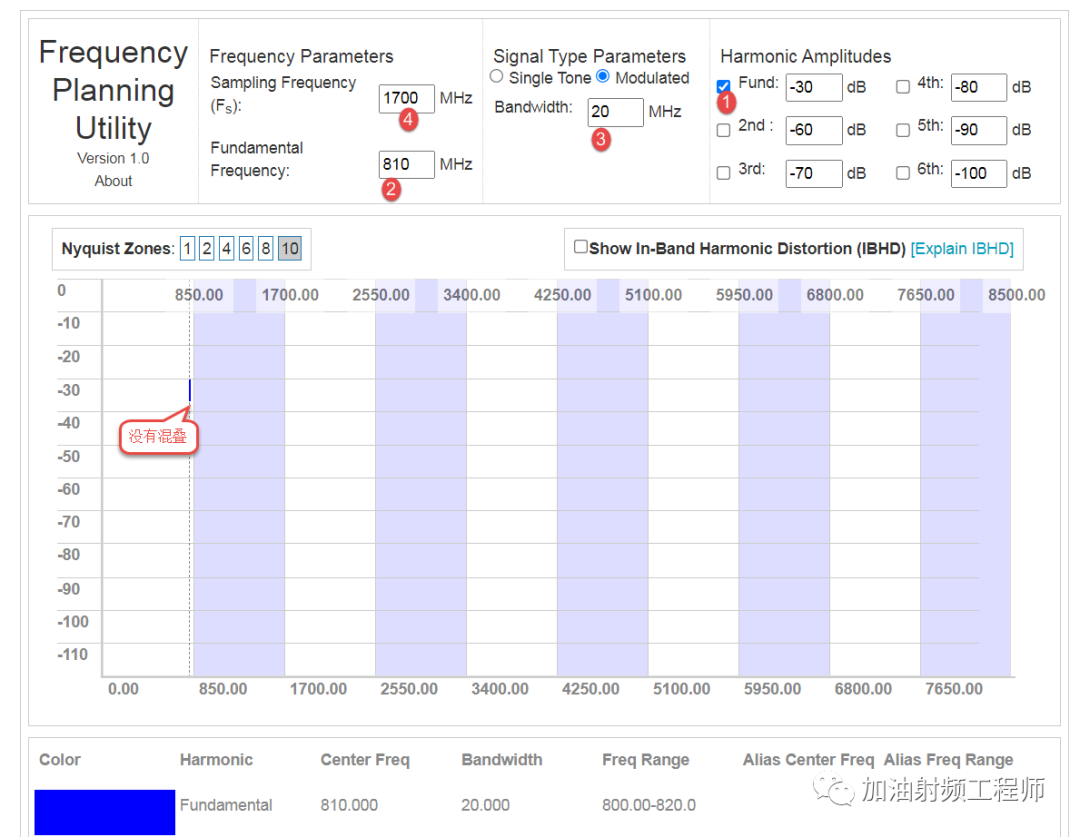

把Harmonic Amplitudes的选项中,只保留Fund选项,然后Nyquist Zones选择10。假设信号的最低频率fL=800MHz,fH=820MHz,那么BW=fH-fL=20MHz。

对于上式1,取n=1,即过采样时,使得fs>2*fH=1640MHz,则显示结果如下图所示。

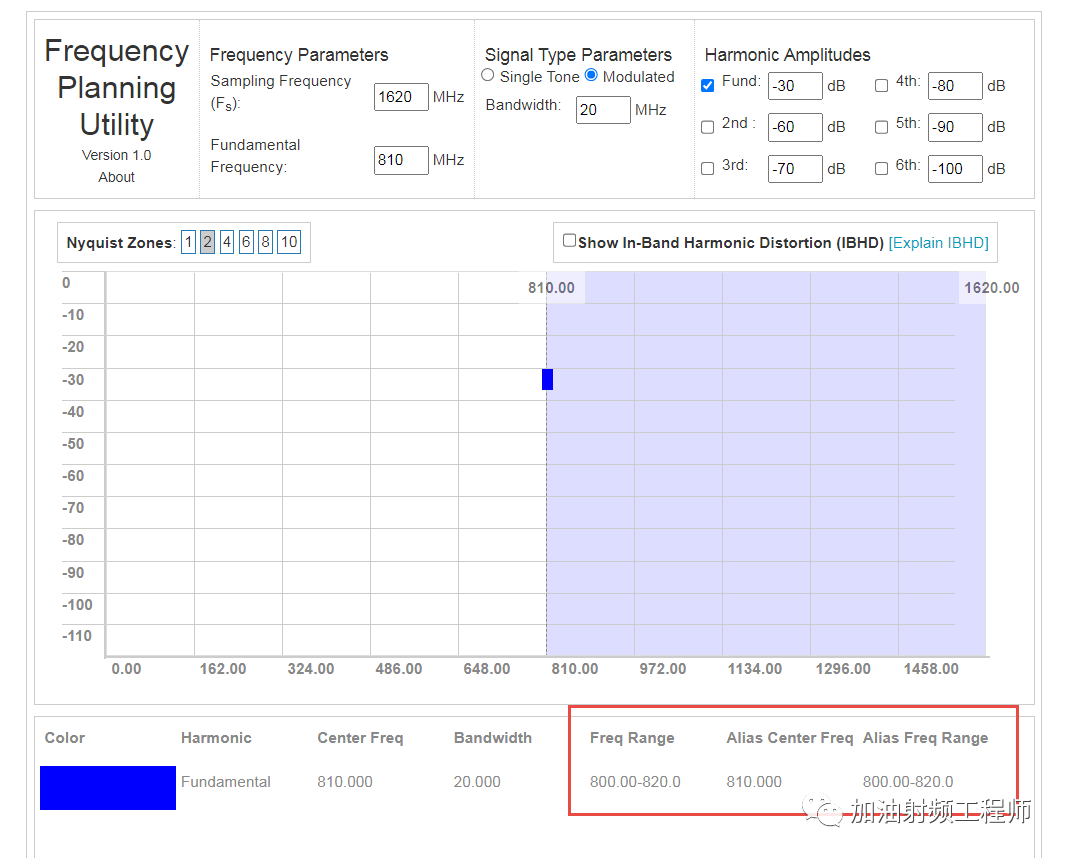

如果把采样率选成1620MHz,则结果如下图所示,

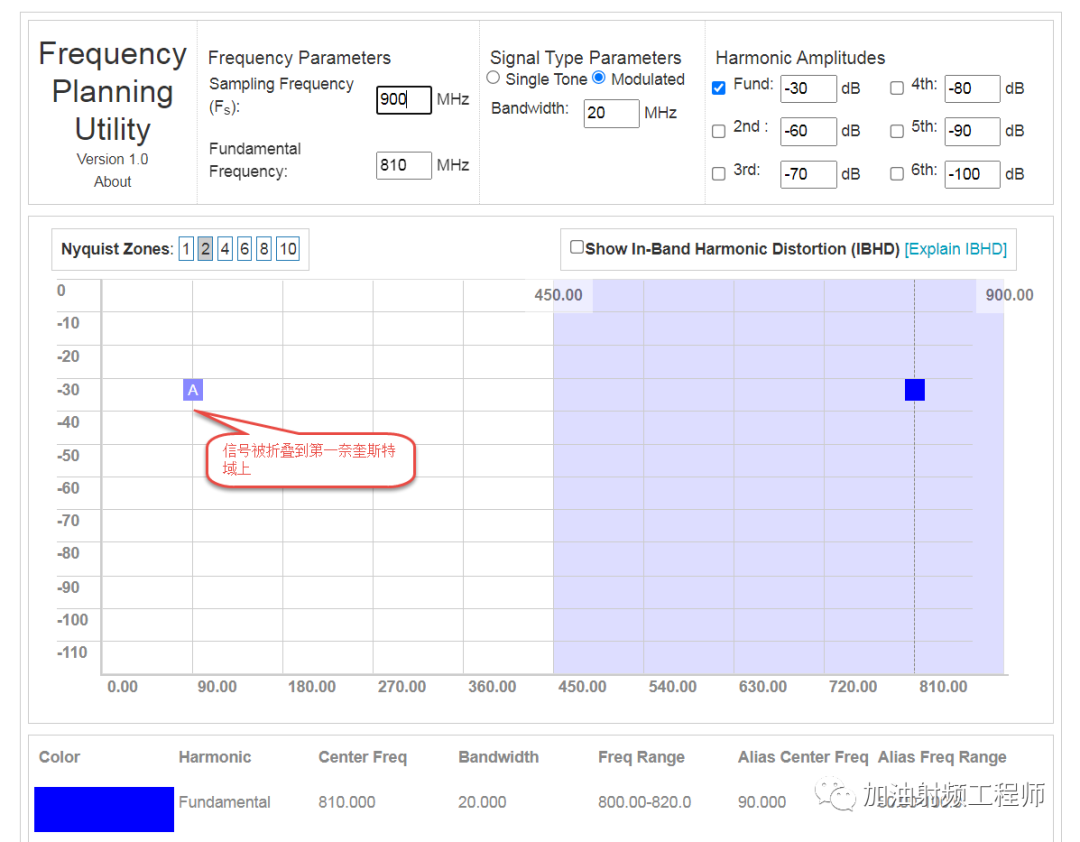

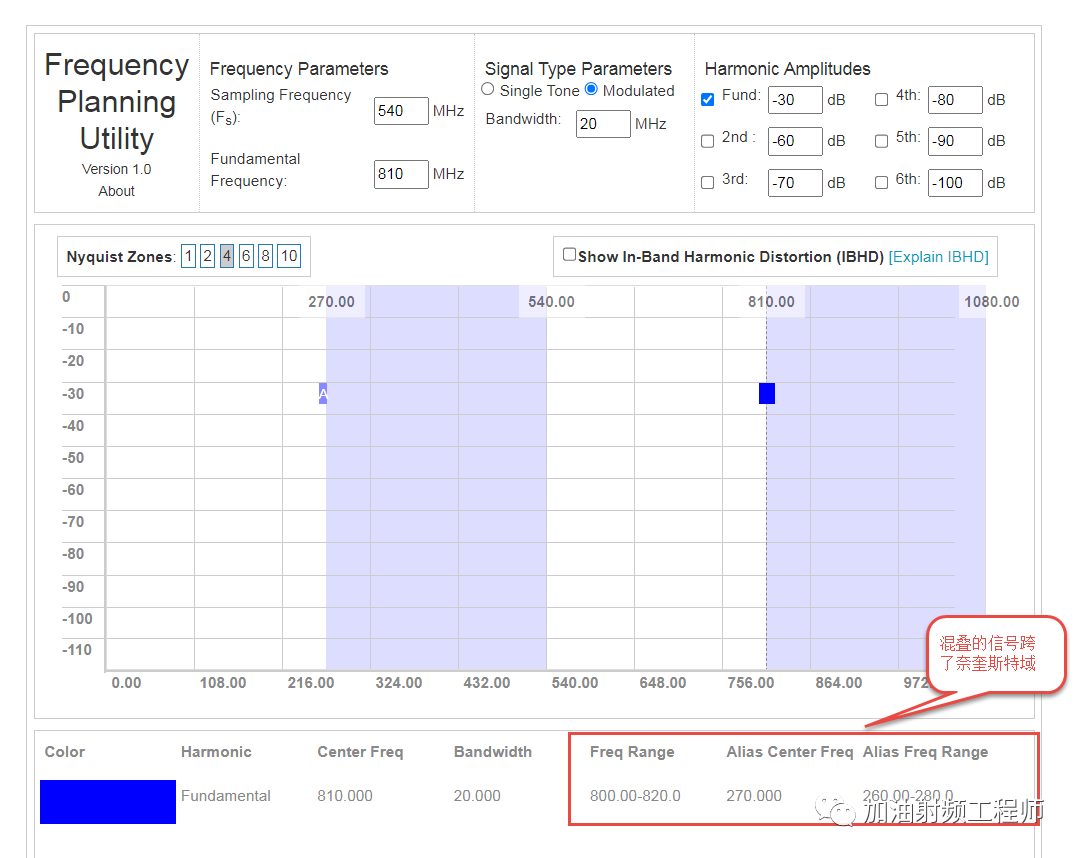

选择n=2,则式1变为fH<=fs<=2*fL,那么假设选择fs=900MHz,满足式1.

那如果选择一个不符合式1的采样率呢,发现采样出来的信号,处于第一奈奎斯特域和第二奈奎斯特域中间,不满足要求。

审核编辑:刘清

-

接收机

+关注

关注

9文章

1240浏览量

55868 -

通信系统

+关注

关注

6文章

1248浏览量

54970 -

数字信号处理器

+关注

关注

5文章

499浏览量

28301 -

混叠滤波

+关注

关注

0文章

2浏览量

5513 -

ADC采样

+关注

关注

0文章

134浏览量

13529

原文标题:直采架构中的带通采样

文章出处:【微信号:加油射频工程师,微信公众号:加油射频工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

TC334 ADC采样25us采不到的问题怎么解决?

如何理解ADS5263的fin和采样率呢?

TIVA在ADC数字比较器中断中能否直接读取采样值?

常见ADC架构设计要求与应用

低速带通采样定理与高速AD/DA之间的矛盾分析

ADC中采样技术的信号链设计挑战

如何理解ADC直采架构中的带通采样要求呢?

如何理解ADC直采架构中的带通采样要求呢?

评论