本节开始简单介绍后端流程。后面会以实际例程说明后端的基本操作。

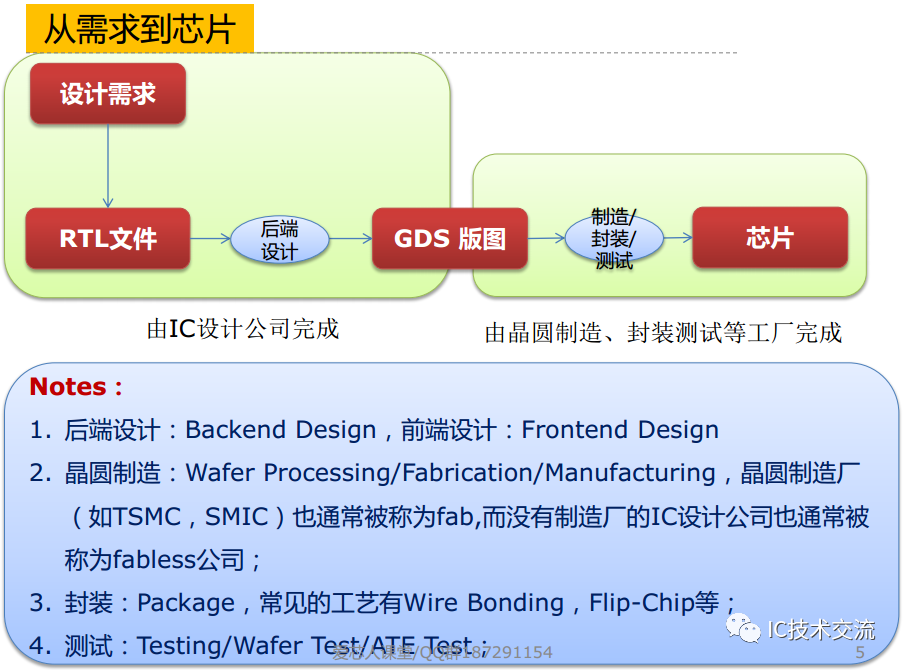

简单来说后端就是将RTL变为GDS版图,再交由晶圆厂(TSMC台积电和SMIC中芯国际)生产制造。大多数IC设计公司都是fabless公司,做到GDS这一步就OK。

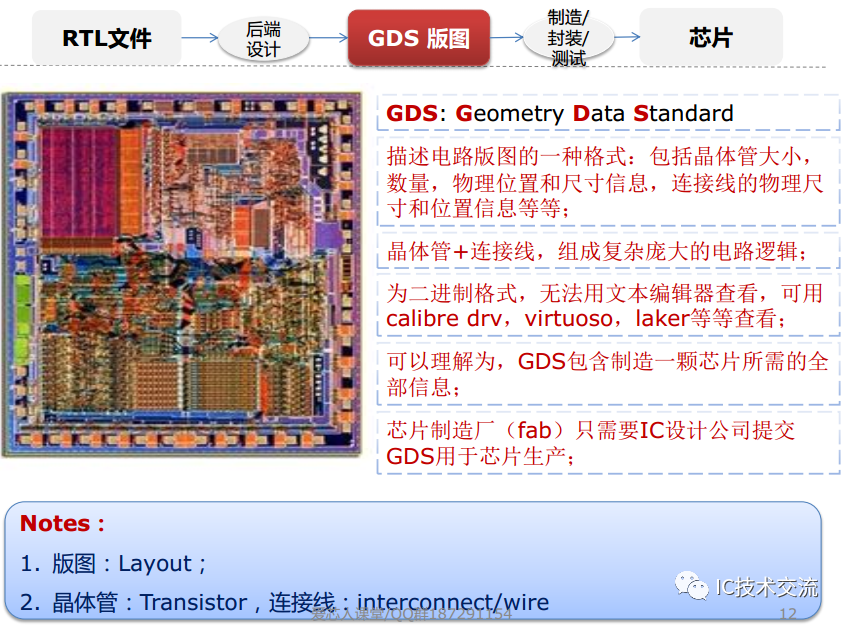

GDS:Geometry Data Standard。它是描述电路版图的一种格式:包括晶体管大小,数量,物理位置和尺寸信息,连接线的物理尺寸和位置信息等等。晶体管+连接线组成庞大的电路逻辑。一般GDS可通过calibre,virtuoso,laker等查看。

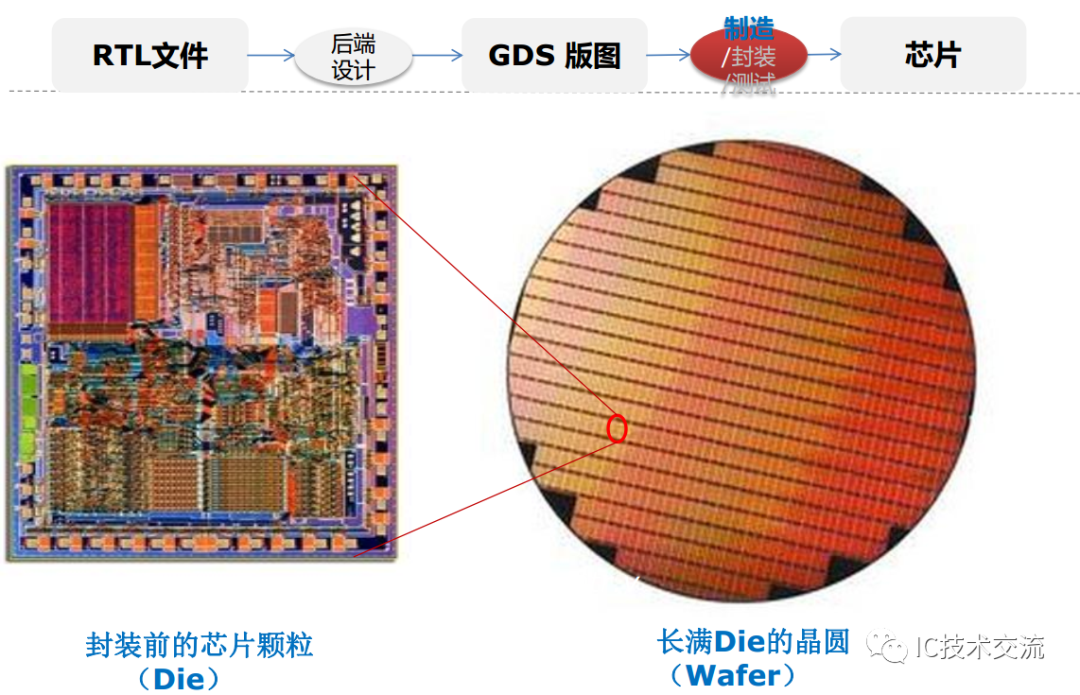

GDS交由晶圆厂后,在一片wafer上切割成多个小块,每块为一个Die,就是芯片的最小核心。

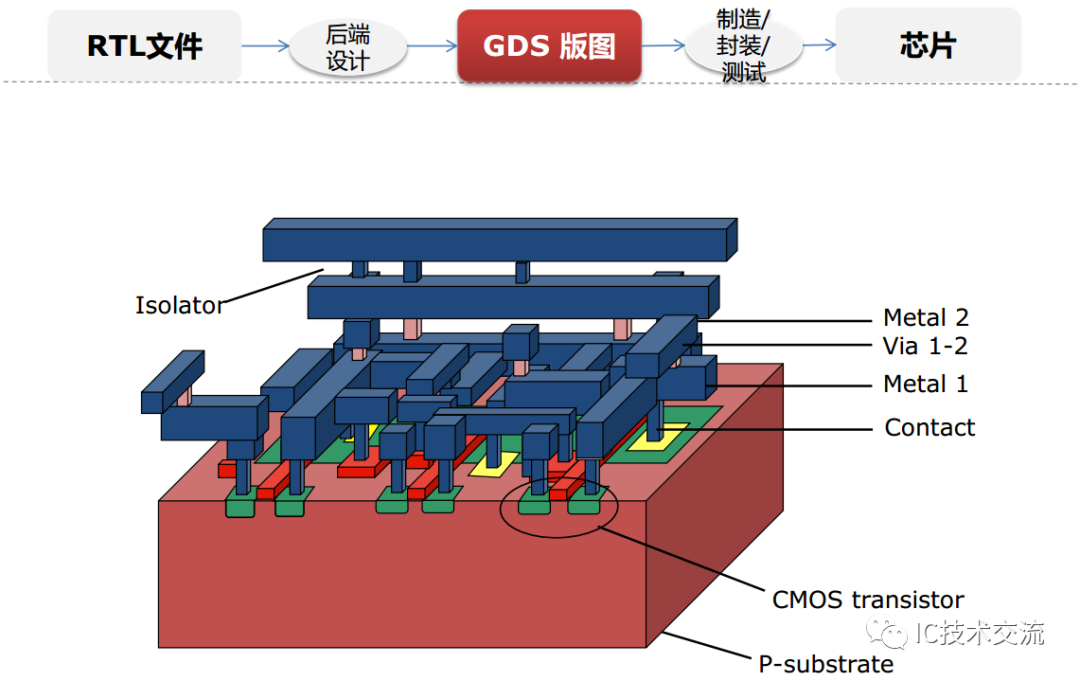

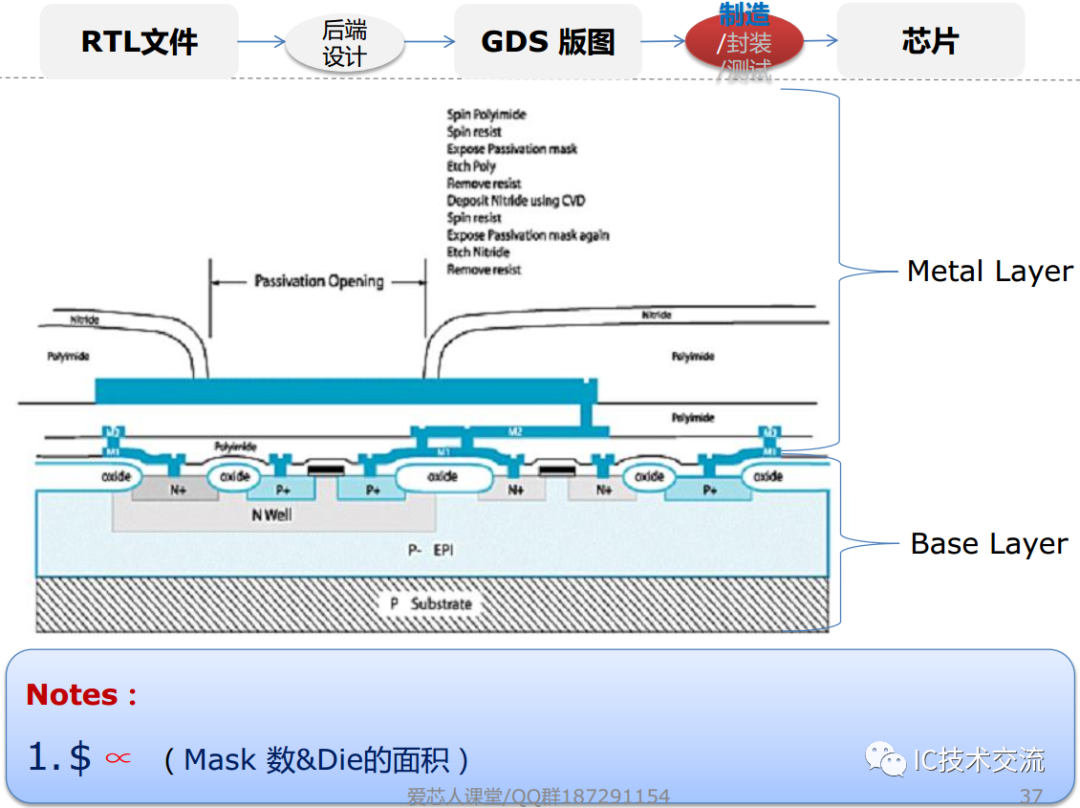

真实的芯片结构如下图所示。最底层是晶体管结构,晶体管接口和连接线的接触部分叫Contact。Contact上面是Metal金属层,金属层就是连接线,密密麻麻的晶体管很多,因此连线分了好几层才能走通,一层的连接线要穿到其它层就需要打过孔(Via),就像搭积木一样实现整个电路。每层连线之间都插有Isolator隔离。

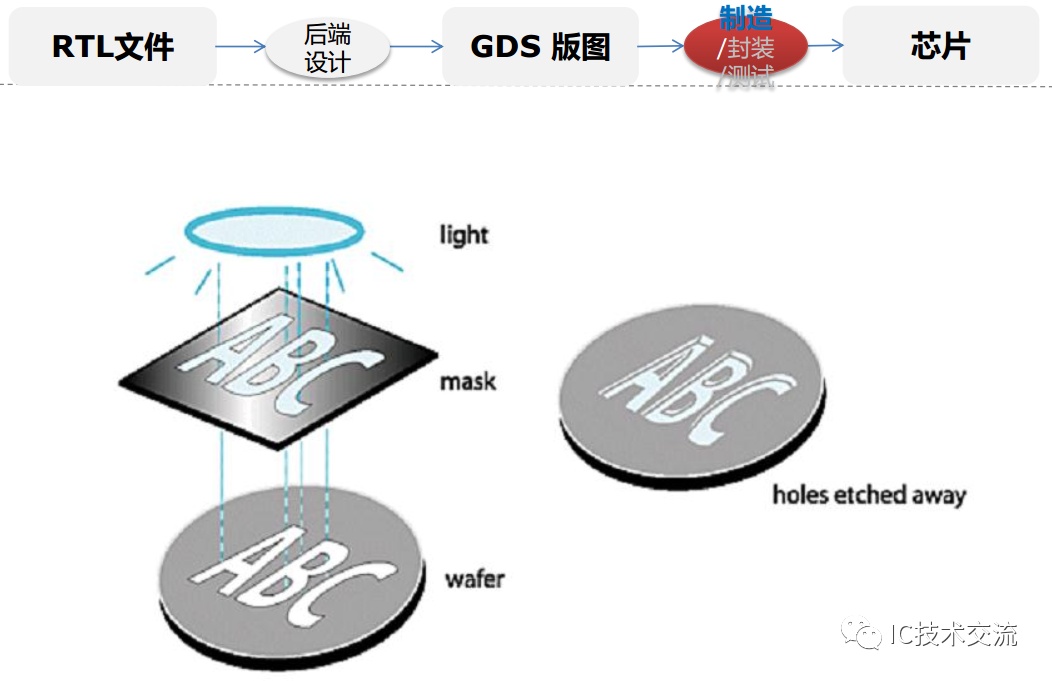

至于电路的具体制作过程如下所示。特殊频谱的光可以蚀刻电路,通过掩膜(mask),照射在wafer上,wafer涂有光刻胶,被照射的地方被腐蚀,剩下的部分形成电路。

流片成本很高,绝大部分是Mask(掩膜)的费用,Die面积XMask数就是主要的流片成本。

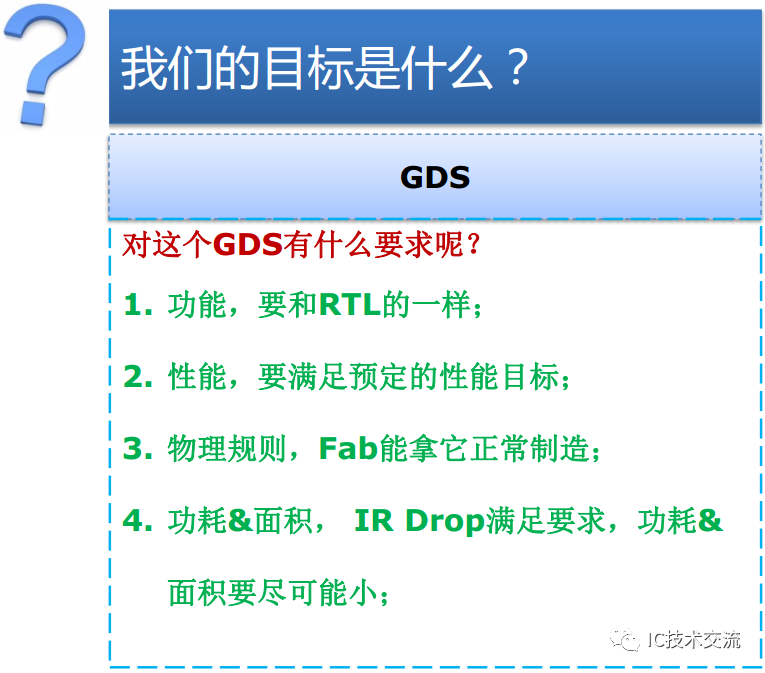

从RTL到GDS版图,要遵守以下要求,符合要求的GDS才能拿去流片

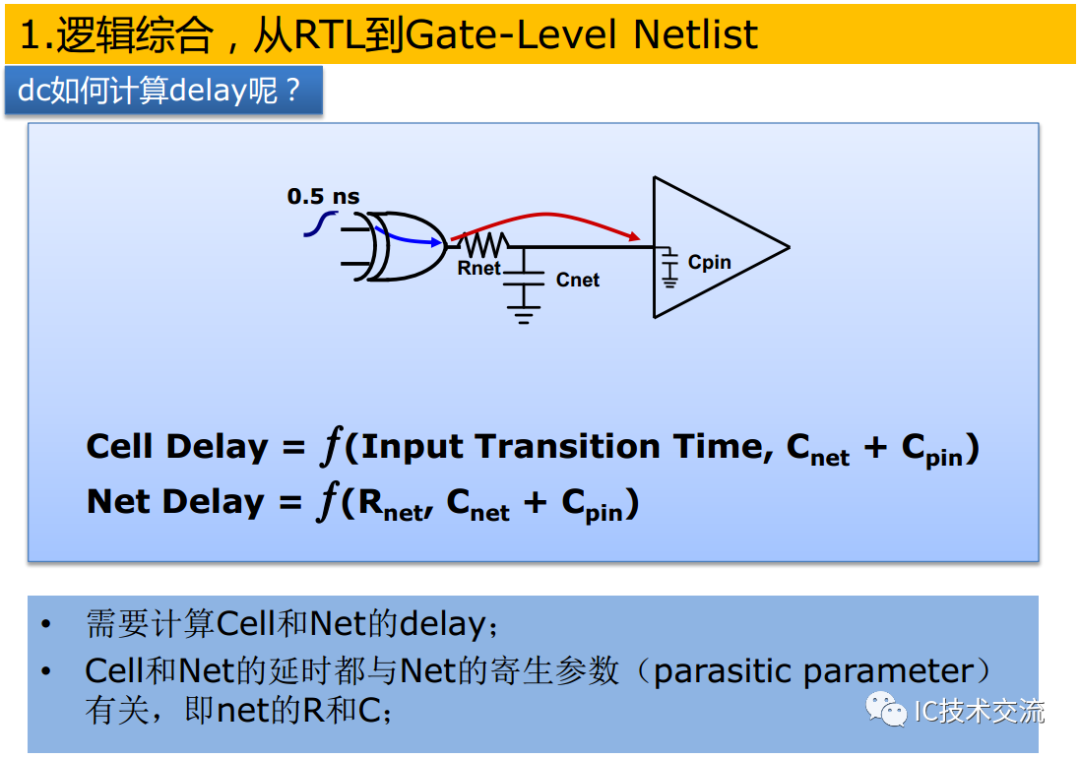

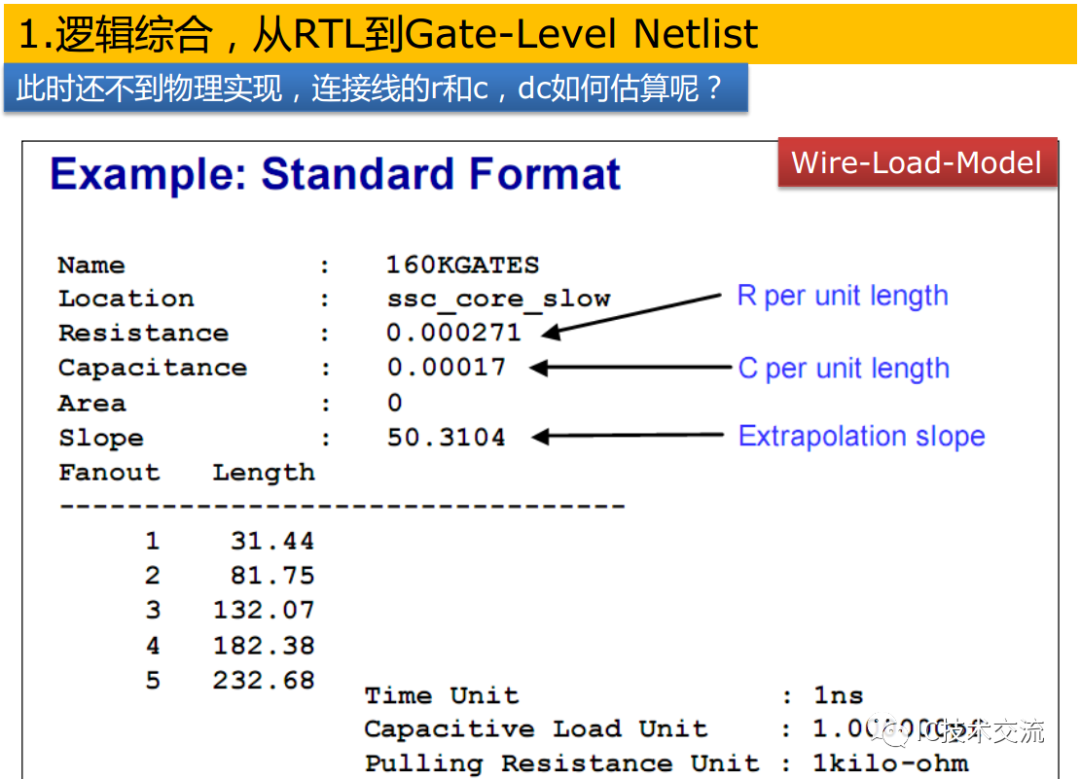

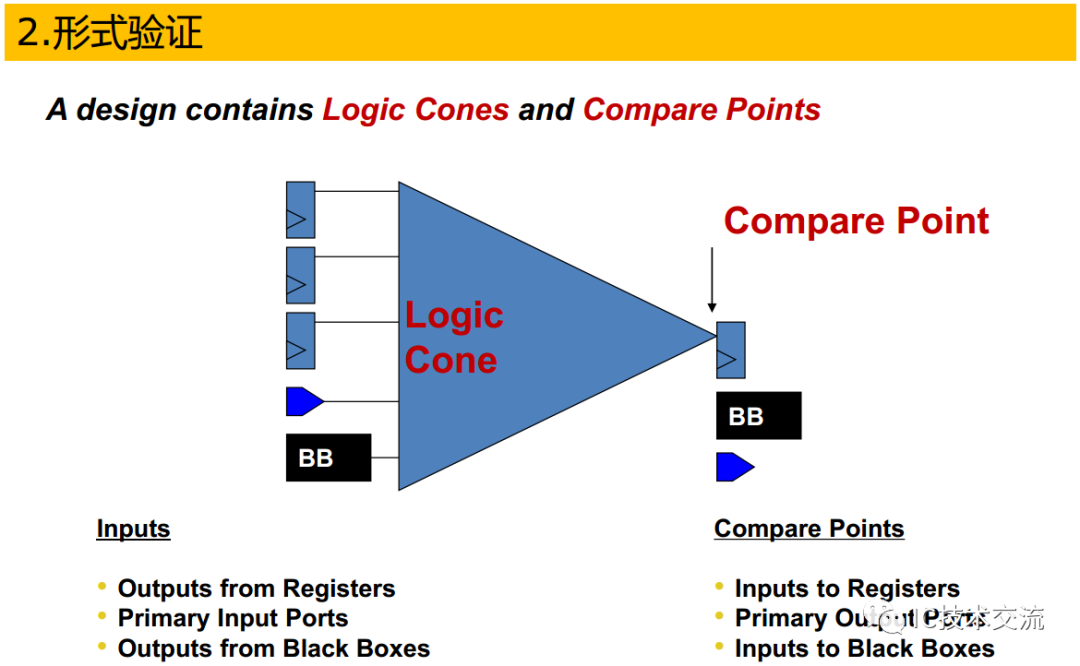

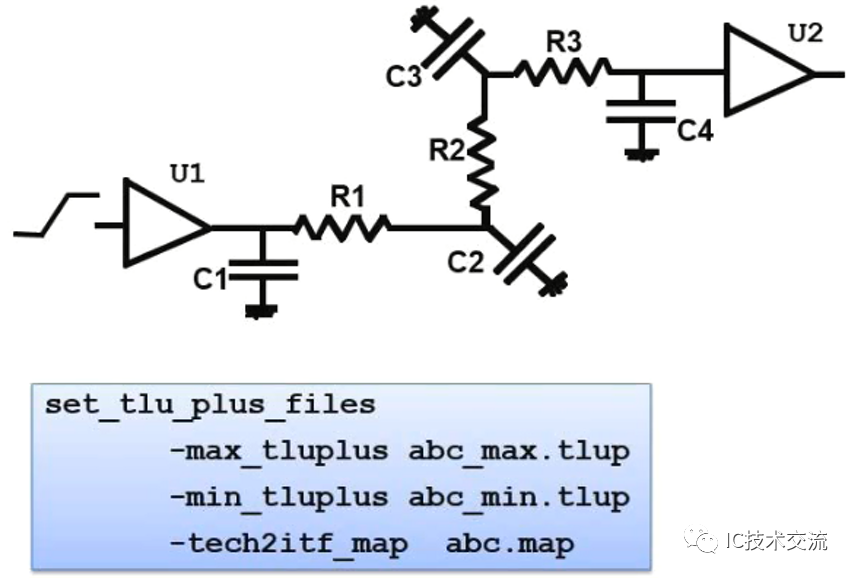

后端第一步是将RTL+SDC约束转换为网表,该步骤通过综合实现。通常工具会先将RTL转换为GTECH格式,然后再将GTECH转换为工艺库中的标准单元。整体来看是分两步走。转换为门级网表的过程中,综合工具会对RTL进行修改和优化,这些修改记录保存在svf文件。svf文件在后面的FM形式验证中会被使用。转换后的Netlist要满足设置的约束(包括时序,面积,功耗)。此外逻辑综合要满足sdc约束下的setup timing,不需要理会hold timing。常用的工具有synopsys的Design Compiler和cadence的RTL Compiler。逻辑综合涉及时序问题,延迟计算使用线负载模型(RC寄生参数)因为综合还没有涉及到布局布线,因此timing通常是不准的。下图给出了delay延迟的计算。

线延迟的计算通过长度衡量,长度越长RC值越大,扇出能力越弱。综合工具吐出Netlist网表后,需要进行FM形式验证,比对RTL和网表在功能上是否等价,常用的工具有synopsys的formality(fm)和Cadence的Conforml(lec)

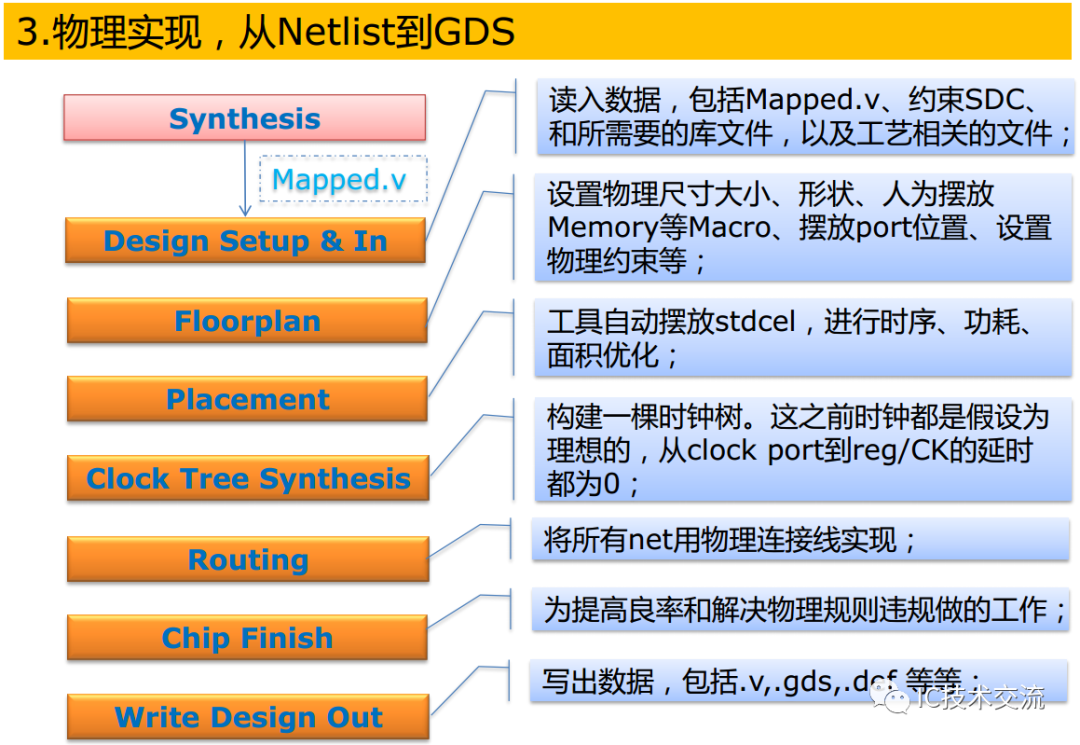

如果FM通过了,那么下一步进行物理实现:从Netlist到GDS。通常需要经过以下步骤:

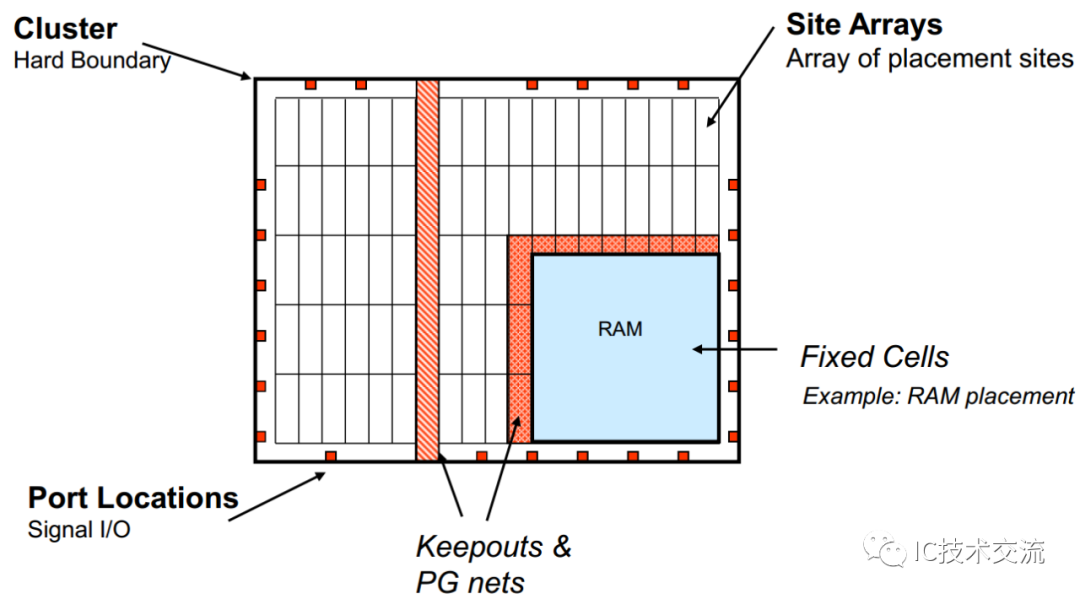

综合之后网表和约束已经有了,下一步进行ICC布局布线。Design Setup & In步骤中读入相关的网表、SDC和所需的工艺库文件。Floorplan步骤设置尺寸大小,摆放port位置,设置物理约束。Placement步骤中由工具自动摆放stdcel,进行时序、功耗、面积优化。Clock Tree Synthesis构建时钟树,这之前时钟都是假设为理想的,从clock port到reg/CK的延时都为0。对于时序分析而言,时钟树长出来之前所有的Timing问题其实都不准的,hold无需关注,setup需留有余量,因为布局布线的影响,时序会再次变化。Routing步骤中将所有net用物理连接线实现。Chip Finish步骤中为提高良率和解决物理规则违规对芯片做一些特殊处理。Write Design Out将所需的文件导出。

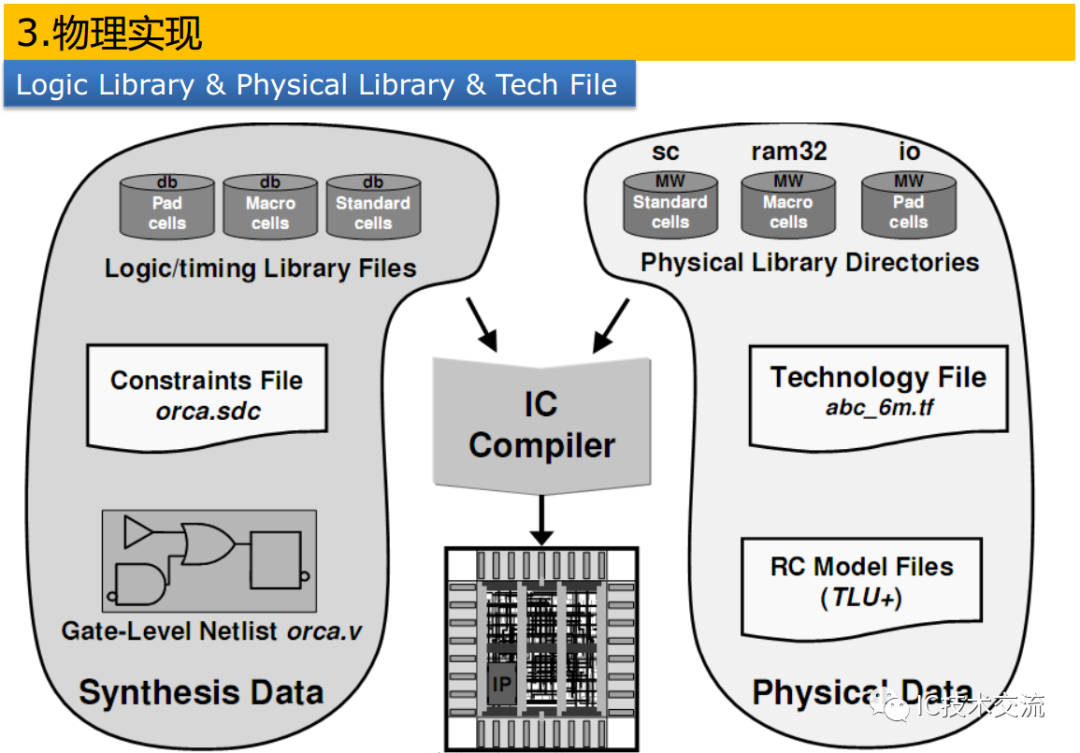

上图中给出ICC执行所需的两类文件:

1、一类是DC综合时的文件,包括library的db文件、sdc约束文件、综合后的网表文件;

2、一类是物理数据文件,包括library中db文件对应的Milkyway文件,技术文件(abc_6m.tf),RC模型文件(TLU+)用于提取寄生参数计算线延迟。

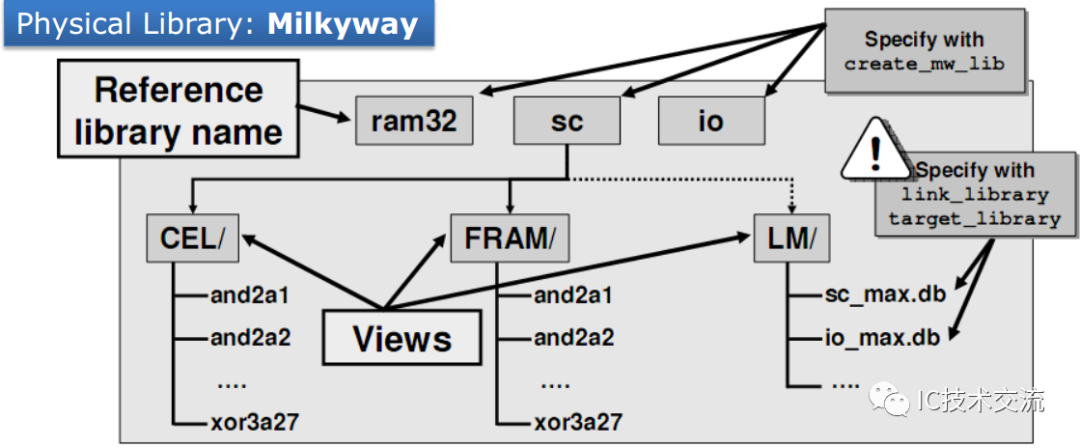

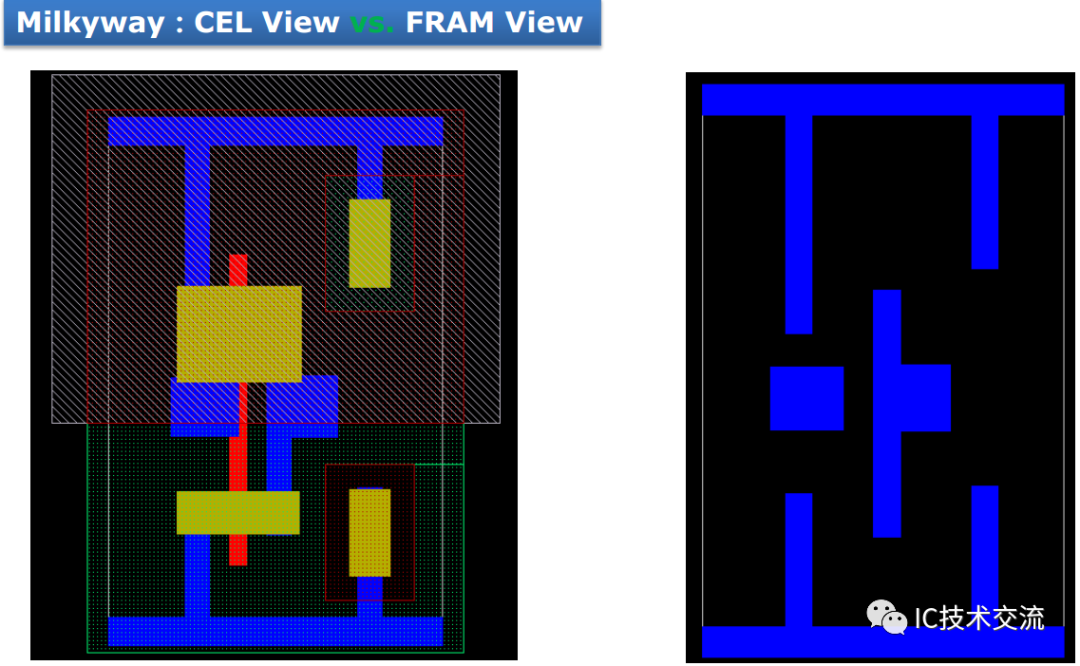

这里我们首先说下物理库,ICC中所有物理库都以Milkway的格式存在包括stdcell、memory等物理库,也包括设计本身。以stdcell为例,一般包含三类:CEL、FRAM和LM。其中CEL和FRAM是View信息,CEL包括所有的物理信息,FRAM只包含pin的位置和形状以及routing blocage。PnR过程中,ICC只会把FRAM View读进memory,CEL View数据量太大,CEL View只在最后写GDS时用。Routing blockage是绕线阻碍物,就是给某些金属加上blockage属性,让工具走线时不通过该区域,避免route时把连线伸进去,造成短路;

上图左侧为INV的CEL View,右侧为INV的FRAM View。从图中可看出FRAM中信息量确实很少。

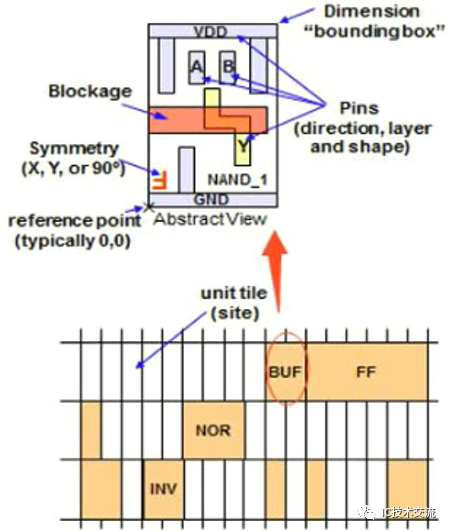

一个FRAM View中包含Pin的方向、位于哪一层、形状。左下角是cell的参考点,坐标为(0,0)自动布局时会被使用。还有中间的Blockage区域(避免走线)。通常一个cell放在Row中的一个site上,cell的高度和Row的高度是相同的,这些都在tf文件中有定义。VDD位于顶层,GND位于最下面,这些和row的线对齐。

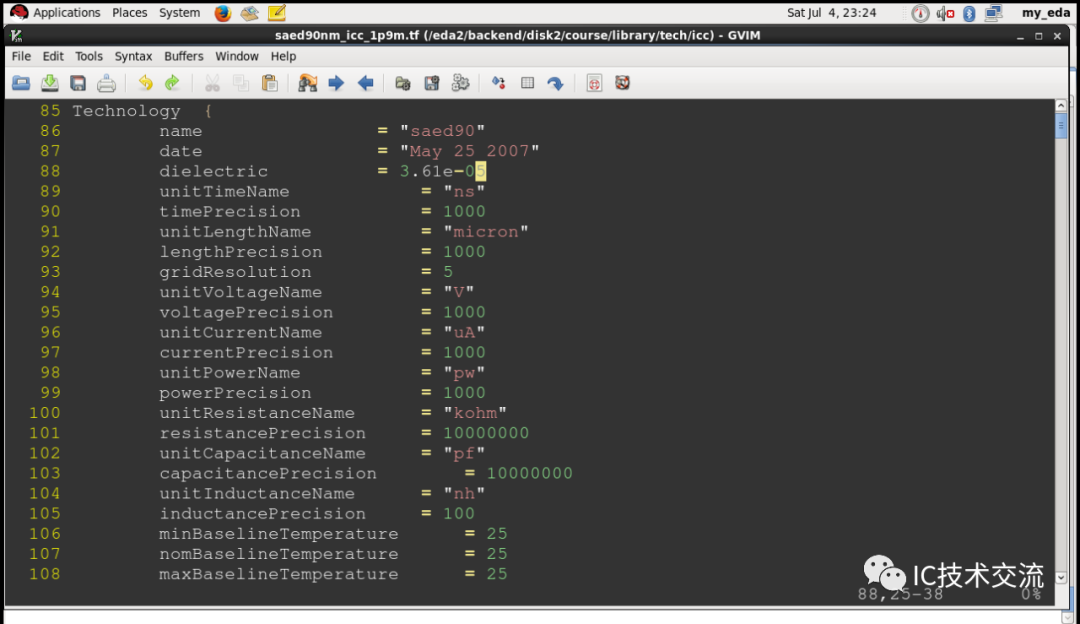

tf技术文件包括以下信息:

1、layer/via的数量和名字

2、每层layer的物理和电参数

3、每层layer的设计规则(最小线宽,线间距)

4、每个cell的单位和精度

5、每层的layer的显示颜色和模式

技术文件内容如上图所示,里面定义了很多物理参数。

至于tlu+文件用于对线负载模型建模,ICC的RC估算比DC精确的多,已经可以表达真实的线延迟。后端工具基于此可计算wire的寄生参数:包括电阻、电容、耦合电容。

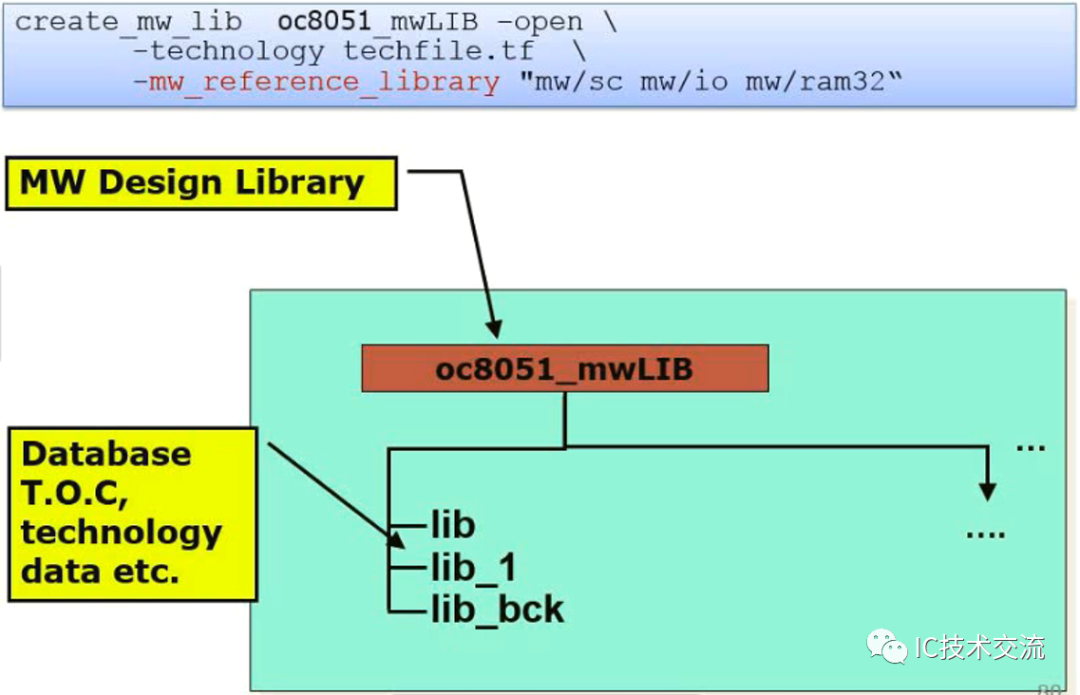

在ICC处理的第一步中就是创建milkway_lib,它会创建名为oc8051_mwLIB文件夹。并将技术文件和mw文件导入其中。

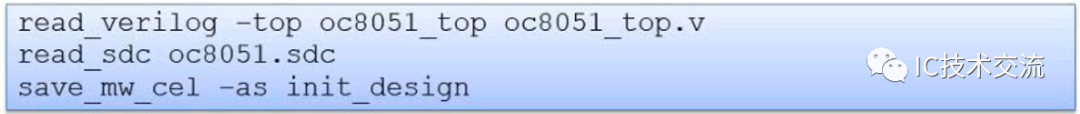

接下来读入网表文件和约束文件,同时保存CEL View数据

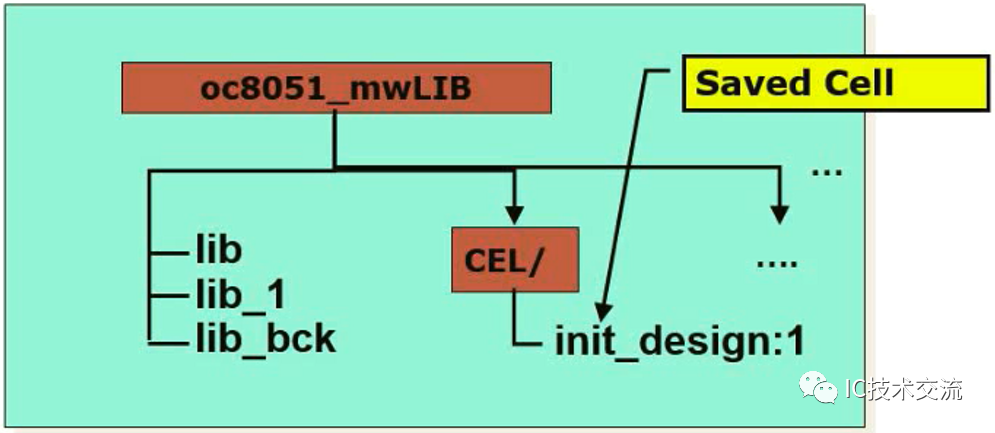

此时原有文件夹下会新建CEL文件,并将mw数据保存为init_design库文件。在Design Setup & In阶段,读入所有文件后,此时并没有floorplan操作,所有cell堆积在左下角。

floorplan步骤:先摆放大的mcro cell,然后摆放stdcell,这期间需要固定IO位置。对于最底层晶体管的供电而言,M1或M2与Row平行的会放置metal,依次与cell的VDD和VSS相连,在M6或M7放置供电网,高层次的layer通过via与底层次的Layer相连,从而搭建整体的电源系统。这里需要说明一点,如果M1是横向的,那么M2必须是纵向的,以此减少线干扰,相隔两层的metal必须正交,不能平行(与硬件PCB多层板布线很相似)。

floorplan本质是包含三方面:PPA(功耗性能面积),这三方面需要折中处理。这之后就到了Placement阶段,工具会自动将每个cell放入site中。

在Route之前,ICC做place_opt进行优化时用Virtual Route估计连接线的长度和形状,以此根据TLU+模型估计RC参数。事实上,在后面的CTS阶段,由于没有route,所以也通过同样的方法估计RCPlacement阶段,需要满足sdc约束下的setup timing,所以完成place后,要分析Timing。

-

IC设计

+关注

关注

38文章

1369浏览量

107907 -

晶体管

+关注

关注

78文章

10250浏览量

146269 -

晶圆厂

+关注

关注

7文章

643浏览量

38859

原文标题:IC后端概述(上)

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

IC前端和后端设计的区别

数字IC后端(CAD)

ADM1186 OUT1~OUT4可以直接去控制后端的Power IC Enable Pin吗?

数字IC后端设计介绍,写给哪些想转IC后端的人!

后端集成电路SAA7158电子资料

后端系统,后端系统是什么意思

IC前端设计(逻辑设计)和后端设计(物理设计)的详细解析

IC后端概述(上)

IC后端概述(上)

评论